由于3D結構的復雜性,可能會發(fā)生多種錯誤。特別是在高容量系統(tǒng)中,這些問題需要NAND閃存控制器和先進的糾錯算法。

在 NAND 工藝開發(fā)中,2D NAND 在大約 10 納米處達到了極限。由于平面NAND技術的浮動門內部的電子較少,因此3D NAND結構正在成為大容量存儲系統(tǒng)的主流。

3D NAND結構將平面浮動門旋轉90度,并將許多層堆疊在一起以增加容量。3D NAND市場的大多數參與者 - 包括三星,東芝/ WD,美光,海力士和英特爾 - 現在批量生產64層三電平單元(TLC)NAND,芯片容量為256 Gb。

利用 ECC 克服 3D NAND 的復雜性

由于3D結構的復雜性,可能會發(fā)生多種錯誤。這些問題包括逐層讀取干擾、寫入干擾和數據保留問題。特別是在高容量系統(tǒng)中,所有這些問題至少需要NAND閃存控制器,更具體地說,需要先進的糾錯算法。

遺憾的是,多級單元 (MLC) NAND 技術中使用的傳統(tǒng)博世-喬杜里-霍昆海姆 (BCH) 糾錯碼 (ECC) 算法對于 3D TLC NAND 來說是不夠的。需要更強大的低密度奇偶校驗 (LPDC) ECC 算法。

LPDC ECC 使用硬件和軟件機制來糾正位錯誤。硬件機制可以糾正每 1 KB 超過 120 位的錯誤,而軟件機制使用更復雜的糾錯方法來解決幾乎兩倍的錯誤。但是,盡管它們更強大,但基于軟件的ECC操作需要更長的時間來執(zhí)行。

除了硬件和軟件校正機制外,3D NAND還需要一種防止大規(guī)模數據丟失的方法。這意味著必須在NAND控制器內部實現RAID功能,該功能可以解決LPDC ECC算法無法糾正的錯誤,例如整頁錯誤或多個數據頁的損壞。當然,此RAID功能需要一些額外的內存用于奇偶校驗和額外的計算資源,但為了確保SSD上的數據是安全的,這是非常值得的。

3D TLC NAND 器件的安全數據序列

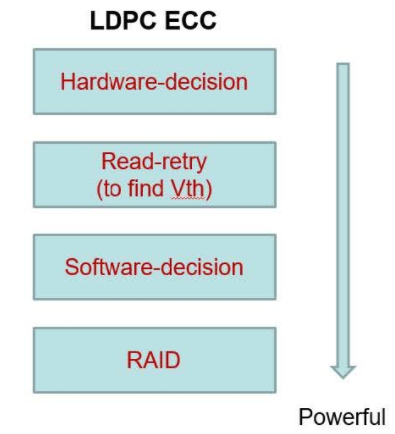

圖 1 顯示了固態(tài)硬盤控制器的 LDPC ECC 序列,包括上述 RAID 功能。在步驟中,SSD 控制器必須實現的 ECC 序列如下所示:

首先使用硬件機制(硬件決策)

如果步驟 1 失敗,請嘗試實現不同的 Vth(NAND 狀態(tài)的電壓電平)以獲得最低的誤碼率,也稱為讀移或讀取重試

接下來,實施軟件機制(軟件決策)來糾正錯誤

如果所有其他方法都失敗了,請使用內部 RAID 功能

圖 1.在 3D TLC NAND 控制器上實現此 ECC 方案提供了一個糾正位錯誤的過程,該錯誤從資源密集程度最低變?yōu)楣δ茏顝姶蟆?/p>

更可靠的 3D 薄型液晶顯示器

3D TLC NAND代表存儲介質中的拐點,提供更低的每比特成本和更少的占用空間。然而,為了使市場擴展到嵌入式行業(yè),該技術需要為位糾錯提供一套可持續(xù)的、可擴展的解決方案。

通過實現上述LPDC ECC序列,該序列以NAND控制器上強大的RAID功能終止,UDInfo認為,對于未來基于3D TLC的NAND設備,可以保證SSD質量和數據完整性。

審核編輯:郭婷

-

顯示器

+關注

關注

21文章

5071瀏覽量

141657 -

控制器

+關注

關注

114文章

17067瀏覽量

183761 -

NAND

+關注

關注

16文章

1721瀏覽量

138014

發(fā)布評論請先 登錄

TPS65735 用于主動快門 3D 眼鏡的電源管理 IC數據手冊

一種以圖像為中心的3D感知模型BIP3D

一種3D交聯導電粘結劑用于硅負極Angew

SD NAND、SPI NAND 和 Raw NAND 的定義與比較

解決方案 3D 視覺機器人賦能汽車制造新征程

【半導體存儲】關于NAND Flash的一些小知識

DMD芯片在3D打印中的創(chuàng)新應用

美光第九代3D TLC NAND閃存技術的SSD產品開始出貨

一種用于3D TLC NAND的彈性糾錯方案

一種用于3D TLC NAND的彈性糾錯方案

評論