聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1359瀏覽量

105753 -

eda

+關(guān)注

關(guān)注

71文章

2924瀏覽量

177935 -

3DIC

+關(guān)注

關(guān)注

3文章

86瀏覽量

19785 -

chiplet

+關(guān)注

關(guān)注

6文章

459瀏覽量

12994

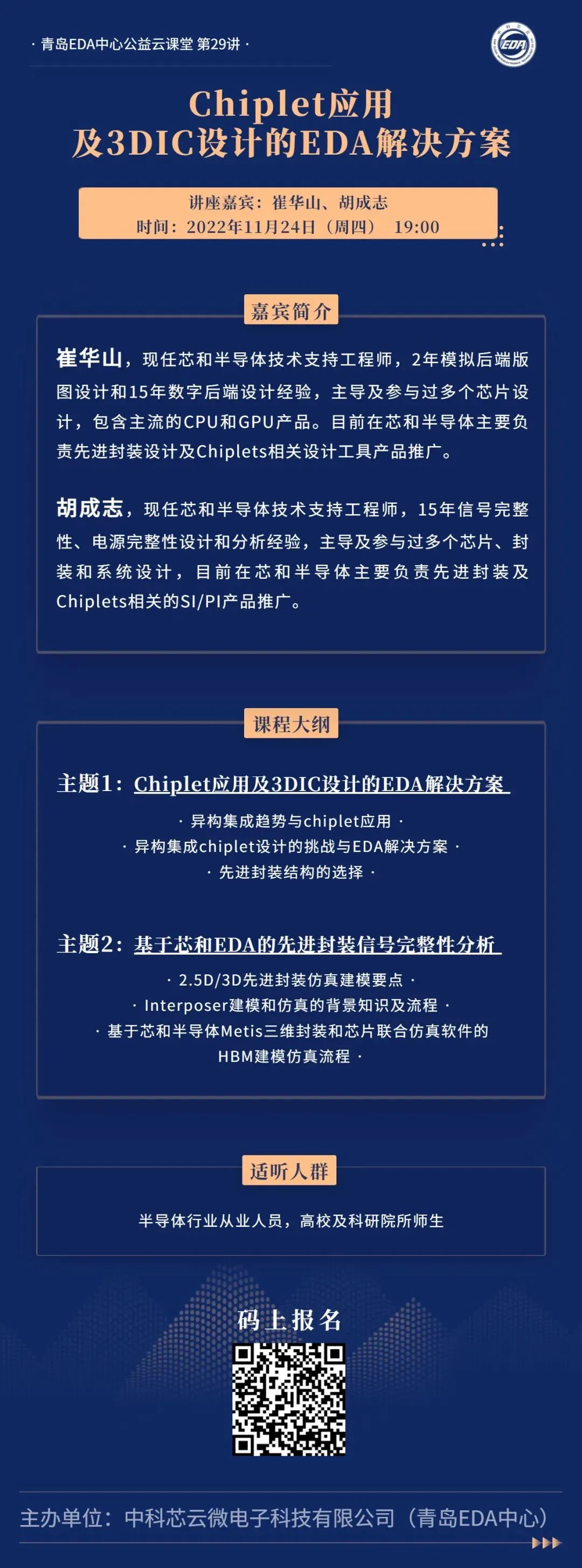

原文標(biāo)題:【明日開課】公益云課堂第29講 | Chiplet應(yīng)用及3DIC設(shè)計的EDA解決方案

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

AI、Chiplet EDA需求強勁!國產(chǎn)EDA跑步進入,突破3%市場份額有大招

EDA的市場份額是1%,到了2023年國產(chǎn)EDA市場占有率達到3%。而華大九天是國內(nèi)唯一躋身全球前十的EDA公司,擁有特定領(lǐng)域全流程,在局部領(lǐng)域技術(shù)領(lǐng)先。”8月16日,在2024中國(

西門子EDA產(chǎn)品組合新增兩大解決方案

西門子數(shù)字化工業(yè)軟件日前宣布為其電子設(shè)計自動化 (EDA) 產(chǎn)品組合新增兩大解決方案,助力半導(dǎo)體設(shè)計團隊攻克 2.5D/3D 集成電路 (IC) 設(shè)計與制造的復(fù)雜挑戰(zhàn)。

適用于先進3D IC封裝完整的裸片到系統(tǒng)熱管理解決方案

摘要半導(dǎo)體行業(yè)向復(fù)雜的2.5D和3DIC封裝快速發(fā)展,帶來了極嚴(yán)峻的熱管理挑戰(zhàn),這需要從裸片層級到系統(tǒng)層級分析的復(fù)雜解決方案。西門子通過一套集成工具和方法來應(yīng)對這些多方面的挑戰(zhàn),這些工具和方法結(jié)合了

行芯科技亮相2025世界半導(dǎo)體博覽會

”的簽核技術(shù)也迎來新的挑戰(zhàn)與機遇,會議上市場代表發(fā)表《面向3DIC的Signoff挑戰(zhàn)與行芯創(chuàng)新策略》主題演講,展示自研3DIC Signoff全流程解決方案,引起行業(yè)高度關(guān)注。

行芯科技揭示先進工藝3DIC Signoff破局之道

在當(dāng)下3DIC技術(shù)作為提升芯片性能和集成度的重要路徑,正面臨著諸多挑戰(zhàn),尤其是Signoff環(huán)節(jié)的復(fù)雜性問題尤為突出。此前,6月6日至8日,由中國科學(xué)院空天信息創(chuàng)新研究院主辦的“第四屆電子與信息前沿

Chiplet與先進封裝設(shè)計中EDA工具面臨的挑戰(zhàn)

Chiplet和先進封裝通常是互為補充的。Chiplet技術(shù)使得復(fù)雜芯片可以通過多個相對較小的模塊來實現(xiàn),而先進封裝則提供了一種高效的方式來將這些模塊集成到一個封裝中。

淺談Chiplet與先進封裝

隨著半導(dǎo)體行業(yè)的技術(shù)進步,尤其是摩爾定律的放緩,芯片設(shè)計和制造商們逐漸轉(zhuǎn)向了更為靈活的解決方案,其中“Chiplet”和“先進封裝”成為了熱門的概念。

STCO發(fā)展促使EDA工具考慮更多系統(tǒng)級因素

迅速發(fā)展,對芯片技術(shù)提出了更高的要求,傳統(tǒng)的SoC在應(yīng)對這些需求時已顯得力不從心。Chiplet技術(shù)作為一種新興的解決方案,通過將不同功能模塊集成在一起,提供了更高效、更靈活的芯片設(shè)計方式。 ? 在Chiplet設(shè)計中,

英諾達為本土客戶提供優(yōu)質(zhì)EDA解決方案

英諾達(成都)電子科技有限公司成立于2020年,是一家由行業(yè)頂尖資深人士創(chuàng)立的本土EDA企業(yè),公司堅持以客戶需求為導(dǎo)向,幫助客戶實現(xiàn)價值最大化,為中國半導(dǎo)體產(chǎn)業(yè)提供卓越的EDA解決方案。

eda的常見誤區(qū)和解決方案

,導(dǎo)致分析結(jié)果受到臟數(shù)據(jù)的影響。 解決方案: 在進行EDA之前,應(yīng)該先進行數(shù)據(jù)清洗,包括處理缺失值、異常值和重復(fù)值。可以使用數(shù)據(jù)清洗工具或編寫腳本來自動化這一過程。 誤區(qū)2:過度依賴單一圖表 常見誤區(qū): 僅使用柱狀圖或散點圖來探索數(shù)據(jù)

芯和半導(dǎo)體邀您相約IIC Shenzhen 2024峰會

芯和半導(dǎo)體將于11月5-6日參加在深圳福田會展中心7號館舉辦的國際集成電路展覽會暨研討會(IIC Shenzhen 2024),并在DesignCon專區(qū)中展示其3DIC Chiplet先進封裝一體化EDA設(shè)計平臺的最新

UCIe規(guī)范引領(lǐng)Chiplet技術(shù)革新,新思科技發(fā)布40G UCIe IP解決方案

了近3倍,算力提升了6倍,這背后離不開Chiplet(小芯片)設(shè)計方案的引入。Chiplet技術(shù),作為“后摩爾定律時代”提升芯片性能的關(guān)鍵解決方案

創(chuàng)新型Chiplet異構(gòu)集成模式,為不同場景提供低成本、高靈活解決方案

顆是原生支持Transformer全系算子的AI Chiplet“大熊星座”。 ? Chiplet 集成模式提供低成本、高靈活解決方案 ? 隨著摩爾定律逐步放緩以及先進封裝等技術(shù)的發(fā)展,高性能計算芯片的迭代無需再僅僅圍繞摩爾定律

新思科技7月份行業(yè)事件

新思科技宣布推出面向英特爾代工EMIB先進封裝技術(shù)的可量產(chǎn)多裸晶芯片設(shè)計參考流程,該流程采用了Synopsys.ai EDA全面解決方案和新思科技IP。此外,新思科技3DSO.ai與新思科技3

西門子EDA創(chuàng)新解決方案確保Chiplet設(shè)計的成功應(yīng)用

這些要求,因此,多芯片集成(如Chiplet設(shè)計)成為了一種新的趨勢。 ? Chiplet設(shè)計 帶來的挑戰(zhàn)及行業(yè)解決方案 Chiplet設(shè)計帶來了許多優(yōu)勢,同時也帶來了眾多新的挑戰(zhàn)。這

Chiplet應(yīng)用及3DIC設(shè)計的EDA解決方案

Chiplet應(yīng)用及3DIC設(shè)計的EDA解決方案

評論