一個新的轉換器接口正在穩步發展,并有望成為未來轉換器的首選協議。這個新接口JESD204最初是在幾年前推出的,但經過了修訂,使其成為更具吸引力和效率的轉換器接口。隨著轉換器分辨率和速度的提高,對更高效接口的需求也在增長。JESD204接口帶來了這種效率,在速度、尺寸和成本方面,與互補金屬氧化物半導體(CMOS)和低壓差分信號(LVDS)前代產品相比具有多項優勢。采用JESD204的設計具有更快的接口優勢,可以跟上轉換器更快的采樣速率。此外,引腳數量減少,導致封裝尺寸更小,走線路徑數量更少,從而使電路板設計更加容易,并降低整體系統成本。該標準還易于擴展,因此可以進行調整以滿足未來的需求。該標準所經歷的兩次修訂已經證明了這一點。JESD204標準自2006年推出以來已經進行了兩次修訂,目前處于修訂版B。隨著越來越多的轉換器供應商和用戶以及FPGA制造商采用該標準,該標準已經得到改進,并添加了新功能,從而提高了效率和易于實施。該標準適用于模數轉換器(ADC)和數模轉換器(DAC),主要用作FPGA的通用接口(但也可以與ASIC一起使用)。

JESD204—這是什么?

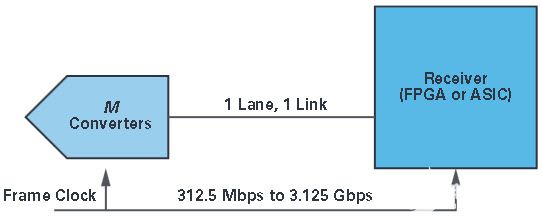

2006年4月,JESD204的原始版本發布。該標準描述了轉換器和接收器之間的多千兆串行數據鏈路,通常是FPGA或ASIC等器件。在JESD204的原始版本中,串行數據鏈路定義為一個或多個轉換器與接收器之間的單個串行通道。圖 1 提供了圖形表示。所示通道是M個轉換器和接收器之間的物理接口,由利用電流模式邏輯(CML)驅動器和接收器的差分互連對組成。所示鏈路是在轉換器和接收器之間建立的串行數據鏈路。幀時鐘路由到轉換器和接收器,并為器件之間的JESD204鏈路提供時鐘。

圖1.JESD204原始標準。

通道數據速率定義為每秒 312.5 兆比特 (Mbps) 和每秒 3.125 千兆比特 (Gbps),源阻抗和負載阻抗均定義為 100 Ω ±20%。差分電壓電平定義為標稱值為800 mV峰峰值,共模電壓電平范圍為0.72 V至1.23 V。該鏈路采用包含嵌入式時鐘的8b/10b編碼,消除了路由額外時鐘線的必要性,也消除了在高數據速率下將附加時鐘信號與傳輸數據對齊的相關復雜性。很明顯,隨著JESD204標準開始普及,該標準需要修訂,以支持具有多個轉換器的多個對齊串行通道,以適應轉換器速度和分辨率的提高。

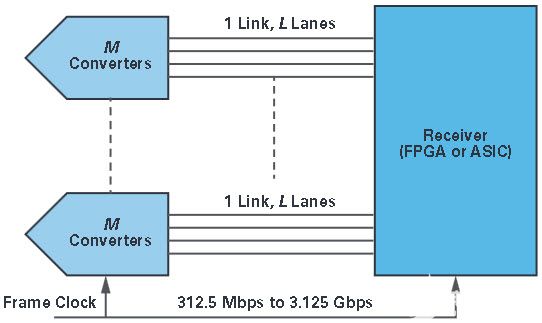

這一認識導致了JESD204標準的第一次修訂,即JESD204A。該標準的修訂增加了支持具有多個轉換器的多個對齊串行通道的能力。支持312.5 Mbps至3.125 Gbps的通道數據速率保持不變,幀時鐘和電氣接口規格也保持不變。通過提高標準支持多個對齊串行通道的功能,具有高采樣速率和高分辨率的轉換器能夠滿足3.125 Gbps的最大支持數據速率。 圖2顯示了JESD204A修訂版中為支持多通道而添加的附加功能的圖形表示。

圖2.第一次修訂—JESD204A。

盡管最初的JESD204標準和修訂后的JESD204A標準都比傳統接口具有更高的性能,但它們仍然缺乏關鍵要素。這個缺失的元素是鏈路上序列化數據中的確定性延遲。處理轉換器時,重要的是要知道采樣信號與其數字表示之間的時序關系,以便在接收到信號后在模擬域中正確重建采樣信號(當然,這種情況對于ADC來說也是如此,DAC的情況類似)。這種時序關系受轉換器延遲的影響,對于ADC而言,延遲定義為輸入信號采樣邊沿時刻與其數字表示出現在轉換器輸出端之間的時鐘周期數。類似地,在DAC中,延遲定義為從數字信號時鐘進入DAC到模擬輸出開始變化之間的時鐘周期數。在JESD204和JESD204A標準中,沒有定義功能來確定轉換器及其串行數字輸入/輸出的延遲。此外,轉換器的速度和分辨率都在不斷提高。這些因素導致了該標準的第二次修訂版JESD204B的引入。

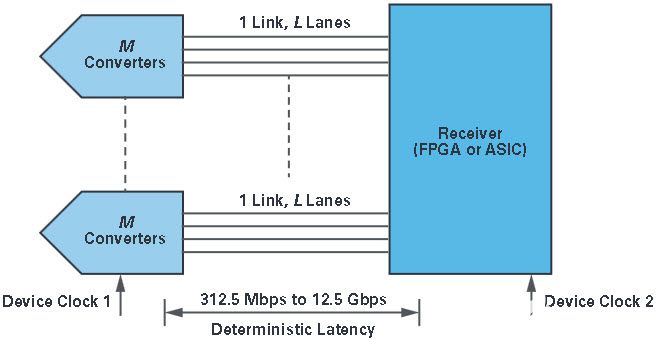

2011年7月,該標準的第二次也是當前修訂版JESD204B發布。修訂后的標準的關鍵組成部分之一是增加了實現確定性延遲的規定。此外,支持的數據速率被推高到12.5 Gbps,細分為不同的設備速度等級。此標準修訂版要求從使用幀時鐘作為主時鐘源過渡到使用設備時鐘作為主時鐘源。圖3顯示了JESD204B版本添加的其他功能。

圖3.第二個(當前)修訂版 — JESD204B。

在JESD204標準的前兩個版本中,沒有定義任何規定來確保通過接口的確定性延遲。JESD204B修訂版通過提供一種機制來解決這個問題,以確保從上電周期到上電周期以及跨鏈路重新同步事件,延遲應該是可重復和確定的。實現此目的的一種方法是,通過使用稱為SYNC~的輸入信號,在明確定義的時刻同時在所有通道上啟動轉換器中的初始通道對齊序列。另一種實現方式是使用SYSREF信號,這是JESD204B新定義的信號。SYSREF信號充當主定時參考,并對齊來自器件時鐘的所有內部分頻器以及每個發射器和接收器中的本地多幀時鐘。這有助于確保通過系統的確定性延遲。JESD204B規范列出了三個器件子類:子類0——不支持確定性延遲;子類 1 - 使用 SYSREF 的確定性延遲;子類 2 — 使用 SYNC~ 的確定性延遲。子類0可以簡單地與JESD204A鏈路進行比較。子類 1 主要用于工作在 500 MSPS 或高于 500 MSPS 的轉換器,而子類 2 主要用于工作在 500 MSPS 以下的轉換器。

除了確定性延遲外,JESD204B版本還將支持的通道數據速率提高到12.5 Gbps,并將設備分為三種不同的速度等級。對于定義為 100 Ω ±20% 的所有三個速度等級,源阻抗和負載阻抗相同。第一個速度等級與JESD204和JESD204A版本的通道數據速率一致,并定義了高達3.125 Gbps的通道數據速率的電氣接口。JESD204B中的第二個速度等級定義了高達6.375 Gbps的通道數據速率的電氣接口。該速度等級將最小差分電壓電平從第一個速度等級的峰峰值降至400 mV。JESD204B中的第三級速度定義了高達12.5 Gbps的通道數據速率的電氣接口。該速度等級將電氣接口所需的最小差分電壓電平降低到360 mV峰峰值。隨著速度等級的通道數據速率增加,所需的最小差分電壓電平降低,通過降低驅動器所需的壓擺率,使物理實現更容易。

為了提供更大的靈活性,JESD204B版本從幀時鐘過渡到器件時鐘。以前,在JESD204和JESD204A修訂版中,幀時鐘是JESD204系統中的絕對時序參考。通常,轉換器的幀時鐘和采樣時鐘是相同的。這并沒有提供很大的靈活性,并且在嘗試將同一信號路由到多個設備并考慮不同路由路徑之間的任何偏差時,可能會導致系統設計中不必要的復雜性。在JESD204B中,器件時鐘是JESD204系統中每個元件的時序參考。每個轉換器和接收器都從時鐘發生器電路獲得各自的設備時鐘,該時鐘發生器電路負責從公共源生成所有設備時鐘。這為系統設計提供了更大的靈活性,但需要為給定設備指定幀時鐘和設備時鐘之間的關系。

JESD204—我們為什么要關注它?

就像LVDS幾年前開始取代CMOS成為轉換器數字接口的首選技術一樣,JESD204也有望在未來幾年走上類似的道路。雖然CMOS技術今天仍然徘徊,但它大多已被LVDS取代。轉換器的速度和分辨率以及對低功耗的渴望最終使CMOS和LVDS不足以滿足轉換器的需求。隨著CMOS輸出端數據速率的增加,瞬態電流也會增加,從而導致更高的功耗。雖然LVDS的電流和功耗保持相對平穩,但該接口具有可以支持的速度上限。

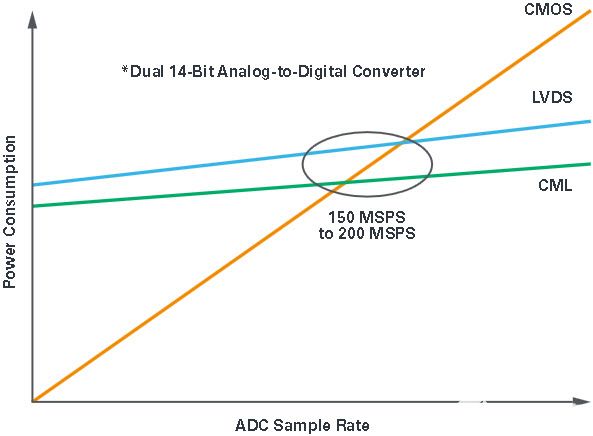

這是由于驅動程序架構以及必須全部同步到數據時鐘的大量數據線。圖4顯示了雙通道14位ADC的CMOS、LVDS和CML輸出的不同功耗要求。

圖4.CMOS、LVDS 和 CML 驅動器功耗比較。

在大約150 MSPS至200 MSPS和14位分辨率下,CML輸出驅動器在功耗方面開始變得更加高效。由于數據的序列化,CML具有以下優點:與LVDS和CMOS驅動器相比,每個給定分辨率所需的輸出對更少。為JESD204B接口指定的CML驅動器具有額外的優勢,因為該規范要求隨著采樣速率的增加和輸出線路速率的提高而降低峰峰值電壓電平。

相同的轉換器分辨率和采樣率所需的引腳數量也大大減少。表1顯示了使用具有不同通道數和位分辨率的200 MSPS轉換器的三種不同接口的引腳數。對于CMOS和LVDS輸出,數據假定每個通道的數據具有同步時鐘,對于使用CML輸出的JESD204B數據傳輸,最大數據速率為4.0 Gbps。使用CML驅動器發展到JESD204B的原因在查看此表并觀察到引腳數的大幅減少時變得顯而易見。

| 通道數 | 分辨率 | CMOS 引腳數 | LVDS 引腳數 (DDR) | CML 引腳數 (JESD204B) |

| 1 | 12 | 13 | 14 | 2 |

| 2 | 12 | 26 | 28 | 4 |

| 4 | 12 | 52 | 56 | 8 |

| 8 | 12 | 104 | 112 | 16 |

| 1 | 14 | 15 | 16 | 2 |

| 2 | 14 | 30 | 32 | 4 |

| 4 | 14 | 60 | 64 | 8 |

| 8 | 14 | 120 | 128 | 16 |

| 1 | 16 | 17 | 18 | 2 |

| 2 | 16 | 34 | 36 | 4 |

| 4 | 16 | 68 | 72 | 8 |

| 8 | 16 | 136 | 144 | 16 |

作為數據轉換器領域的市場領導者,ADI公司已經看到了將轉換器數字接口推向JEDEC定義的JESD204接口的趨勢。ADI公司從一開始就參與了該標準,當時發布了第一個JESD204規范。迄今為止,ADI公司已經發布了幾款具有JESD204和JESD204A兼容輸出的轉換器,目前正在開發輸出與JESD204B兼容的產品。AD9639是一款四通道、12位170 MSPS/210 MSPS ADC,具有JESD204接口。AD9644和AD9641分別是14位80 MSPS/155 MSPS雙通道和單通道ADC,具有JESD204A接口。從DAC的角度來看,最近發布的AD9128是一款雙通道16位1.25 GSPS DAC,具有JESD204A接口。有關ADI公司在JESD204方面工作的更多信息,請訪問 analog.com/jesd204。

隨著轉換器的速度和分辨率的提高,對更高效的數字接口的需求也在增加。業界通過JESD204串行數據接口開始實現這一點。接口規范不斷發展,為轉換器和FPGA(或ASIC)之間傳輸數據提供了一種更好、更快捷的方式。該接口經歷了兩次修訂,以改進其實現并滿足更高速度和更高分辨率轉換器帶來的日益增長的需求。展望轉換器數字接口的未來,很明顯,JESD204有望成為轉換器數字接口的行業選擇。每次修訂都滿足了改進其實施的要求,并允許標準不斷發展以滿足轉換器技術變化帶來的新要求。隨著系統設計變得越來越復雜,轉換器性能越來越高,JESD204標準應該能夠適應和發展,以繼續滿足必要的新設計要求。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8970瀏覽量

150890 -

半導體

+關注

關注

335文章

28666瀏覽量

233265 -

lvds

+關注

關注

2文章

1118瀏覽量

67135

發布評論請先 登錄

請問AD9683的引腳如何與zynq 7015芯片中的 JESD204 ip核端口對應相連?

JESD204 v5.2約束使用生成的dcp構建邏輯計時失敗

JESD204不允許生成比特流

JESD204接口簡介

JESD204標準解析

JESD204評估許可證問題

為什么JESD204內核不使用GTX通道綁定功能來對齊通道?

JESD204C標準值得注意的新特性

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對應相連?

工程師,為什么要關注JESD204?

采用JESD204標準的高速串行接口的應用

什么是JESD204_我們為什么要關注它?

JESD204——它是什么?

什么是JESD204,我們為什么要關注它

什么是JESD204,我們為什么要關注它

評論