自對準硅化物 (Self -Aligned Silicide) 工藝

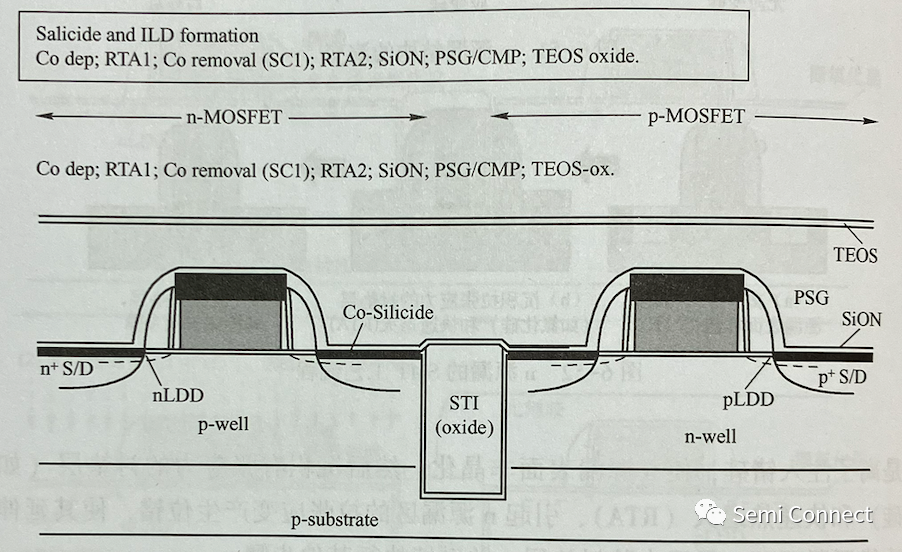

傳統(tǒng)的 CMOS 工藝(如32nm或更早的節(jié)點上)是基于氧化硅/多晶硅結構形成源漏的(即非 HKMG 和非應變源漏的工藝流程),因此稱為先柵 ( Gate-First)工藝。在有源區(qū)和多晶硅柵區(qū)多采用同時形成硅化物的自對準技術,如圖所示。

形成多晶硅柵和源漏之后,先用濕法或干法清除在有源區(qū) (AA)和多晶硅柵表面的氧化物,濺射一薄層(厚度范圍 10~20nm)金屬(鈷Co 或鎳Ni),緊接著進行第1次 RTA(溫度范圍為 400-550°C),與硅接觸的金屬發(fā)生反應形成金屬硅化物(Metal Silicide)。然后,用 SC1 溶劑去掉氧化硅上剩余的未參與反應的金屬,并進行第2 次RTA(溫度約為 700°C),在有源區(qū)和多晶硅柵區(qū)域上留有金屬硅化物,這一過程被稱為自對準硅化物工藝。之后,沉積氮氧硅和磷硅玻璃(PSG),并用CMP 進行平坦化,再沉積一層 CVD 氧化物(TEOS-ox)來密封 PSG,形成柵-金屬層間介質 (Inter-Layer Dielectrie, ILD)。

審核編輯 :李倩

-

CMOS

+關注

關注

58文章

5999瀏覽量

238278 -

多晶硅

+關注

關注

3文章

248瀏覽量

29712

原文標題:中段集成工藝(MOL Integration Flow)- 1

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

微流控芯片的封合工藝有哪些

自對準硅化物工藝詳解

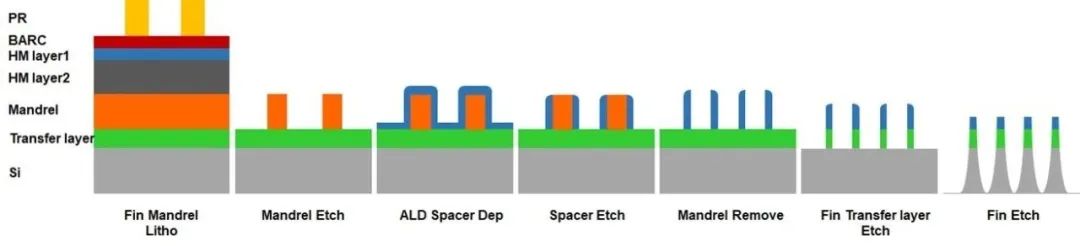

自對準雙重圖案化技術的優(yōu)勢與步驟

IBC技術新突破:基于物理氣相沉積(PVD)的自對準背接觸SABC太陽能電池開發(fā)

TRCX應用:顯示面板工藝裕量分析

DLP4500的內參數(shù)和畸變系數(shù)的相對準確的值是多少?

單晶圓系統(tǒng):多晶硅與氮化硅的沉積

Techwiz LCD 3D應用:基板未對準分析

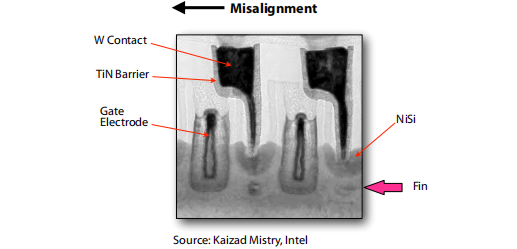

FinFet Process Flow—啞柵極的形成

TRCX:摻雜過程分析

Techwiz LCD:基板未對準分析

Poly方塊電阻的測試條件

CDCF5801A具有延遲控制和相位對準的時鐘乘法器數(shù)據(jù)表

自對準硅化物 (Self -Aligned Silicide) 工藝

自對準硅化物 (Self -Aligned Silicide) 工藝

評論