由于數字應用和數據處理的迅速興起,計算能力需求呈爆炸式增長。隨著越來越多地使用人工智能來應對我們這個時代的主要挑戰,例如氣候變化或糧食短缺,從現在開始,計算需求預計每六個月就會翻一番。為了以可持續的方式處理呈指數級增長的數據量,我們需要改進的高性能半導體技術。為了實現這一目標,我們需要同時應對五個挑戰。雖然世界上沒有一家公司可以單獨完成這一目標,但整個半導體生態系統的共同創新和協作將使摩爾定律得以延續:這是 imec 未來 15 至 20 年雄心勃勃的路線圖的關鍵信息。

一次五面墻

縮放墻:純光刻支持的縮放正在放緩。由于微芯片和晶體管的單個結構正在接近原子的大小,量子效應開始干擾微芯片的運行,這變得越來越困難。

內存墻:系統性能面臨內核和內存之間的數據路徑限制。事實上:內存帶寬跟不上處理器性能。我們每秒有更多的觸發器而不是每秒千兆字節。

功率墻:將功率引入芯片并從芯片封裝中提取熱量變得越來越具有挑戰性,因此我們必須開發改進的功率傳輸和冷卻概念。

可持續性墻:半導體設備的制造導致環境足跡不斷增加,包括溫室氣體和水、自然資源和電力消耗。

成本墻:顯然,芯片制造成本可能會隨著復雜性的增加以及設計和工藝開發成本的增加而激增。

拆墻

乍一看,戈登摩爾的預言看起來并不那么美好,他首先指出密集集成電路 (IC) 中的晶體管數量大約每兩年翻一番。如果我們頑固地堅持 Dennard 縮放和傳統的 Von Neumann 計算架構,這種預測尤其正確。

在其擴展路線圖中,imec 為芯片技術的未來提出了一條替代路徑,在架構、材料、晶體管的新基本結構以及……范式轉變方面進行了根本性的改變。到 2036 年,imec 路線圖將使我們從 7 nm 到 0.2 nm 或 2 ?ngstr?m,保持兩到兩年半的介紹速度。

首先,光刻技術的不斷進步將是進一步縮小尺寸的關鍵:傳統的光刻技術使用光,而如今,光的波長大于圖案所需的精度。這就是引入極紫外 (EUV) 光刻的原因。它現在出現在越來越多的用于批量生產的功能性生產帶上。EUV 將把我們從5納米時代帶到2納米時代。為了變得更小,我們需要 EUV 的更新版本,High NA-EUV,以及更大的鏡頭。它們的直徑為 1 米,精度為 20 皮米。對于High NA EUV,ASML 正在開發的第一個原型將于 2023 年面世。預計在 2025 年或 2026 年的某個時候投入大批量生產。為了降低在制造業中引入的風險,imec 與阿斯麥正在緊密合作。

同時我們還需要晶體管架構的創新。如今,幾乎所有芯片制造商都使用FinFET晶體管制造微芯片。然而,進入 3nm 代時,FinFET 受到量子干擾,導致微芯片運行中斷。

接下來是環柵 (GAA)或納米片晶體管,由納米片堆疊而成,它將提供改進的性能和改善的短溝道效應。從 2 nm 開始,這種架構將是必不可少的。三星、英特爾和臺積電等主要芯片制造商已經宣布,他們將在其 3 納米和/或 2 納米節點中引入 GAA 晶體管。forksheet 晶體管是 imec 的發明,甚至比 nanosheet 晶體管更密集,將 gate-all-around 概念擴展到 1 nm 一代。forksheet 架構在負溝道和正溝道之間引入了屏障,使溝道更加靠近。該架構有望使單元尺寸縮小 20%。

通過將負溝道和正溝道相互疊加,可以實現進一步的縮放,稱為互補 FET (CFET) 晶體管,是 GAA 的復雜垂直繼承者。它顯著提高了密度,但以增加工藝復雜性為代價,尤其是接觸晶體管的源極和漏極。

隨著時間的推移,CFET 晶體管將采用原子厚度的新型超薄二維單層材料,如二硫化鎢 (WS2) 或鉬。該器件路線圖與光刻路線圖相結合,將帶我們進入埃格斯特倫時代。

這些亞 2 納米晶體管的系統級還面臨著另外兩個挑戰。內存帶寬跟不上 CPU 性能。處理器的運行速度不能超過從內存中獲取數據和指令的速度。要推倒這堵“內存墻”,內存必須離芯片更近。拆除內存墻的一種有趣方法是 3D 片上系統 (3D SOC) 集成,它超越了當今流行的小芯片方法。按照這種異構集成方法,系統被劃分為獨立的芯片,這些芯片在三維中同時設計和互連。例如,它將允許在核心邏輯設備上為 level-1-Cash 堆疊一個 SRAM 內存層,從而實現內存與邏輯的快速交互。

關于與系統相關的挑戰,為芯片提供足夠的功率并散發熱量變得更加困難。然而,一個解決方案就在眼前:配電現在從晶圓頂部穿過十多個金屬層到達晶體管。Imec 目前正在研究晶圓背面的解決方案。我們會將電源軌沉入晶圓,并使用更寬、電阻更小的材料中的納米硅通孔將它們連接到背面。這種方法將電力傳輸網絡與信號網絡分離,提高整體電力傳輸性能,減少路由擁塞,并最終允許進一步標準單元高度縮放。

最后,半導體制造是有代價的。它需要大量的能源和水,并產生危險廢物。但整個供應鏈需要致力于解決這個問題,而生態系統方法將是必不可少的。去年,imec 啟動了可持續半導體技術和系統 (SSTS) 研究計劃,該計劃匯集了半導體價值鏈的利益相關者——從亞馬遜、蘋果和微軟等大型系統公司到供應商,包括 ASM、ASML、KURITA、SCREEN、和東京電子。目標是減少整個行業的碳足跡。該計劃評估新技術對環境的影響,確定影響大的問題,并在技術開發的早期定義更環保的半導體制造解決方案。

模式轉變

從長遠來看,馮諾依曼架構需要徹底改革。馮·諾依曼教授將數字計算機視為一個具有輸入、中央處理器和輸出的系統。但我們需要向特定領域和應用程序相關的架構發展,大規模并行化可與人腦的工作方式相媲美。這意味著 CPU 將扮演更小的角色,有利于為特定工作負載定制電路。

這種范式轉變,加上前方的障礙,標志著半導體行業有趣時代的開始。我們需要在整個半導體生態系統中進行共同創新和協作:代工廠、IDM、無晶圓廠、fab-lite、設備和材料供應商。不僅僅是為了滿足摩爾定律,而是因為半導體是高性能深度技術應用的核心,可以在應對氣候變化、可持續交通、空氣污染和食物短缺等我們這個時代的挑戰方面取得有影響力的進展。 賭注很高。

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52282瀏覽量

437474 -

晶體管

+關注

關注

77文章

9993瀏覽量

140907 -

半導體行業

+關注

關注

9文章

403瀏覽量

41055 -

半導體設備

+關注

關注

4文章

395瀏覽量

15850

原文標題:IMEC發布芯片微縮路線圖:2036年進入0.2 nm時代

文章出處:【微信號:光刻人的世界,微信公眾號:光刻人的世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

全球唯一?IBM更新量子計算路線圖:2029年交付!

三星在4nm邏輯芯片上實現40%以上的測試良率

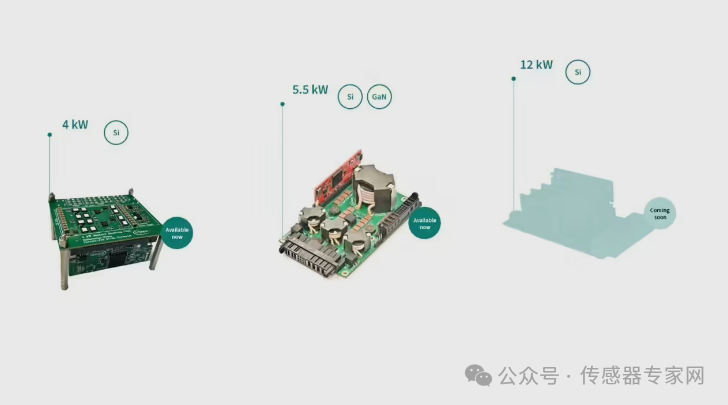

英飛凌公布AI數據中心電池備份單元BBU路線圖,全球首款12kW系統在列

手機芯片進入2nm時代,首發不是蘋果?

OpenAI簡化大模型選擇:薩姆·奧特曼制定路線圖

關于RISC-V學習路線圖推薦

未來10年智能傳感器怎么發展?美國發布最新MEMS路線圖

聯發科攜手臺積電、新思科技邁向2nm芯片時代

三星加速2nm及1.4nm制程投資

聯發科將發布安卓陣營首顆3nm芯片

越南定半導體路線圖:2030年建1芯片廠10封測廠

三星電子計劃在2026年推出最后一代10nm級工藝1d nm

2024學習生成式AI的最佳路線圖

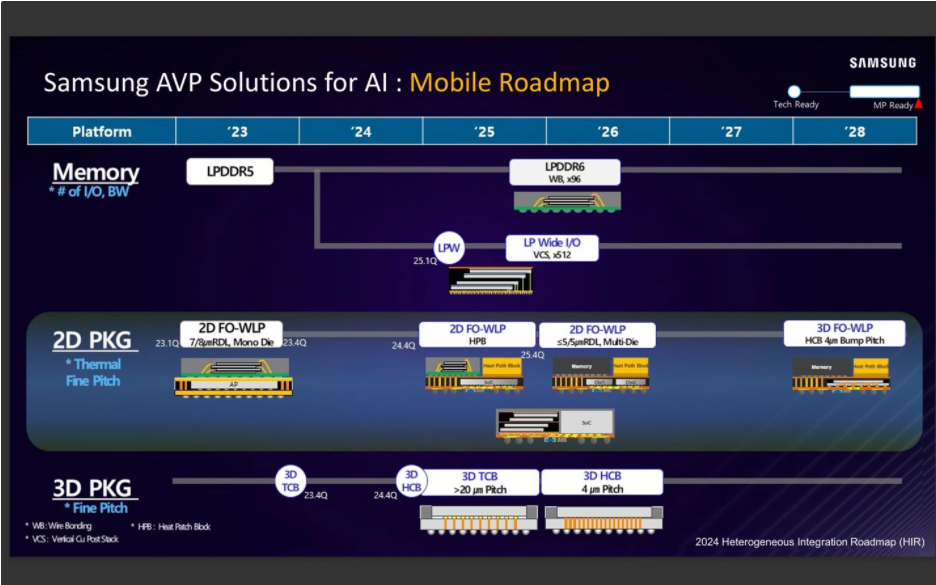

三星電子公布2024年異構集成路線圖,LP Wide I/O移動內存即將面世

IMEC發布芯片微縮路線圖:2036年進入0.2 nm時代

IMEC發布芯片微縮路線圖:2036年進入0.2 nm時代

評論