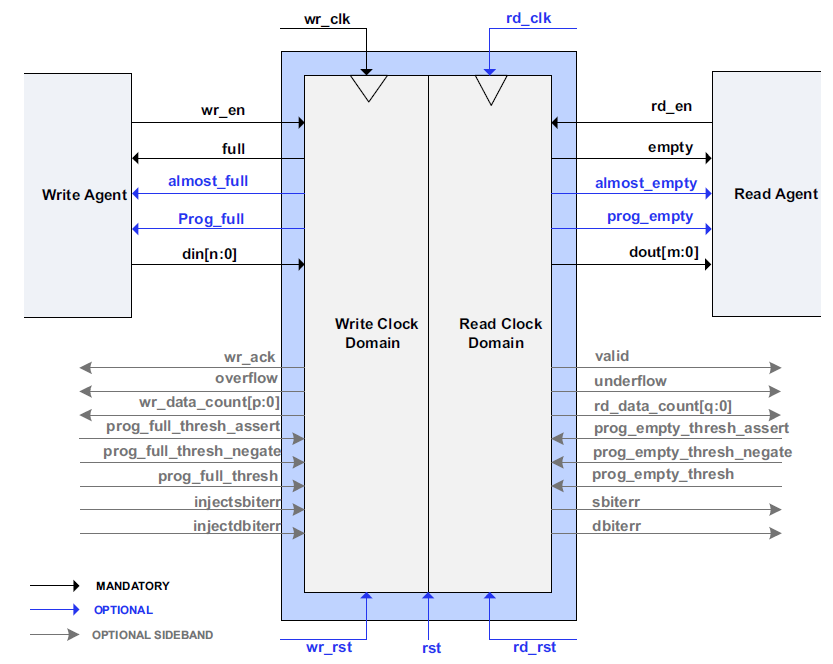

FIFO是實現多位寬數據的異步跨時鐘域操作的常用方法,相比于握手方式,FIFO一方面允許發送端在每個時鐘周期都發送數據,另一方面還可以對數據進行緩存。需要注意的是對FIFO控制信號的管理,以避免發生“寫滿”后繼續寫或“讀空”后繼續讀的狀況。這些控制信號包括寫時鐘域下的寫使能信號(wr_en,輸入)和寫滿標記信號(full,輸出),讀時鐘域下的讀使能信號(rd_en,輸入)和讀空標記信號(empty,輸出),如下圖所示。圖中黑色標記信號為必選信號如輸入/輸出數據信號2(din/dout),藍色標記信號為可選信號如快滿/快空信號(almost_full/almost_empty)。

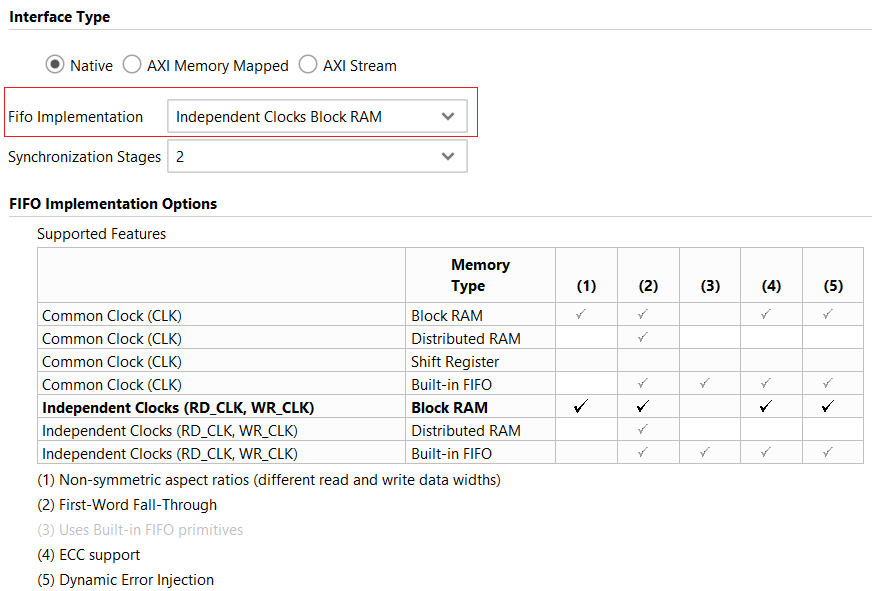

無論是通過XPM方式(XPM_FIFO)還是IP方式(FIFO Generator),都需要注意,因為這里針對的是異步跨時鐘域情形,所以XPM應選擇xpm_fifo_async,使用IP時應選擇Independent Clocks,如下圖所示。

從約束層面看,無論是XPM_FIFO還是IP方式,都會有自帶的約束,如下圖所示。這些自帶約束包括set_max_delay,set_bus_skew和set_false_path,如圖中藍色方框內容所示。尤其要注意的是set_max_delay約束,由于其優先級較set_clock_groups和set_false_path低,故要避免該約束被其所覆蓋,導致約束失效。

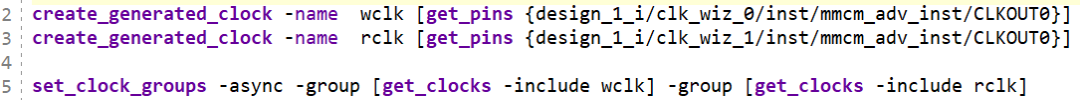

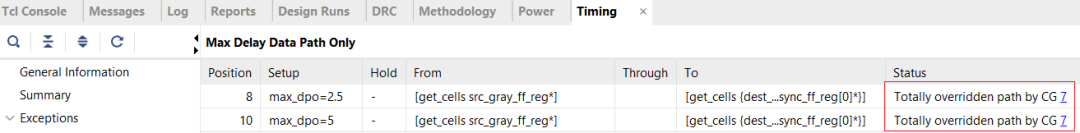

具體來說,如果wr_clk和rd_clk兩個時鐘域下除了通過FIFO隔離的路徑外,還有其他跨時鐘域路徑,對于這些跨時鐘域路徑,倘若直接采用set_clock_groups進行約束,如下圖所示,那么就會導致FIFO自帶的set_max_delay被覆蓋掉。這可通過命令report_exceptions查看,如下圖所示,注意圖中紅色方框標記。

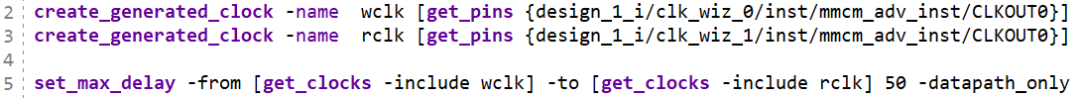

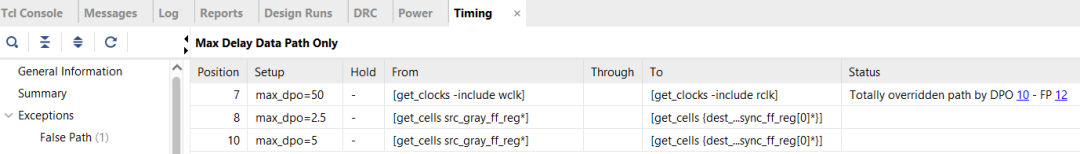

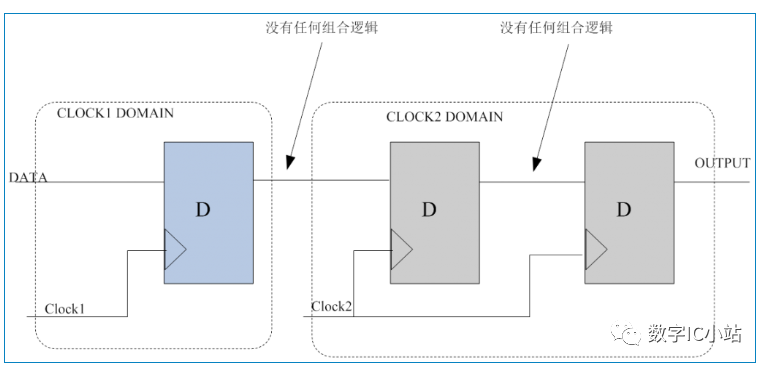

在這種情形下,顯然不能再用set_clock_groups進行約束。那么該如何對這些跨時鐘域路徑約束呢?我們分情況討論。如果對這些跨時鐘域路徑操作使用的是XPM_CDC,那么Vivado會直接使用其自帶約束,這些自帶約束的作用域僅限于XPM_CDC,所以不會覆蓋FIFO自帶約束。如果對這些跨時鐘域路徑操作使用的是用戶模塊,那么在約束時,若確認為偽路徑,應使用set_false_path,同時-from和-to的對象應使用get_cells或get_pins獲取,而不能使用get_clocks獲取。如果cell較多,而且也無法用通配符完全匹配到,那么可以使用如下方式:即仍使用set_max_delay外加選項-datapath_only,-from和-to的對象仍通過get_clocks獲取,而延遲值可以填一個很大的值,如這里的50(代表50ns),這樣就等效于set_false_path。report_exceptions的結果也顯示FIFO自帶約束沒有被覆蓋,如下圖所示。

綜上所述,使用異步FIFO完成多位寬數據的跨時鐘域操作時,要注意FIFO自帶有set_max_delay約束,確保該約束不會被set_false_path或set_clock_groups所覆蓋,否則可能發生時序收斂,但系統不能正常工作的情形。

審核編輯:湯梓紅

-

電路設計

+關注

關注

6701文章

2528瀏覽量

213020 -

fifo

+關注

關注

3文章

400瀏覽量

44649 -

信號

+關注

關注

11文章

2844瀏覽量

77958 -

時鐘域

+關注

關注

0文章

53瀏覽量

9736 -

Vivado

+關注

關注

19文章

831瀏覽量

68322

原文標題:跨時鐘域電路設計(7):多位寬數據通過FIFO跨時鐘域

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

跨時鐘域電路設計:多位寬數據通過FIFO跨時鐘域

跨時鐘域電路設計:多位寬數據通過FIFO跨時鐘域

評論