跨時鐘域操作包括同步跨時鐘域操作和異步跨時鐘域操作。同步跨時鐘域意味著發(fā)送時鐘和接收時鐘是同步的,比如兩個時鐘是同一個MMCM生成的,在這種情況下,這兩個時鐘有明確的相位關(guān)系。

所以,同步跨時鐘域操作重要的是做好約束。無論是從快時鐘域到慢時鐘域還是從慢時鐘域到快時鐘域,都可以通過多周期路徑約束實現(xiàn),同時還要注意時鐘偏移對跨時鐘域路徑時序的影響。

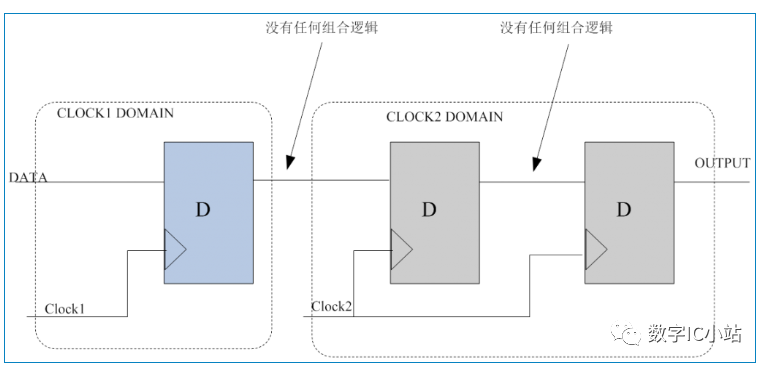

對于異步跨時鐘域操作,由于發(fā)送時鐘和接收時鐘是異步的,也就是兩者不存在明確的相位關(guān)系,這時既要從硬件電路上保證設(shè)計是安全的,又要從約束層面確保數(shù)據(jù)被穩(wěn)定接收。

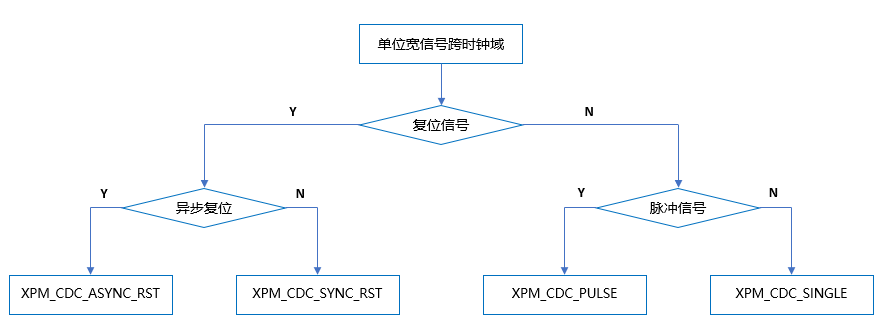

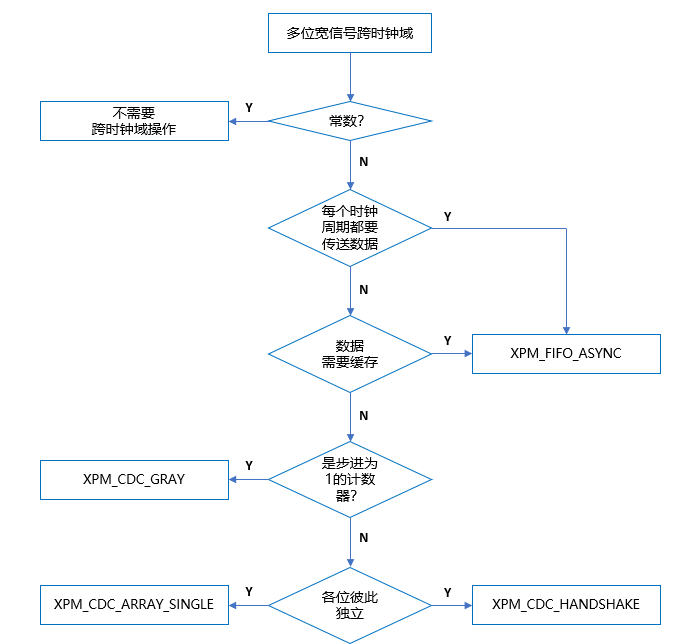

根據(jù)數(shù)據(jù)位寬可分為兩種情形:單位寬信號跨時鐘域和多位寬信號跨時鐘域。此時,可使用XPM_CDC,具體使用哪個模塊,可參考如下兩個流程。

審核編輯:劉清

-

CDC

+關(guān)注

關(guān)注

0文章

57瀏覽量

18149 -

XPM

+關(guān)注

關(guān)注

0文章

12瀏覽量

8790

原文標(biāo)題:跨時鐘域電路設(shè)計(8):總結(jié)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

跨時鐘域的解決方案

從電路的角度出發(fā),提出了一種新的SOC跨時鐘域同步電路設(shè)計的方法

如何利用FPGA設(shè)計一個跨時鐘域的同步策略?

關(guān)于FPGA中跨時鐘域的問題分析

跨時鐘域電路設(shè)計:多位寬數(shù)據(jù)通過FIFO跨時鐘域

跨時鐘域電路設(shè)計:單位寬信號如何跨時鐘域

fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發(fā)送過來的數(shù)據(jù)?

如何處理跨時鐘域這些基礎(chǔ)問題

跨時鐘域電路設(shè)計總結(jié)

跨時鐘域電路設(shè)計總結(jié)

評論