- 亞穩態

跨時鐘域(CDC)的應從對亞穩定性和同步性的基本了解開始。用普通的話來說,亞穩定性是指不穩定的中間狀態,但是在此狀態下,任何微小的擾動將導致最終狀態變為穩定狀態,但是并不能保證最終的狀態就是設計所期待的狀態,換句話就是可能發生傳輸錯誤。當應用于數字電路中的觸發器時,它表示觸發器的輸出可能尚未穩定,不確定是否能到最終期望值的狀態。

觸發器進入亞穩態的一種方法是違反了其建立或保持時間。在異步時鐘域跨越(CDC)中,其中源時鐘和目標時鐘沒有頻率關系,來自源域的信號在驅動目的域的觸發器時,無法保證目的域的觸發器能夠滿足建立時間和保持時間。當目的域的觸發器的輸出變為亞穩態并且在必須再次對其輸出進行采樣(由目標域中的第二個觸發器完成)時尚未收斂,則將發生同步失敗。更糟糕的是,下一個觸發器也可能變為亞穩態,從而導致亞穩定性在設計中傳播!

- 跨時鐘域同步器

同步器是跨時鐘域中設計的一種常用電路,其目的是把同步失敗的可能性降到最低。我們希望亞穩態在一個同步周期(目標時鐘域的時鐘周期)內解決,以便我們可以在目標時鐘域中使得觸發器的輸出是安全采樣值。在此我們把同步器的兩次采樣出現問題之間的時間間隔,稱為平均故障間隔時間(MTBF)。

在跨時鐘域(CDC)中出現亞穩態的概率與以下因素成正比:

- 目標時鐘域的時鐘頻率

- 跨時鐘邊界的數據傳輸速率

根據上述因素,我們常用的同步器電路如下:

-

兩個觸發器同步器

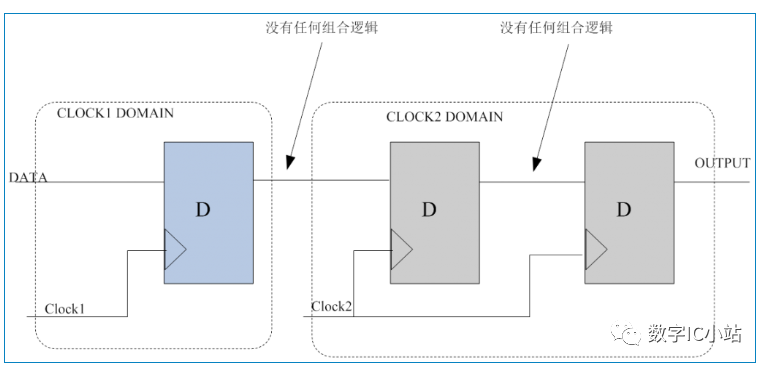

最基本的同步器是兩個串聯的觸發器,均由目的時鐘域提供時鐘。這個電路稱為兩個觸發器同步器。如果輸入數據的變化非常接近接收時鐘邊沿(在建立/保持時間內),則同步器中的第一個觸發器可能會變為亞穩態,但是在信號被采樣之前,仍然有一個完整的時鐘使信號變得穩定--第二觸發器。然后,目標時鐘域的邏輯使用的是第二個觸發器的輸出。

兩級觸發器可防止亞穩態傳播的原理:假設第一級觸發器的輸入不滿足其建立/保持時間,它在第一個脈沖沿到來后輸出的數據就為亞穩態,那么在下一個脈沖沿到來之前,其輸出的亞穩態數據在一段恢復時間后必須穩定下來,而且穩定的數據必須滿足第二級觸發器的建立時間,如果都滿足了,在下一個脈沖沿到來時,第二級觸發器將不會出現亞穩態,因為其輸入端的數據滿足其建立保持時間。同步器有效的條件:第一級觸發器進入亞穩態后的恢復時間 + 第二級觸發器的建立時間 <= 時鐘周期。如果不滿足上述表達式,那么到第二個觸發器開始,信號仍然可能是亞穩態的。在這種情況下,將發生同步錯誤,并且設計可能會發生故障,但是這種情況是很罕見的。

兩個觸發器同步器足以滿足很大部分應用的需求了。為了進一步提高MTBF,有時會使用具有更好的建立/保持時間特性的庫單元(其具有低閾值電壓)構建兩個觸發器同步器。

在跨時鐘域(CDC)發送信號到同步器之前,通常先在源時鐘域中使用寄存器保存信號。這也是為什么上圖中介紹為什么在兩個時域的觸發器之間需要沒有組合邏輯的原因,只有這樣才可以首先消除了組合電路產生的毛刺。如下圖所示:

因為在組合邏輯電路中常常因為各個輸入信號的不一致性以及各路徑延遲的不一樣,可能導致輸出結果存在毛刺。

而在跨時鐘域時,又不確定目的時鐘域時鐘上升沿什么時候到來,因此目的時鐘域時鐘的采樣就更加無法保證。

因此必須保證兩個時域的觸發器之間沒有組合邏輯。

- 慢時鐘域到快時鐘域

最簡單的情況是將信號從慢速時鐘域傳遞到快速時鐘域。只要快時鐘的頻率大于慢時鐘頻率的1.5-2倍,通常就不會有問題。快速目標時鐘將簡單地對慢速信號進行多次采樣。在這些情況下,一個簡單的兩級串聯觸發器同步就足夠了。

目的時鐘域如果不采取任何操作,那么就會多次采樣同一個值,這會導致一個問題--電路誤以為這是多個操作。因此為了避免這種錯誤的發生,通常添加一些簡單的邏輯使得同步后的采樣值出現周期和原時鐘域的一樣。具體操作,在soc設計方法與實現書上有講。

如果快時鐘的頻率小于慢時鐘頻率的1.5倍,也就是稍微快點,這個歡迎各位討論,我覺得使用。

- 快時鐘域到慢時鐘域

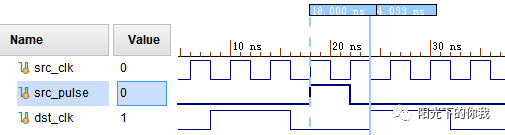

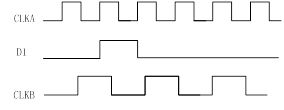

困難的情況是將快速信號傳遞到慢速時鐘域。明顯的問題是,如果快速信號上的脈沖短于慢速時鐘的周期,則該脈沖可能會在被慢速時鐘采樣之前消失。下面的波形顯示了這種情況。

還有一個考慮較少的問題是,即使脈沖只是比慢時鐘的周期稍寬,信號也會在目標觸發器的建立/保持時間內(在慢時鐘上)變化,這會違反時序并導致亞穩性。

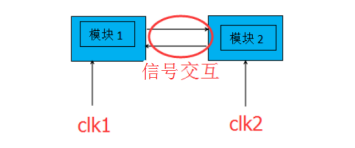

在處理上述問題時,首先應該確認是否需要源信號中的每個值,如果可以不需要,那么采樣在上文異步fifo中設計的格雷碼就可以異步FIFO設計。當然如果需要在目的域中使用每個值,那么就得想辦法設計新方法。

- 還是使用兩級觸發器

一個簡單的兩個觸發器同步器是跨時鐘域交叉傳輸信號的最快方法。只要在快速時鐘域中生成的信號比慢速時鐘的周期時間寬,在許多應用中就足夠了。例如,如果只需要同步緩慢變化的狀態信號,則可能會起作用。一個安全的經驗法則是信號必須大于目標時鐘周期寬度的1.5倍。這保證了信號將被目標時鐘的至少一個(但可能更多)時鐘沿采樣。可以使用SystemVerilog斷言(SVA)輕松檢查需求。

當源和目標的相對時鐘頻率固定時,很容易實現1.5x的周期寬度。但是在現實世界中,情況并非如此。目標時鐘可以采用多種不同的頻率,它們可以與源時鐘更快/更低/相同。在那種情況下,設計時鐘域交叉信號來滿足最慢目標時鐘的1.5倍周期寬度并不容易。

- 采用具有反饋信號的同步器

上圖中,源域通過兩個觸發器同步器將信號發送到目的時鐘域,然后通過另一個兩個觸發器同步器將同步信號傳遞回源時鐘域,作為反饋確認。下圖顯示了同步器的波形。

該解決方案非常安全,但是由于在允許再次更改信號之前需要在兩個方向上進行同步,因此確實存在增加延遲的代價。

-

SoC設計

+關注

關注

1文章

151瀏覽量

19108 -

MTBF

+關注

關注

1文章

30瀏覽量

13797 -

CDC

+關注

關注

0文章

57瀏覽量

18145 -

觸發器

+關注

關注

14文章

2033瀏覽量

61916 -

同步器

+關注

關注

1文章

106瀏覽量

15075

發布評論請先 登錄

從電路的角度出發,提出了一種新的SOC跨時鐘域同步電路設計的方法

跨時鐘域電路設計:多位寬數據通過FIFO跨時鐘域

跨時鐘域電路設計—單比特信號傳輸

跨時鐘域電路設計—單比特信號傳輸

評論