本文分別對quartus和vivado防止信號被優化的方法進行介紹。

為什么要防止信號被優化

在FPGA開發調試階段,經常遇到這樣的情況,需要臨時添加信號,觀察信號變化,用來定位代碼中存在的問題,很多時候這些臨時添加的信號會被綜合工具優化掉,為了防止這種情況的發生,可以使用添加虛擬引腳(quartus)和代碼中添加屬性(vivado)。

下面分別對兩種方法進行說明,在原有代碼中加入如下代碼,觀察cnt信號是否被優化,能否通過邏輯分析儀進行觀測。

reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

Quartus中如何設置虛擬引腳

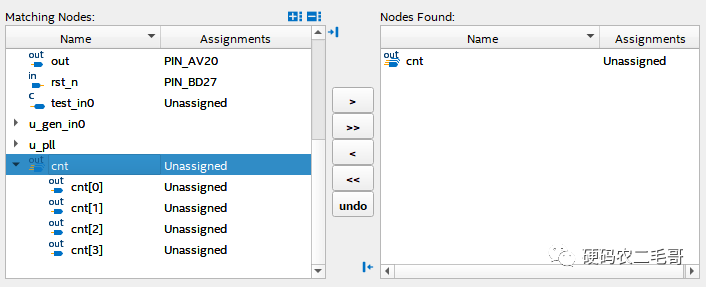

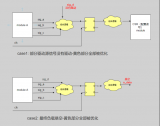

在quartus中加入上述代碼后,將cnt信號設置成輸出引腳。 下面將cnt信號設置為虛擬引腳。

方法1:

在qsf文件中添加如下內容:

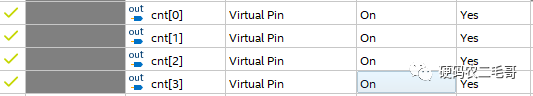

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[0]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[1]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[2]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[3]

編譯后,添加signal tap,cnt信號可以添加,說明沒有被優化。

方法2:

將cnt信號設置成輸出后,打開Assignment Editor,進行如下設置。

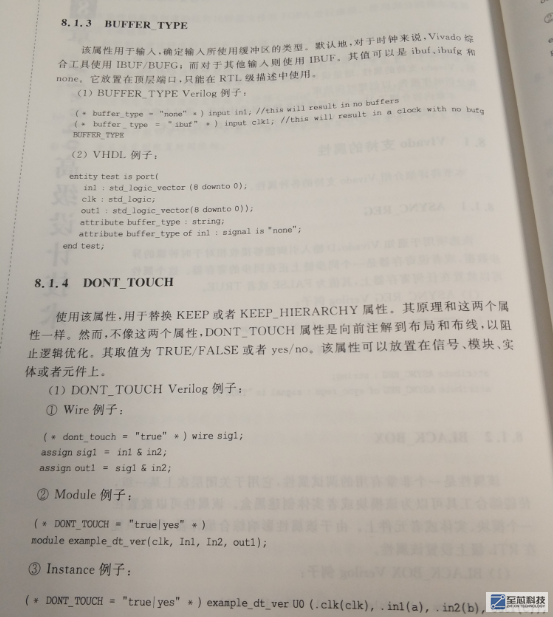

Vivado中防止信號被優化

在代碼中加入(* dont_touch = "true" *) 。

(* dont_touch = "true" *) reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

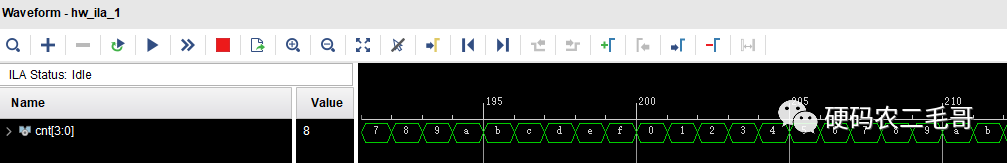

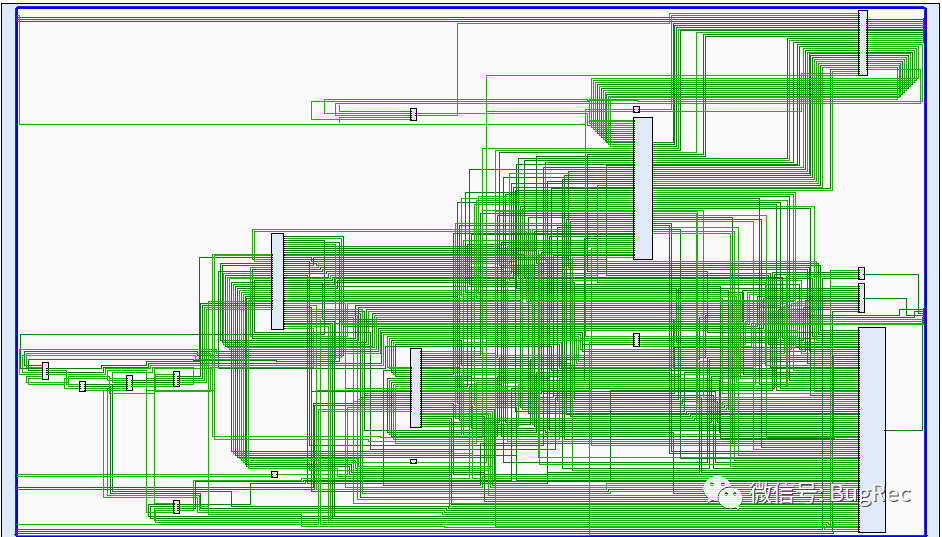

重新編譯后,使用ila觀測cnt,ila中有信號,證明信號沒有被優化。

-

FPGA

+關注

關注

1643文章

21982瀏覽量

614550 -

信號

+關注

關注

11文章

2844瀏覽量

77947 -

引腳

+關注

關注

16文章

1614瀏覽量

52428 -

quartus

+關注

關注

17文章

172瀏覽量

75278 -

Vivado

+關注

關注

19文章

831瀏覽量

68304

發布評論請先 登錄

FPGA中的I_O時序優化設計

今日說“法”:如何防止reg、wire型信號在使用邏輯分析儀時被優化

如何有效防止FPGA設計被克隆?

防止Wi-Fi信號被截獲的墻紙(英國開發)

FPGA信號處理算法設計、實現以及優化(南京)

怎樣防止手機被屏蔽

信號管腳任務可進行多個FPGA的I/O優化

PCB設計中的高速信號傳輸優化技巧

FPGA在線調試信號被優化原因分析及防止優化方法總結

FPGA設計中如何防止信號被優化

FPGA設計中如何防止信號被優化

評論