英特爾宣布在業內率先在產品級測試芯片上實現背面供電(backside power delivery)技術,滿足邁向下一個計算時代的性能需求。作為英特爾業界領先的背面供電解決方案,PowerVia將于2024年上半年在Intel 20A制程節點上推出。通過將電源線移至晶圓背面,PowerVia解決了芯片單位面積微縮中日益嚴重的互連瓶頸問題。

“

英特爾正在積極推進‘四年五個制程節點’計劃,并致力于在2030年實現在單個封裝中集成一萬億個晶體管,PowerVia對這兩大目標而言都是重要里程碑。通過采用已試驗性生產的制程節點及其測試芯片,英特爾降低了將背面供電用于先進制程節點的風險,使得我們能領先競爭對手一個制程節點,將背面供電技術推向市場。

--Ben Sell

英特爾技術開發副總裁

”

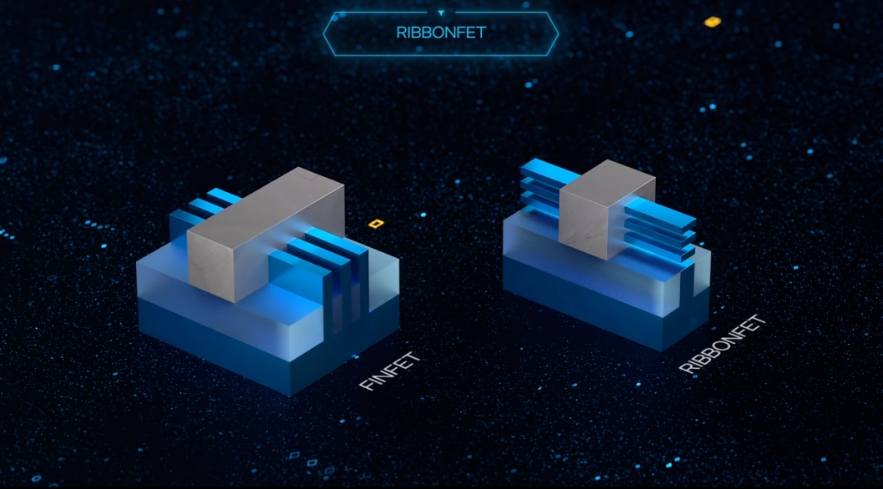

英特爾將PowerVia技術和晶體管的研發分開進行,以確保PowerVia可以被妥善地用于Intel 20A和Intel 18A制程芯片的生產中。在與同樣將與Intel 20A制程節點一同推出的RibbonFET晶體管集成之前,PowerVia在其內部測試節點上進行了測試,以不斷調試并確保其功能良好。經在測試芯片上采用并測試PowerVia,英特爾證實了這項技術確實能顯著提高芯片的使用效率,單元利用率(cell utilization)超過90%,并有助于實現晶體管的大幅微縮,讓芯片設計公司能夠提升產品性能和能效。

英特爾將在于6月11日至16日在日本京都舉行的VLSI研討會上通過兩篇論文展示相關研究成果。

作為大幅領先競爭對手的背面供電解決方案,PowerVia讓包含英特爾代工服務(IFS)客戶在內的芯片設計公司能更快地實現產品能效和性能的提升。長期以來,英特爾始終致力于推出對行業具有關鍵意義的創新技術,如應變硅(strained silicon)、高K金屬柵極(Hi-K metal gate)和FinFET晶體管,以繼續推進摩爾定律。隨著PowerVia和RibbonFET全環繞柵極技術在2024年的推出,英特爾在芯片設計和制程技術創新方面將繼續處于行業領先地位。

通過率先推出PowerVia技術,英特爾可幫助芯片設計公司突破日益嚴重的互連瓶頸。越來越多的使用場景,包括AI或圖形計算,都需要尺寸更小、密度更高、性能更強的晶體管來滿足不斷增長的算力需求。從數十年前到現在,晶體管架構中的電源線和信號線一直都在“搶占”晶圓內的同一塊空間。通過在結構上將這兩者的布線分開,可提高芯片性能和能效,為客戶提供更好的產品。背面供電對晶體管微縮而言至關重要,可使芯片設計公司在不犧牲資源的同時提高晶體管密度,進而顯著地提高功率和性能。

此外,Intel 20A和Intel 18A制程節點將同時采用PowerVia背面供電技術和RibbonFET全環繞柵極技術。作為一種向晶體管供電的全新方式,背面供電技術也帶來了散熱和調試設計方面的全新挑戰。

通過將PowerVia與RibbonFET這兩項技術的研發分開進行,英特爾能夠迅速應對上述挑戰,確保能在基于Intel 20A和Intel 18A制程節點的芯片中實現PowerVia技術。英特爾開發了散熱技術,以避免過熱問題的出現,同時,調試團隊也開發了新技術,確保這種新的晶體管設計結構在調試中出現的各種問題都能得到適當解決。因此,在集成到RibbonFET晶體管架構之前,PowerVia就已在測試中達到了相當高的良率和可靠性指標,證明了這一技術的預期價值。

PowerVia的測試也利用了極紫外光刻技術(EUV)帶來的設計規則。在測試結果中,芯片大部分區域的標準單元利用率都超過90%,同時單元密度也大幅增加,可望降低成本。測試還顯示,PowerVia將平臺電壓(platform voltage)降低了30%,并實現了6%的頻率增益(frequency benefit)。PowerVia測試芯片也展示了良好的散熱特性,符合邏輯微縮預期將實現的更高功率密度。

接下來,在將于VLSI研討會上發表的第三篇論文中,英特爾技術專家Mauro Kobrinsky還將闡述英特爾對PowerVia更先進部署方法的研究成果,如同時在晶圓正面和背面實現信號傳輸和供電。

英特爾領先業界為客戶提供PowerVia背面供電技術,并將在未來繼續推進相關創新,延續了其率先將半導體創新技術推向市場的悠久歷史。

-

英特爾

+關注

關注

61文章

10188瀏覽量

174309 -

cpu

+關注

關注

68文章

11063瀏覽量

216511

原文標題:英特爾PowerVia技術率先實現芯片背面供電,突破互連瓶頸

文章出處:【微信號:英特爾中國,微信公眾號:英特爾中國】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

世紀大并購!傳高通有意整體收購英特爾,英特爾最新回應

英特爾先進封裝,新突破

新思科技與英特爾在EDA和IP領域展開深度合作

英特爾持續推進核心制程和先進封裝技術創新,分享最新進展

背面供電搭配全環繞柵極,英特爾打造芯片制造“新星組合”

英特爾代工在IEDM 2024展示多項技術突破

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

英特爾PowerVia技術率先實現芯片背面供電,突破互連瓶頸

英特爾PowerVia技術率先實現芯片背面供電,突破互連瓶頸

評論