發生亞穩態的原因是信號在傳輸的過程中不能滿足觸發器的建立時間和保持時間。發生亞穩態時,觸發器的輸出是個中間態,也是x態,不能確定為0或1,而且這個亞穩態還會往后傳遞至更多的組合邏輯和時序邏輯電路。

所謂建立時間,就是在clk有效邊沿到來之前輸入信號需要保持穩定的最小時間;所謂保持時間,就是在clk有效邊沿到來之后輸入信號還需要保持穩定的最小時間。

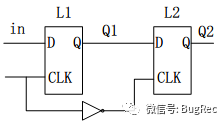

為了簡便分析,將一個觸發器的結構簡化為下圖:

一個觸發器等效為兩個觸發電平不一樣的鎖存器的信號鏈;鎖存器的特性為:

- 當clk為有效電平時,鎖存器是透傳模式,Q隨著D的變化而變化;

- 當clk為無效電平時,鎖存器在鎖存模式,Q為之前保存的值,D輸入值不會對Q有影響。

所以,如上圖,當clk為低電平的時候, L1為透明傳輸模式,輸入信號in透傳至Q1,但是L2是鎖存模式,Q2并不會受到Q1的影響;

而當clk翻轉至高電平時,L1將會進入鎖存模式,這個過程需要一段時間完成。L2會進入透傳模式,而此時L1可能還處于透傳模式。那么在clk翻轉之前的一段時間到L1完成進入鎖存,L2進入透傳模式這段時間內,輸入信號in都是不可以變化的,否則可能導致Q1傳導中間值,進而Q2也傳輸x態,也就是所謂的亞穩態。

圖來自百度百科

再探討一些異步信號同步的方法原理。對于單bit信號來說,我們都知道一般用兩個DFF觸發器來做同步,當然這不是一定的,具體幾個DFF需要根據兩個時鐘域的頻率做計算。但本文分析以兩個DFF觸發器為例。

值得一提的是,多個DFF觸發器解決異步信號同步的亞穩態方案,并不能完全地消除亞穩態,只是極大地降低了亞穩態發生的概率。有一個MTBF的平均無故障時間公式計算,公式跟芯片工藝的PVT,接收數據時鐘頻率,接收數據的翻轉率有關。如果我們的MTBF時間大于產品的保質期,可以視為沒問題(保修期的作用之一)

圖來自百度百科

那么,為什么加兩個觸發器就能降低亞穩態的概率呢?從電路上分析來說,雖然觸發器的輸出是中間值,但是現實世界中是存在噪聲的,那么一定會導致信號會偏向某個固定值0或1。但這個過程是需要一定時間的,所以通過加兩級觸發器,讓這個趨向確定值的過程在觸發器傳遞過程中完成,那么最后觸發器的輸出就是一個確定值了。

當然,也會發生某些情況下,這個趨向確定值的過程會很漫長,所以說只能降低發生的概率而不能消除。

那么對于多bit信號的同步呢,在我看來,方案是讓把多bit信號轉換為單bit信號同步(格雷碼),或者讓多bit信號保持穩定,只要能夠保證在接收數據時鐘域內,信號一直穩定不變,就不會產生亞穩態。大家可以想想諸如FIFO,D-MUX,握手等方法是不是等待多bit信號穩定后再去采樣。

-

鎖存器

+關注

關注

8文章

923瀏覽量

42255 -

觸發器

+關注

關注

14文章

2034瀏覽量

62015 -

FIFO存儲

+關注

關注

0文章

103瀏覽量

6170 -

CLK

+關注

關注

0文章

127瀏覽量

17573 -

dff

+關注

關注

0文章

26瀏覽量

3616

發布評論請先 登錄

利用IDDR簡化亞穩態方案

FPGA中亞穩態——讓你無處可逃

FPGA中亞穩態——讓你無處可逃

FPGA觸發器的亞穩態認識

fpga亞穩態實例分析

在FPGA復位電路中產生亞穩態的原因

FPGA--中復位電路產生亞穩態的原因

關于FPGA設計的同步信號和亞穩態的分析

今日說“法”:讓FPGA設計中的亞穩態“無處可逃”

一種消除異步電路亞穩態的邏輯控制方法

關于FPGA設計中的亞穩態及其緩解措施的分析和介紹

從鎖存器角度看亞穩態發生的原因及方案簡單分析

從鎖存器角度看亞穩態發生的原因及方案簡單分析

評論