數據采集和通用測試測量設備中使用的精密信號鏈必須適應寬廣的輸入電平范圍。信號鏈可能需要提供高輸入阻抗,同時支持增益和衰減,并調整共模電平以確保信號落在ADC的適當輸入范圍內。

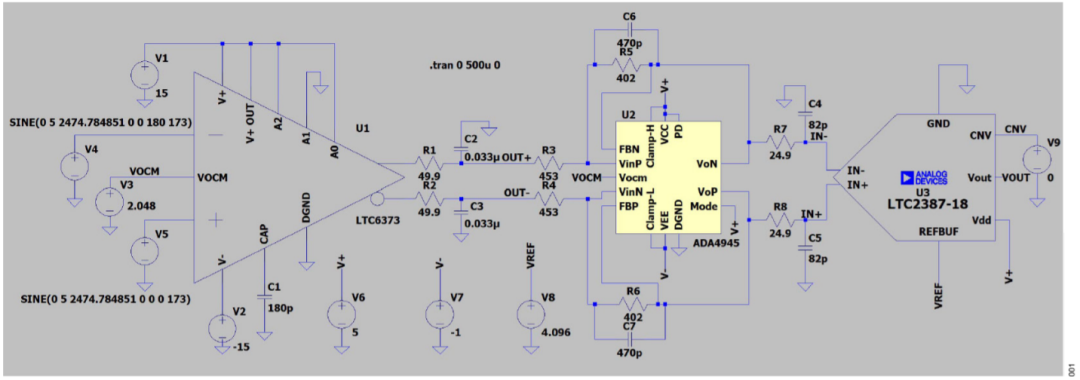

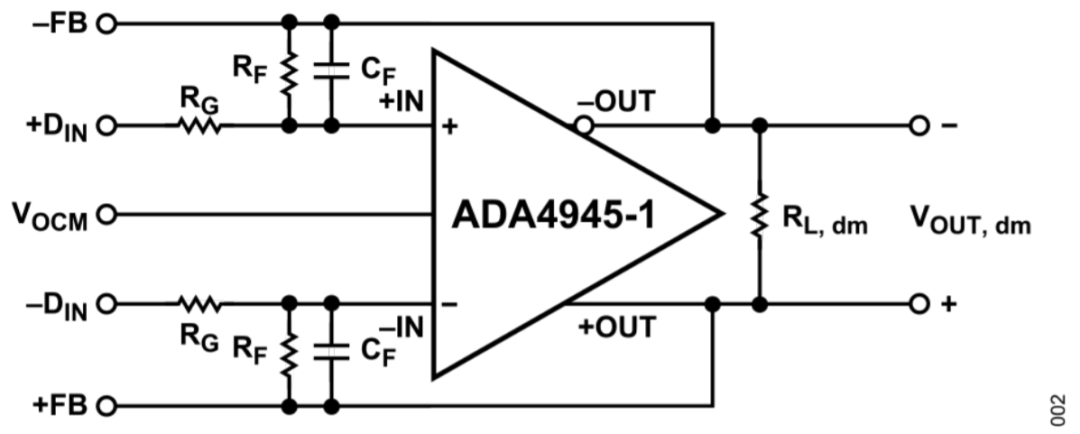

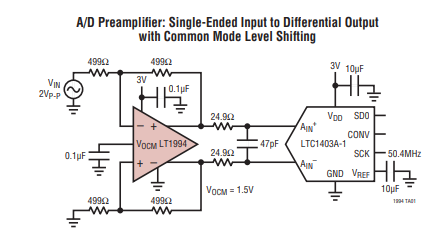

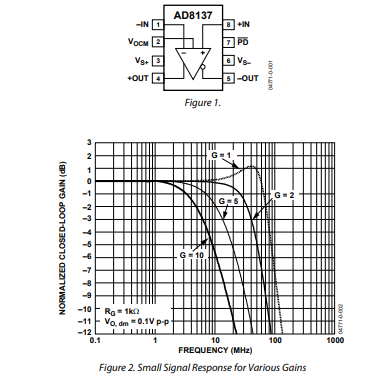

圖1中的原理圖顯示了兩級信號調理,它能調整差分雙極性±10 V輸入信號,并將其轉換為 ADC所需的共模電平為 2.048 V的全差分±4.096 V信號。設計目標是實現上述調理,同時不降低ADC的噪聲和失真性能。ADC 驅動器需要的電源電壓通常超過 ADC 的輸入范圍,從而為輸入和輸出擺幅電壓提供一定的裕量。驅動器通常必須調整并轉換第一級輸出電壓,使之匹配ADC的輸入電壓范圍(例如,將真雙極性差分信號轉換為擺幅為從地到VREF的差分信號)。

圖 1. 雙極性輸入、全差分輸出 ADC 驅動器的 LTspice 原理圖

圖1中的原理圖通過LTspice創建,LTspice一款高性能SPICE III仿真軟件、原理圖采集工具和波形查看器,集成增強功能和模型,簡化了開關穩壓器、線性穩壓器和信號鏈電路的仿真。有關圖1所示器件的更多信息,請參閱 LTC6373 、 ADA4945-1 和LTC2387-18數據手冊。

Tips

具有全差分輸出的精密儀器儀表放大器 LTC6373 可在ADI 中國在線商城直接下單采購。現在下單,還可領取好禮一份哦,點擊查看活動詳情。

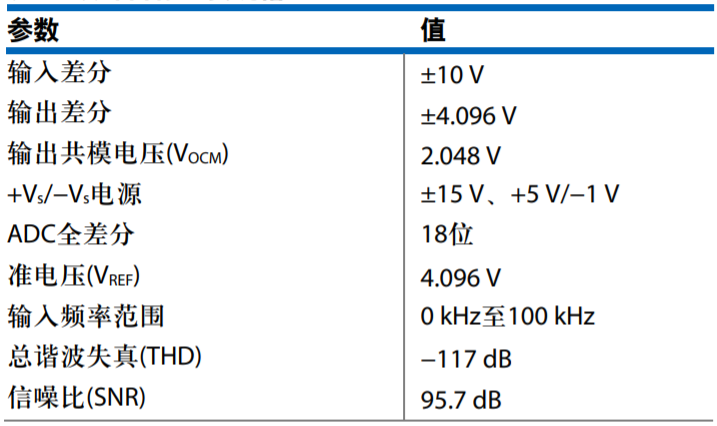

主要設計規格

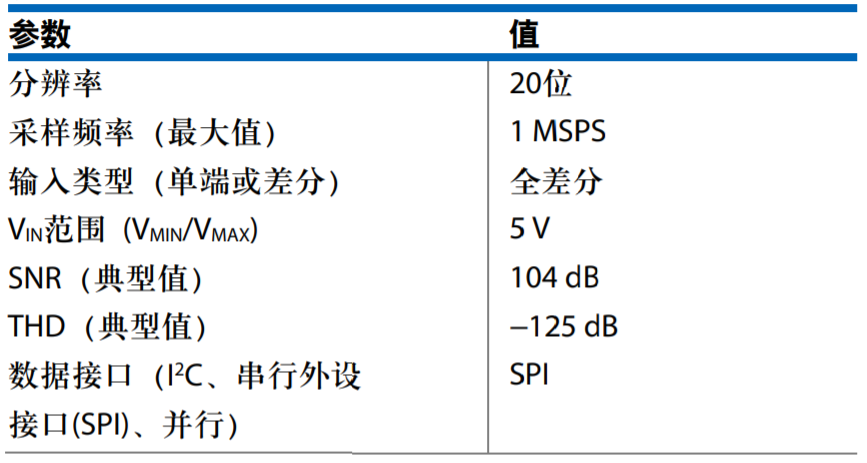

對于±10 V的真雙極性輸入信號范圍,主要設計規格如表1所示。對于差分±10 V峰值正弦波,該電路可輸出±4.096 V差分信號。

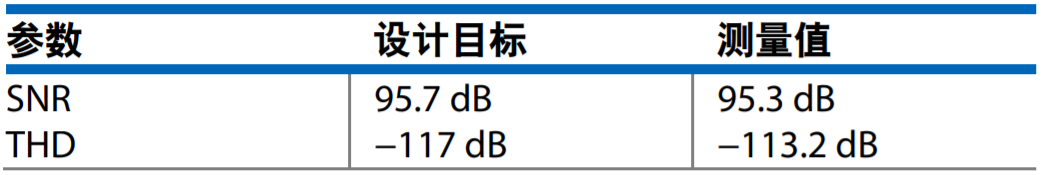

表 1. 設計目標主要規格

設計說明

該電路是一個ADC驅動器電路,具有非常高的輸入阻抗,并且可以定制以驅動較寬的輸入電壓,包括單端和差分。該電路的輸出信號能夠驅動采集時間小于30 ns的ADC。同時,該電路還能保持優化的噪聲和失真性能。圖1中的電路由以下器件組成:LTC6373可編程增益儀表放大器,用作輸入級;ADA4945-1全差分放大器(FDA),用作第二級ADC驅動器;以及18位、15 MSPS ADC LTC2387-18。此外,在LTC6373輸出端和ADA4945-1輸入端之間有一個100 kHz濾波器,用于降低噪聲,并且在ADA4945-1輸出端和LTC2387-18輸入端之間有一個毛刺抑制/降噪濾波器。LTC6373配置為差分放大器,其增益為0.5,輸出共模電壓為2.048 V。ADA4945-1配置為衰減差分動器,其增益為0.8。ADA4945-1 具有 2.048 V 的輸出共模電壓,與LTC2387-18輸入范圍兼容。LTC2387-18各輸入端的輸入信號范圍為0 V至4.096 V,因此使用4.096 V內部基準電壓時,差分輸入信號范圍為±4.096 V。

設計技巧

如果需要更大或更小的信號范圍,可以改變LTC6373的增益和RF/RG的比率。例如,如果需要±100 mV的信號范圍,可以增加RF,而RG保持原始值不變。可以使用下式來重新計算RF:

其中:

由于ADA4945-1的具備更高的增益帶寬積,因此建議提高該器件的增益,而不提高LTC6373的增益。

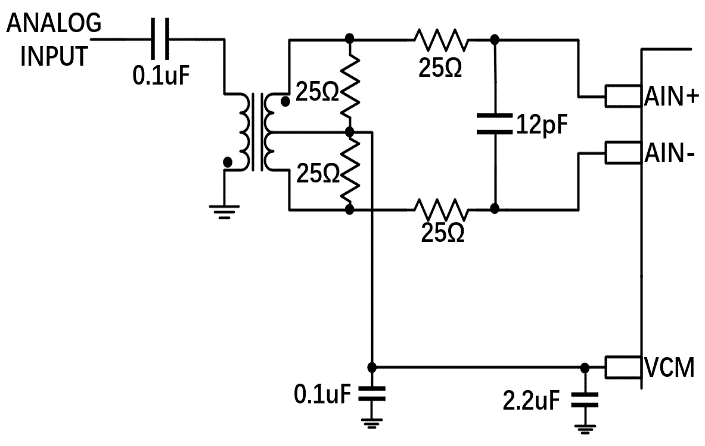

由R5、C6、R6和C7組成的濾波器會降低ADA4945-1的帶寬。較低帶寬導致LTC2387-18輸入端的噪聲較低。C6和C7的值通過試驗方式確定,即逐漸增加其值,直到SNR停止改善為止。

由電阻R7、R8和電容C4、C5組成的濾波器有助于將ADA4945-1輸出與ADC輸入(如果未緩沖的話)產生的采樣毛刺隔離開來。它會限制提供給ADC輸入的信號帶寬,并有助于降低ADC輸入端的噪聲。

如果驅動器和ADC之間的濾波器沒有時間來完成建立,則會產生增益誤差。根據具體應用,很小的增益誤差可能是可以容忍的,但無法建立也可能導致失真,必須避免這種情況。可利用精密ADC驅動器工具來檢查濾波器建立并估算電路SNR和THD性能。

設計步驟

初始條件和假設

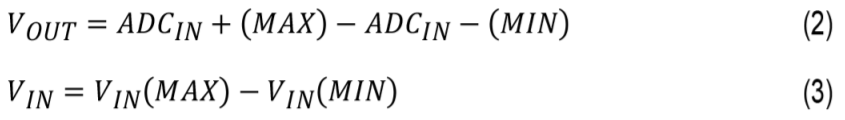

LTC6373的電源設置為±15 V,ADA4945-1的電源設置為+5 V/?1 V。假設輸入范圍為20 V p-p (±10 V),輸出范圍為8.192 V p-p(進入ADC),則分布在模擬前端(AFE)上的總增益為:

留一些裕量以適應器件容差和共模的微小變化,總增益目標設置為0.4 V/V。LTC6373支持固定的增益值選擇:{0.25, 0.5, 1, 2, ..., 16}。兩級的增益均選擇小于1的值,以支持ADA4945-1使用較小的電源范圍,并降低每級的噪聲增益。將LTC6373的增益設置為0.5,這導致ADA4945-1的增益為0.8。

LTC6373和ADA4945-1的共模電壓均設置為2.048 V。

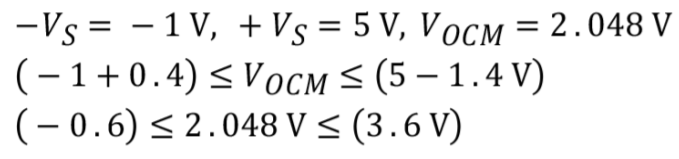

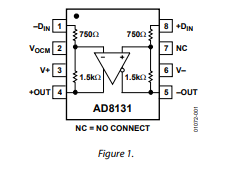

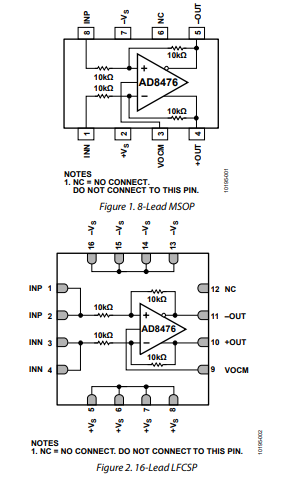

圖 2. ADA4945-1 的電路定義

-

對于 ADC (LTC2387-18),將滿量程輸入設置為±4.096 V,VREF = 4.096 V,±VFS =±4.096 V。

-

設置驅動放大器(ADA4945-1) VOCM。將VOCM偏置為4.096 V/2 = 2.048 V。根據數據手冊輸出共模要求檢查此電壓。

對于此應用,

其中, VOCM 在允許的范圍內。VOCM 由LTC2387-18的VOCM引腳提供。

-

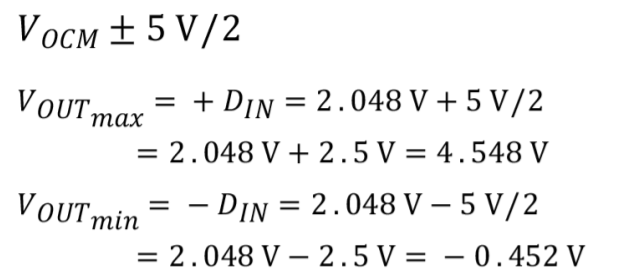

設置輸入放大器(LTC6373)的輸入和輸出限值。增益設置為 0.5,故輸出擺幅為

輸出擺幅為

對于反轉信號極性,只需簡單地反轉±DIN的值(0.452 V,?4.548 V)。

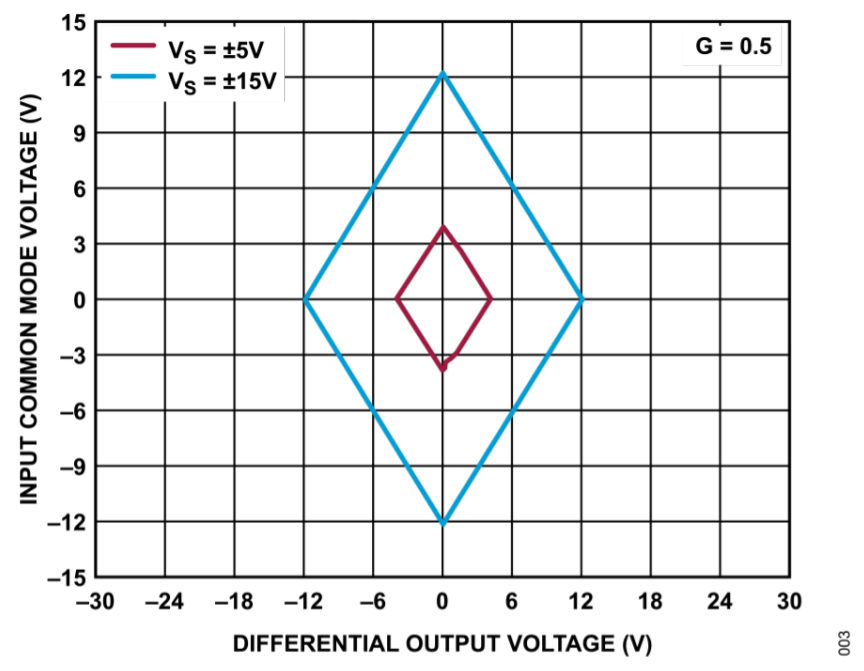

圖3顯示了增益為0.5的LTC6373的輸入和輸出擺幅限制。檢查VS = ±15 V曲線,可以看出,當輸入共模電壓為2.048 V且輸出差分電壓擺幅為±4.548 V時,LTC6373能夠輕松支持這種應用。但是,如果使用±5 V電源,LTC6373可能會在其差分輸出電壓范圍之外工作。數據手冊中提供了LTC6373所有增益下的共模范圍與差分輸出電壓的關系曲線。

LTC6373的VOCM也通過LTC2387-18的VOCM引腳設置為2.048 V,從而不必產生另一個偏置點。

圖 3. 輸入共模范圍與差分輸出電壓的關系

-

按照以下說明設置放大器增益:

對于此應用,

為獲得優化噪聲性能,ADA4945-1數據手冊建議在單位增益設置中RF和RG為499 Ω。在本例中,將RG調整為402 Ω以獲得所需的增益。RG由49.9 Ω和453 Ω電阻提供。如果THD比SNR更重要,則RG可使用2 kΩ,RF可使用1.62 kΩ,這樣THD有望提高3 dB,但SNR會降低4 dB。

-

設置驅動放大器(ADA4945-1)的輸出擺幅。由于驅動放大器的差分輸出擺幅約為VOCM,因此觀察+VFS時,運算放大器輸出就是?VFS的反向電壓。VREF (4.096 V)會用于該范圍,不過受電路增益限制,實際最大范圍為4 V。對于此應用,ADA4945-1輸出必須能夠在0.0 V至4.096 V范圍內擺動。

對于VOUTdm = +VFS,

-

根據數據手冊中的電源軌要求檢查驅動放大器(ADA4945-1)的輸出電壓擺幅。

根據 ADA4945-1 數據手冊,在 1 kΩ 負載下,

對于此應用,

-

設置驅動放大器(ADA4945-1)的輸入擺幅。

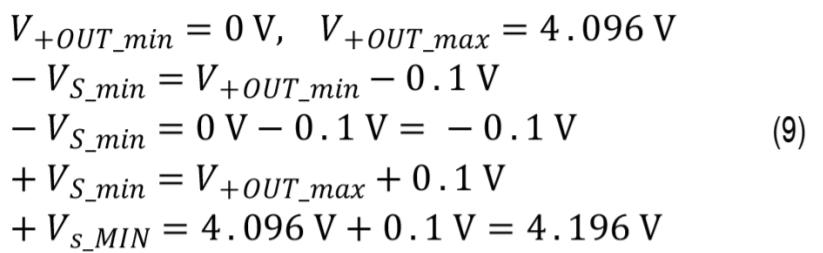

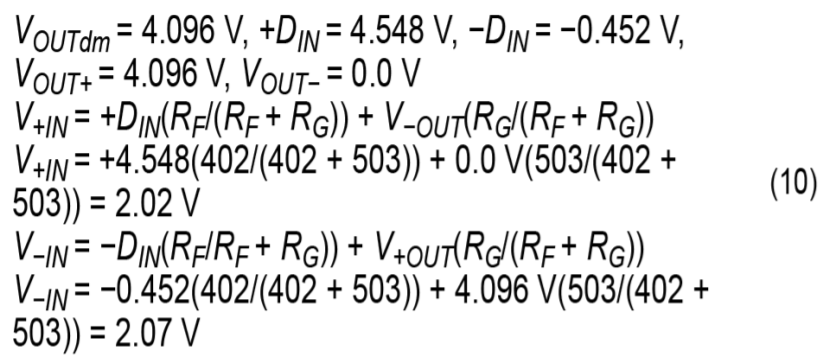

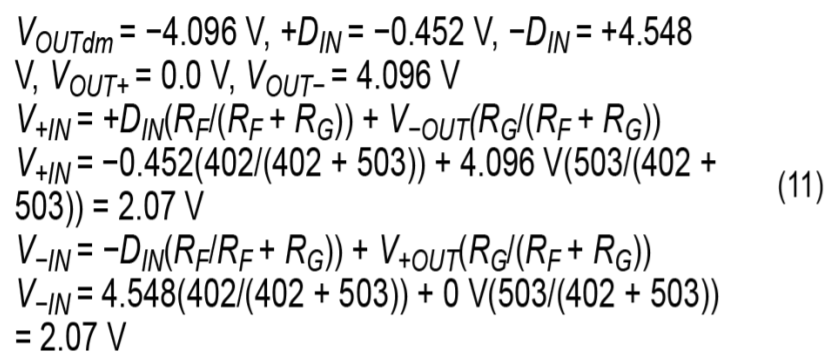

對于 VOUTdm = +VFS,輸入共模電壓計算如下:

對于 VOUTdm = ?VFS,輸入共模電壓計算如下:

對于此應用,ADA4945-1 輸入必須能夠在 2.02 V至 2.07 V 范圍內擺動。

-

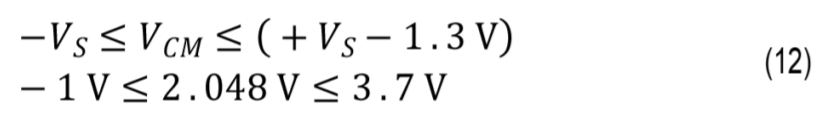

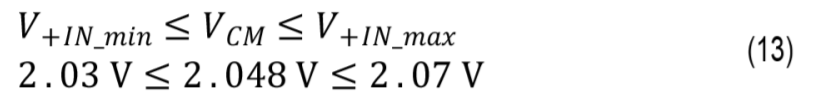

檢查驅動放大器(ADA4945-1)的輸入共模電壓。根據 ADA4945-1 數據手冊,

滿足數據手冊要求。對于此應用,

滿足應用要求。

設計仿真

精密ADC驅動器工具提供專門的仿真環境,在此環境中工程師可以快速確定驅動放大器和R-C濾波器選擇對ADC信號鏈總體性能的影響。

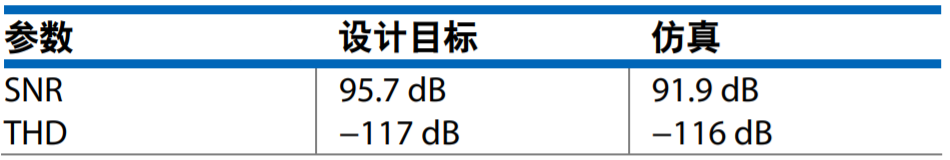

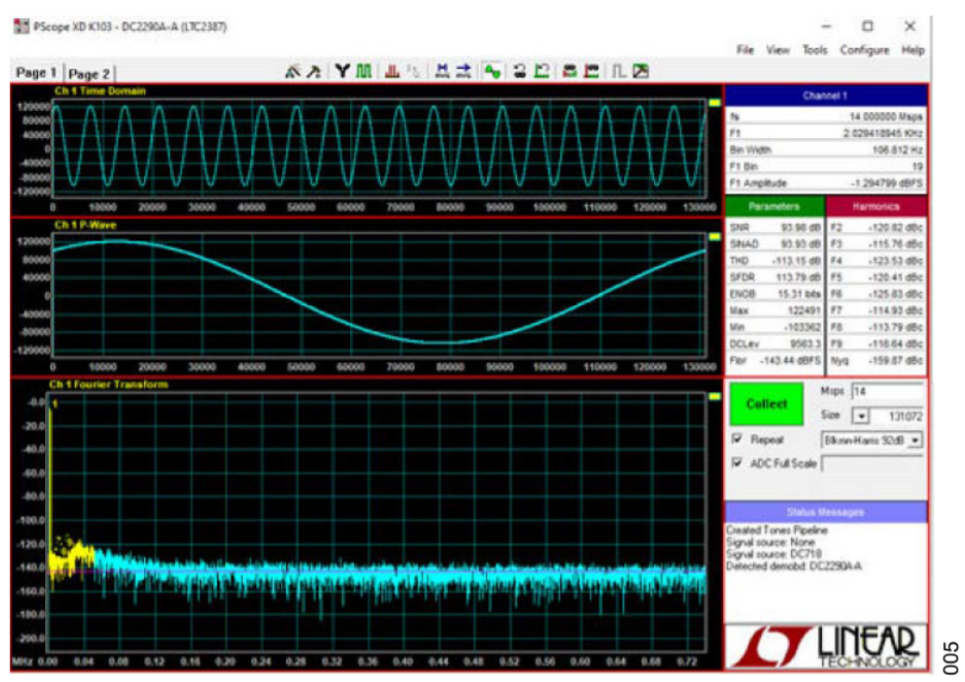

使用圖4所示的精密ADC驅動器工具估算建立時間、噪聲和THD性能。精密ADC驅動器工具目前不允許將 LTC6373 添加到原理圖中,因此僅對驅動LTC2387-18的ADA4945-1性能進行仿真。驅動器工具建議最小電源電壓為+4.6 V和?0.5 V。驅動器工具還提供警示信息,即所選驅動器會顯著降低整體噪聲性能。RF和RG是驅動器噪聲的最大來源。驅動器工具不允許如應用中所示在RF兩端添加電容。(因為高速的ADC驅動器有很多是電流反饋型放大器,在反饋電阻上增加電容會導致振蕩),但在本應用中在RF兩端增加的電容則會降低驅動器噪聲,因為ADA4945是電壓反饋型放大器。表2總結了設計目標與仿真結果。

表 2. 設計目標與仿真

圖4. 精密 ADC 驅動器工具:噪聲和 THD 結果

測量結果

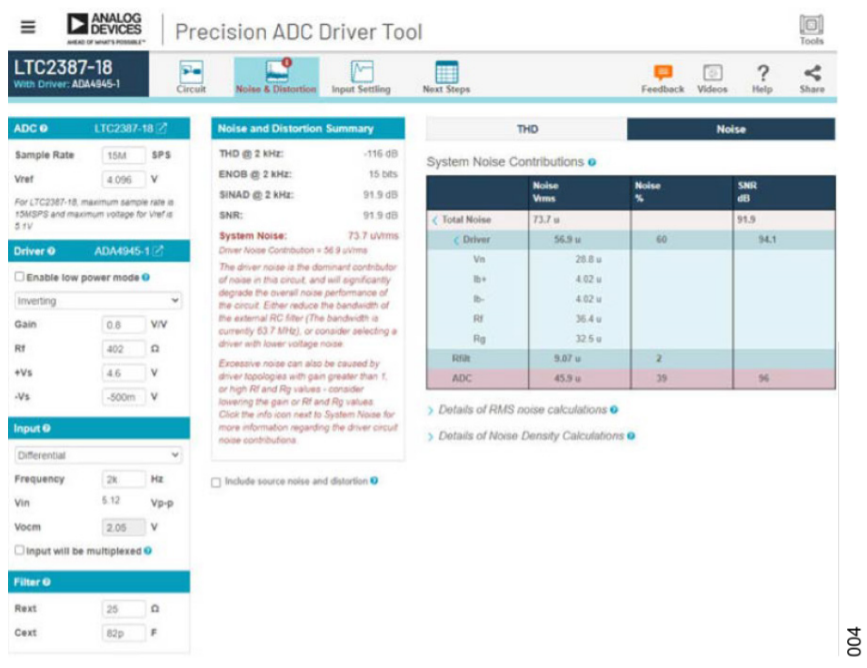

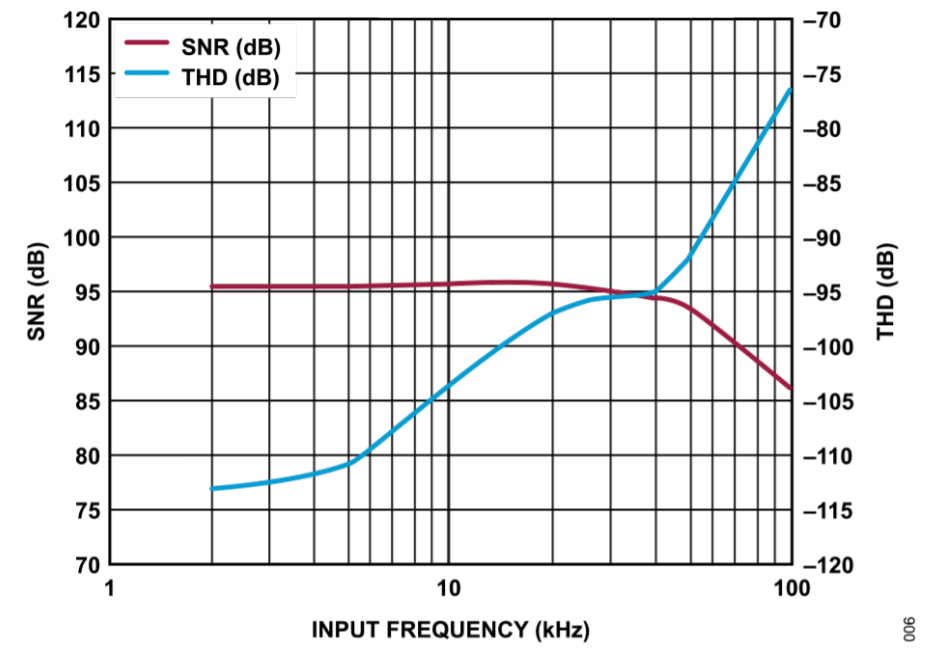

測得的ADC SNR性能比ADA4945-1數據手冊的典型值?95.7 dB低0.4 dB,THD性能比數據手冊的典型值?117 dB低3.8 dB,如圖5所示。

圖 5. 圖 1 電路的實測性能

表3總結了設計目標與仿真結果。將ADA4945-1 RG增加至2 kΩ,并將RF增加至1.62 kΩ,THD性能有望提高3 dB。根據ADC驅動器工具,這將導致SNR性能下降4 dB。THD和SNR性能哪一個更重要,須由用戶決定。所有數據均以14 MSPS的數據速率采集。在15 MSPS時,由于ADC采集周期較短,THD顯著降低。

表 3. 設計目標與測量結果

如圖6所示,當輸入頻率高于15 kHz時,THD超過?100 dB。當輸入頻率高于90 kHz時,SNR低于90 dB。該數據是在25°C時測得的。在更低或更高的溫度下,性能可能會更早地開始下降。電路處理的變化也可能導致性能開始下降的電壓不同。

圖 6. SNR 和 THD 與輸入頻率的關系

設計器件

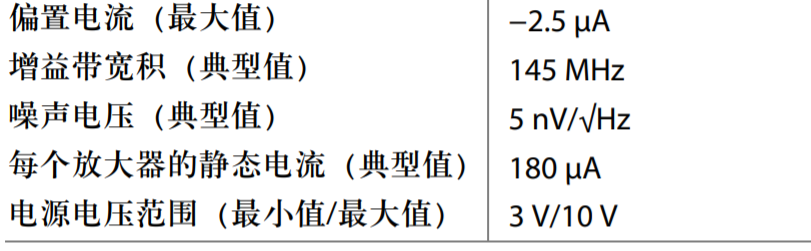

表 4. 運算放大器—ADA4945-1

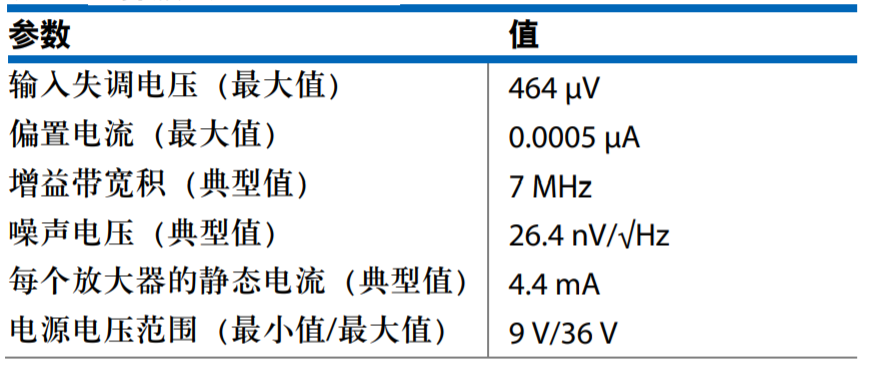

表 5. 運算放大器—LTC6373

表 6. ADC—LTC2387-18

Tips

具有全差分輸出的精密儀器儀表放大器 LTC6373 可在ADI 中國在線商城直接下單采購。現在下單,還可領取好禮一份哦,點擊查看活動詳情。

-

亞德諾

+關注

關注

6文章

4680瀏覽量

16346

原文標題:實例分享丨真雙極性輸入、全差分輸出ADC驅動器設計

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

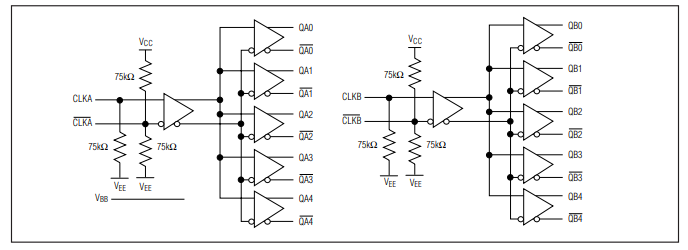

MAX9312/MAX9314雙路、1:5差分LVPECL/LVECL/HSTL時鐘和數據驅動器技術手冊

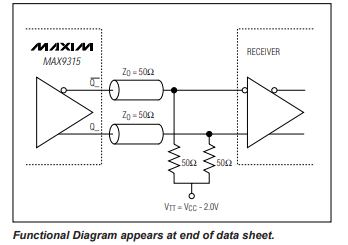

MAX9315 1:5差分LVPECL/LVECL/HSTL時鐘和數據驅動器技術手冊

THS770006 具有+6dB固定增益的高速全差分ADC驅動器放大器技術手冊

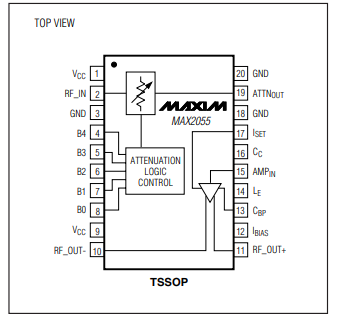

MAX2055數字控制、可變增益、差分ADC驅動器/放大器技術手冊

LT1994低噪聲、低失真全差分輸入/輸出放大器/驅動器技術手冊

實例分享丨真雙極性輸入、全差分輸出ADC驅動器設計

實例分享丨真雙極性輸入、全差分輸出ADC驅動器設計

評論