Data and ACK/NACK

正常情況

主接收機(jī)必須向從機(jī)發(fā)送傳輸結(jié)束的信號。

異常情況

- 發(fā)送到總線上的地址,卻沒有匹配的從機(jī)

- 從機(jī)處于 busy 狀態(tài)。

- 在傳輸過程中,從機(jī)獲取其不理解的數(shù)據(jù)或命令。

- 在傳輸過程中,從機(jī)無法再接收任何數(shù)據(jù)字節(jié)。

主機(jī)可以生成停止條件以中止傳輸,或生成重復(fù)啟動條件以啟動新傳輸。

Clock stretching 時鐘延展

- 時鐘延展:通過將 SCL 線保持在低電平來暫停傳輸。在 SCL 再次拉高之前,傳輸無法進(jìn)行。

- 從機(jī)通過將 SCL 線拉低,強(qiáng)制主機(jī)進(jìn)入等待狀態(tài)。

- 時鐘延展功能是可選的,不是必選的

- 時鐘延展導(dǎo)致需要更多時間來存儲接收到的字節(jié)或準(zhǔn)備另一個要傳輸?shù)淖止?jié)

- 通過延長每個時鐘低電平周期來降低總線時鐘。任何主機(jī)的速度都與該設(shè)備的內(nèi)部運(yùn)行速度相適應(yīng)。

- 在 Hs 模式下,此握手功能只能在字節(jié)級別使用

I2C 主設(shè)備始終控制著時鐘線 SCL,不論是往設(shè)備寫還是從設(shè)備讀。一般情況下,如果操作對象是 EEPROM 或者其他簡單設(shè)備而言,無所謂,但是,如果從設(shè)備是處理器,在接到主機(jī)命令后要去處理一些運(yùn)算然后得出結(jié)果返回給主機(jī)。這個時候可能造成來不及處理。怎么辦?這時,從設(shè)備會主動控制時鐘線把它拉低!直到數(shù)據(jù)準(zhǔn)備好之后再釋放時鐘線,把控制權(quán)交還給 MASTER。這也是 I2C 通信系統(tǒng)中,從機(jī)唯一能控制總線的時候!

關(guān)鍵是很多 I2C 主機(jī)不支持 clock stretching 功能,所以,無法和帶有 clock stretching 功能的從機(jī)通信!所以,各位在選擇主機(jī)器件之前,必須要注意這一點(diǎn),不然整個設(shè)計方案可能報廢,影響很大。

-

時鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132889 -

I2C

+關(guān)注

關(guān)注

28文章

1537瀏覽量

127135

發(fā)布評論請先 登錄

請問S32K148 LPI2C主控如何支持時鐘延展功能?

i2c總線介紹

i2c總線ppt(I2C總線器件應(yīng)用)

i2c總線技術(shù) (非常詳細(xì))

i2c總線的特點(diǎn)

I2C總線規(guī)范與I2C器件C51讀寫程序

I2C Guid I2C指南

I2C總線技術(shù)在彩電中的應(yīng)用

I2C總線在Linux系統(tǒng)中的驅(qū)動設(shè)計

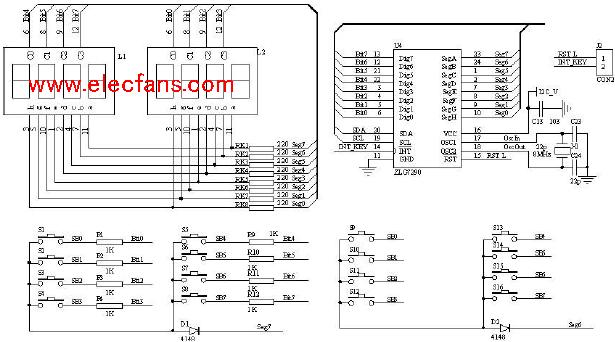

I2C總線實(shí)驗(yàn)(實(shí)時時鐘、EEPROM和ZLG7290的實(shí)驗(yàn)

硬件I2C與模擬I2C

I2C時鐘延展概念介紹

I2C時鐘延展概念介紹

評論