8Gbps及以上高速信號PCB布線建議

—來源:瑞星微RK3588 PCB設(shè)計白皮書

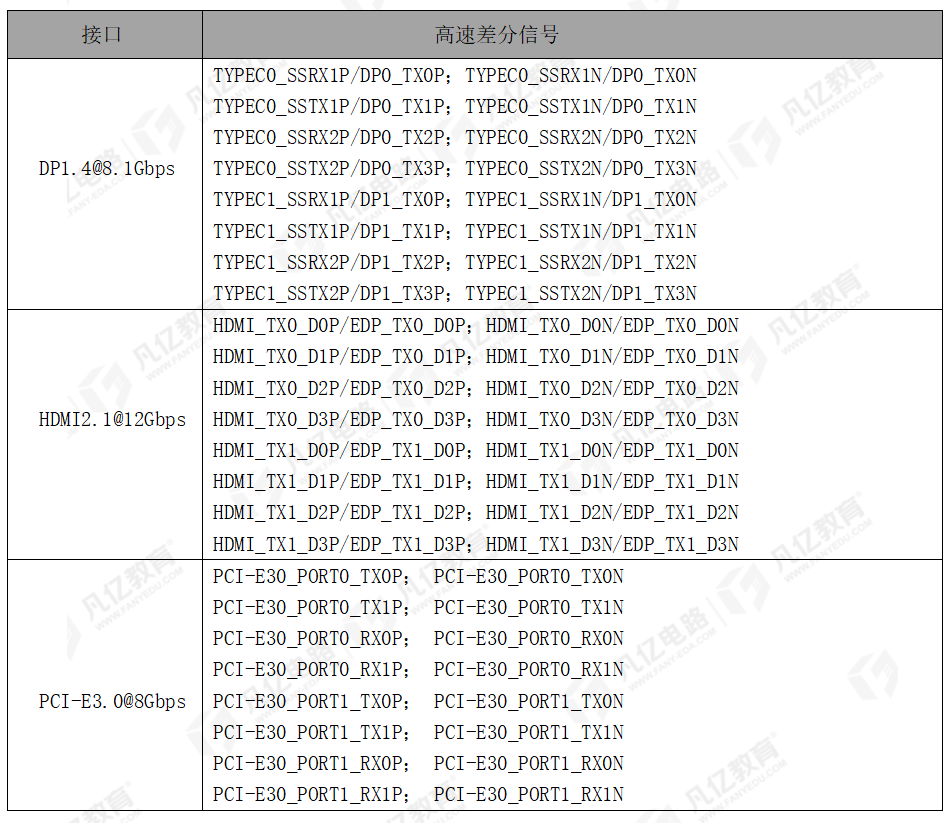

如表1-1所示,RK3588芯片以下接口的信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計要求會更嚴格,在“PCBlayout 通用布線規(guī)范”的基礎(chǔ)上,還需要根據(jù)本章節(jié)的要求來進行PCB布線設(shè)計。

表1-1 RK3588 8Gbps及以上差分信號

高速信號布線時盡量少打孔換層,換層優(yōu)先選擇兩邊是GND的層面處理。盡量收發(fā)信號布線在不同層,如果空間有限,需收發(fā)信號走線同層時,應(yīng)加大收發(fā)信號之間的布線距離。

針對以上高速信號還有如下方面的要求:

一、BGA 焊盤區(qū)域挖參考層

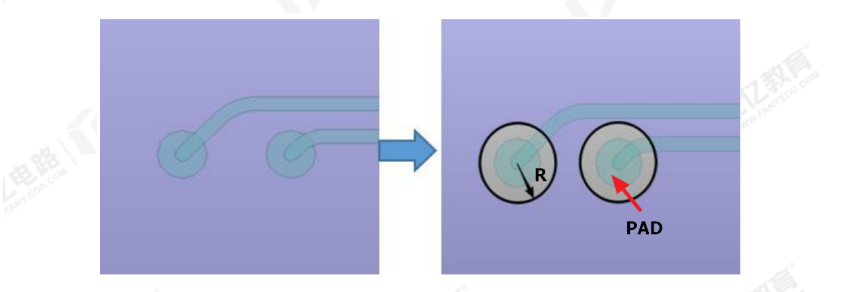

如果表1-1接口的工作速率≥ 8Gbps,建議在RK3588 BGA區(qū)域,挖掉這些信號正下方的L2層參考層以減小焊盤的電容效應(yīng)。挖空尺寸R=10mil。

如果表1-1接口的工作速率低于8Gbps,例如DP接口只工作在1.4Gbps,那么不用挖BGA區(qū)域的參考層,如圖1-1所示。

圖 1-1PAD參考層挖空示意圖

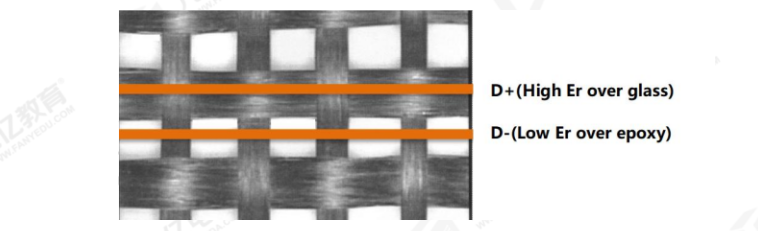

二、避免玻纖編織效應(yīng)

PCB基板是由玻璃纖維和環(huán)氧樹脂填充壓合而成。玻璃纖維的介電常數(shù)大約是6,樹脂的介電常數(shù)一般不到3。在路徑長度和信號速度方面發(fā)生的問題,主要是由于樹脂中的玻璃纖維增強編織方式引起的。較為普通的玻璃纖維編織中的玻璃纖維束是緊密絞合在一起的,因此束與束之間留出的大量空隙需要用樹脂填充,PCB中的平均導(dǎo)線寬度要小于玻璃纖維的間隔,因此一個差分對中的一條線可能有更多的部分在玻璃纖維上、更少的部分在樹脂上,另一條線則相反(樹脂上的部分比玻璃纖維上的多)。這樣會導(dǎo)致D+和D-走線的特性阻抗不同,兩條走線的時延也會不同,導(dǎo)致差分對內(nèi)的時延差進而影響眼圖的質(zhì)量。

圖1-2 差分線在玻璃纖維上的分部情況

當(dāng)表1-1接口的信號速率達到8Gbps且走線長度超過1.5inch,需謹慎處理好玻纖編織效應(yīng)。建議采用以下方式之一來避免玻纖編織效應(yīng)帶來的影響。

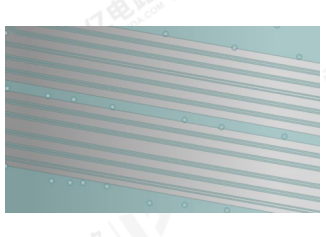

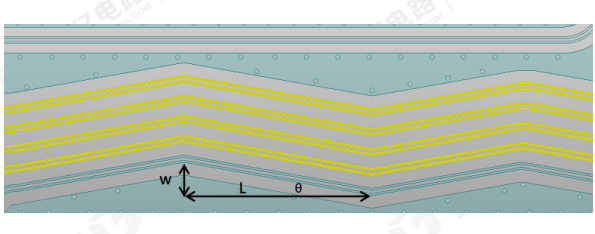

方式一:改變走線角度,如按 10°~ 35°;或PCB生產(chǎn)加工時,將板材旋轉(zhuǎn)10°以保證所有走線都不與玻纖平行,如圖1-3所示;

方式二:使用如圖1-4走線(zigzag),下圖中的W至少要大于3倍的玻纖編織間距。推薦值 W=60mil,θ=10°,L=340mil:

圖1-3 差分走線與玻纖不平行

圖1-4 差分走線布線建議

三、差分過孔建議

1、高速信號盡量少打孔換層,換層時需在信號孔旁邊添加GND過孔。地過孔數(shù)量對差分信號的信號完整性影響是不同的。無地過孔、單地過孔以及雙地過孔可依次提高差分信號的信號完整性。

2、選擇合理的過孔尺寸。對于多層一般密度的PCB設(shè)計來說,選用0.25mm/0.51mm/0.91mm(鉆孔/焊盤/POWER隔離區(qū))的過孔較好;對于一些高密度的PCB也可以使用0.20mm/0.46mm/0.86mm 的過孔,也可以嘗試盲埋孔設(shè)計;

3、過孔中心距的變化對差分信號的信號完整性影響是不同的。對于差分信號,過孔中心距過大或過小均會對信號完整性產(chǎn)生不利影響。

4、如果表1-1接口的工作速率≥8Gbps,那么這些接口差分對的過孔尺寸建議根據(jù)實際疊層進行仿真優(yōu)化。

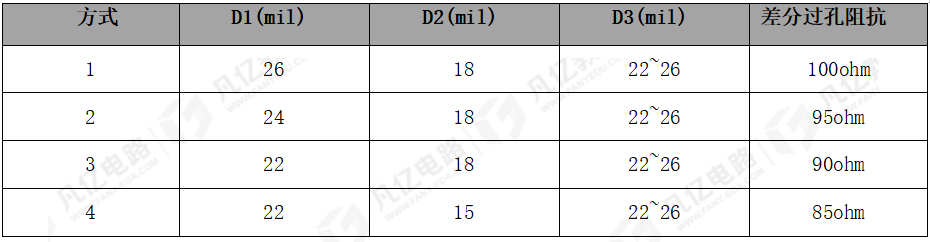

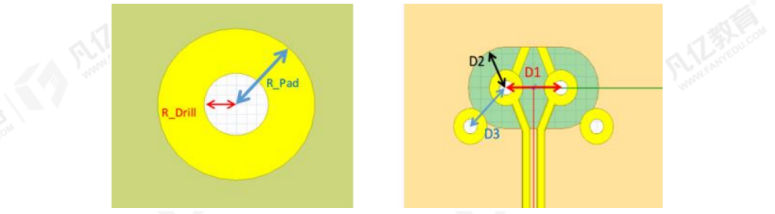

以下給出基于EVB一階HDI疊層的過孔參考尺寸:

R_Drill=0.1mm (鉆孔半徑)

R_Pad=0.2mm (過孔焊盤半徑)

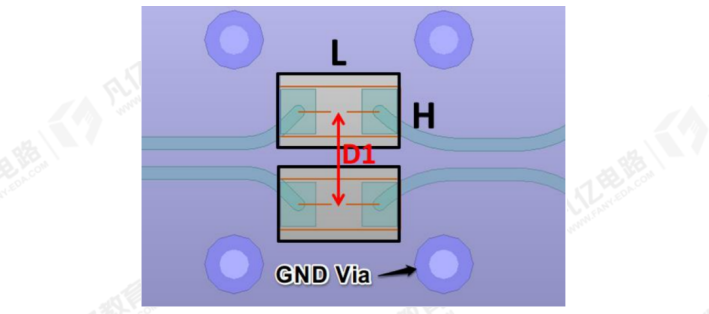

D1:差分過孔中心間距

D2:表層到底層的反焊盤尺寸

D3:信號過孔與回流地過孔的中心間距

表1-2差分過孔的參考尺寸

圖1-5 差分過孔打孔建議

四、耦合電容優(yōu)化建議

1、耦合電容的放置,按照設(shè)計指南要求放置。如果沒有設(shè)計指南時,若信號是IC到IC,耦合電容靠近接收端放置;若信號是IC到連接器,耦合電容請靠近連接器放置;

2、盡可能選擇小的封裝尺寸,減小阻抗不連續(xù);

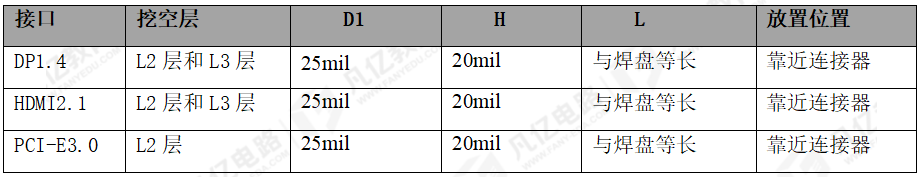

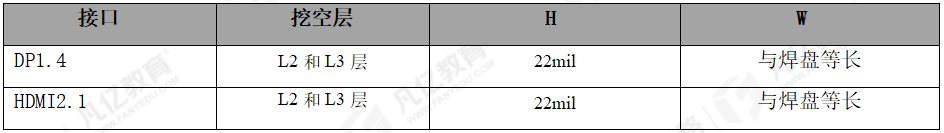

3、如果表 1-1接口的信號工作速率≥8Gbps,那么這些接口的差分隔直電容建議按如下方式進行優(yōu)化。 1)根據(jù)接口選擇挖空一層或者兩層地平面,如果挖空電容焊盤正下方L2地參考層,需要隔層參考,即L3 層要為地參考層;

2)如果挖空L2和L3地參考層,那么L4層要為地參考層。挖空尺寸需根據(jù)實際疊層通過仿真確定;以下給出基于EVB一階HDI疊層的參考尺寸。

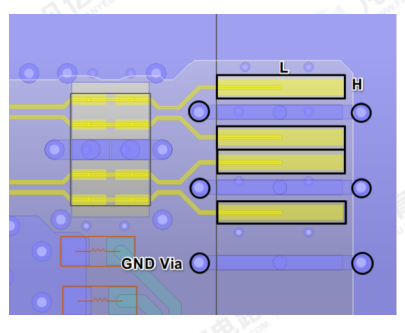

表1-3耦合電容焊盤挖空尺寸參考值

D1:差分耦合電容之間的中心距;L:挖空長度; H:挖空寬度。

4、在耦合電容四周打4個地通孔以將 L2~L4 層的地參考層連接起來,如圖1-6所示。

圖1-6 耦合電容的挖空與GND孔的放置

五、ESD優(yōu)化建議

1、ESD保護器件的寄生電容必須足夠低,以允許高速信號傳輸而不會降級。

2、ESD需放置在被保護的IC之前,但盡量與連接器/觸點PCB側(cè)盡量靠近;放置在與信號線串聯(lián)任何電阻之前;放置在包含保險絲在內(nèi)的過濾或調(diào)節(jié)器件之前。

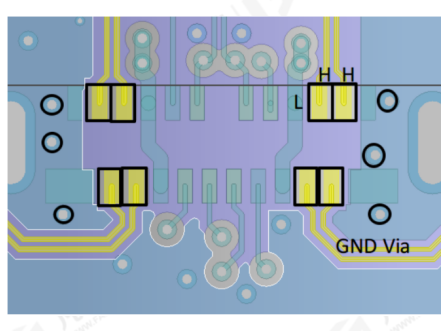

3、如果表1-1的接口的信號工作速率≥8Gbps,那么這些接口的差分對ESD器件建議按以下方式優(yōu)化。挖空ESD焊盤正下方L2和L3地參考層,L4層作為隔層參考層,需要為地平面。挖空尺寸需結(jié)合 ESD型號并根據(jù)實際疊層通過仿真確定。

以下給出基于基于EVB一階HDI疊層的所用 ESD型號為ESD73034D 的參考尺寸。

表1-4 ESD器件焊盤挖空參考尺寸

4、同時在每個ESD四周打 4 個地通孔以將 L2~L4 層的地參考層連接起來,如圖1-7所示。

圖1-7 ESD布線情況示意

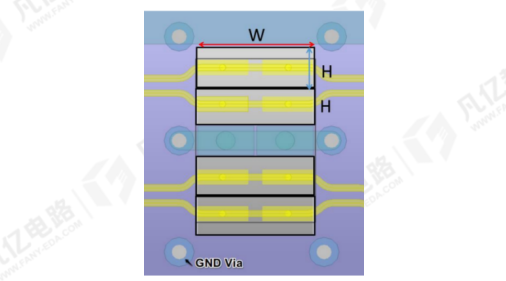

六、連接器優(yōu)化建議

1、在連接器內(nèi)走線要中心出線。如果高速信號在連接器有一端信號沒有與GND相鄰PIN時,設(shè)計時應(yīng)在其旁邊加GND孔。

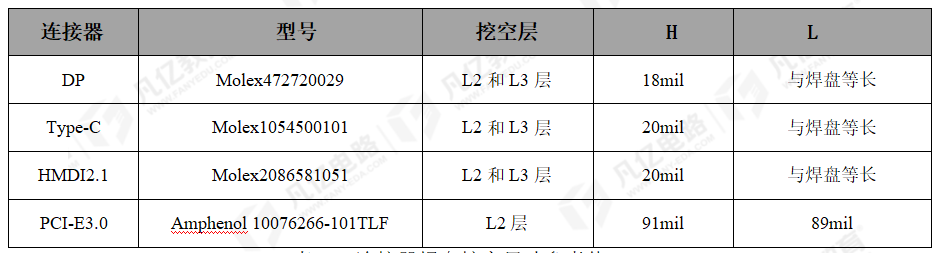

2、如果表1-1接口的信號工作速率≥8Gbps,那么這些接口的連接器要能符合相應(yīng)的標準要求(如HDMI2.1/DP1.4/PCI-E3.0協(xié)議標準)。推薦使用這些廠商的連接器:Molex、Amphenol、HRS等等。

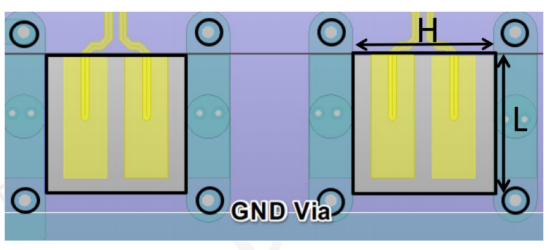

3、根據(jù)接口選擇挖空一層或者兩層地平面,如果挖空連接器焊盤正下方的L2地參考層,需隔層參考,即L3層要作為地參考層;如果挖空L2和L3的地參考層,那么L4層需要為地平面,作為隔層參考層。挖空尺寸需結(jié)合連接器型號并根據(jù)實際疊層通過仿真確定。

4、建議在連接器的每個地焊盤各打2個地通孔,且地孔要盡可能靠近焊盤。

以下給出基于EVB一階HDI疊層的挖空參考尺寸。

表1-5連接器焊盤挖空尺寸參考值

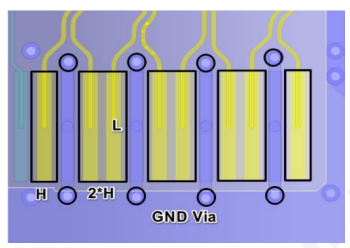

連接器推薦布線方式:

圖1-8 DP連接器布線示意

圖1-9 Type-C連接器布線示意

圖1-10 HDMI2.1連接器布線示意

圖1-11 PCI-E3.0連接器布線示意

聲明: 本文轉(zhuǎn)載自瑞星微,如涉及作品內(nèi)容、版權(quán)和其它問題,請于聯(lián)系工作人員微(prrox66),我們將在第一時間和您對接刪除處理!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207-

pcb

+關(guān)注

關(guān)注

4354文章

23430瀏覽量

406946

原文標題:8Gbps及以上高速信號PCB布線建議

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

高速PCB布局/布線的原則

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

高速PCB板的電源布線設(shè)計

建議收藏,這31條PCB設(shè)計布線技巧

聊聊高速PCB設(shè)計100Gbps信號的仿真

104條關(guān)于PCB布局布線的小技巧

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

高速PCB信號完整性分析及應(yīng)用

高速ADC PCB布局布線技巧分享

DS80PCI810低功耗8Gbps 8通道線性中繼器數(shù)據(jù)表

SN75LVPE802雙通道8Gbps SATA Expres均衡器和轉(zhuǎn)接驅(qū)動器數(shù)據(jù)表

8Gbps及以上高速信號PCB布線建議

8Gbps及以上高速信號PCB布線建議

評論