chiplet和cowos的關系

Chiplet和CoWoS是現(xiàn)代半導體工業(yè)中的兩種關鍵概念。兩者都具有很高的技術含量和經(jīng)濟意義。本文將詳細介紹Chiplet和CoWoS的概念、優(yōu)點、應用以及兩者之間的關系。

一、Chiplet的概念和優(yōu)點

Chiplet是指將一個完整的芯片分解為多個功能小芯片的技術。簡單來說,就是將一個復雜的芯片分解為多個簡單的功能芯片,再通過互聯(lián)技術將它們組合在一起,形成一個整體的解決方案。

Chiplet技術的優(yōu)點主要有以下幾點:

1. 提高芯片的靈活性。芯片中的各個模塊可以獨立升級,從而提高芯片的靈活性和可維護性。

2. 降低芯片設計的難度。芯片優(yōu)化和設計變得更加容易,設計團隊可以將自己的核心專業(yè)領域內的復雜問題分解成簡單的部分進行解決。

3. 降低制造成本。芯片的制造分解成多個芯片,每個小芯片的生產(chǎn)成本會比整個芯片的生產(chǎn)成本低。

4. 提高生產(chǎn)效率。芯片生產(chǎn)分解成多個小芯片后,每個模塊的制造可以并行進行,從而縮短生產(chǎn)周期。

二、CoWoS的概念和優(yōu)點

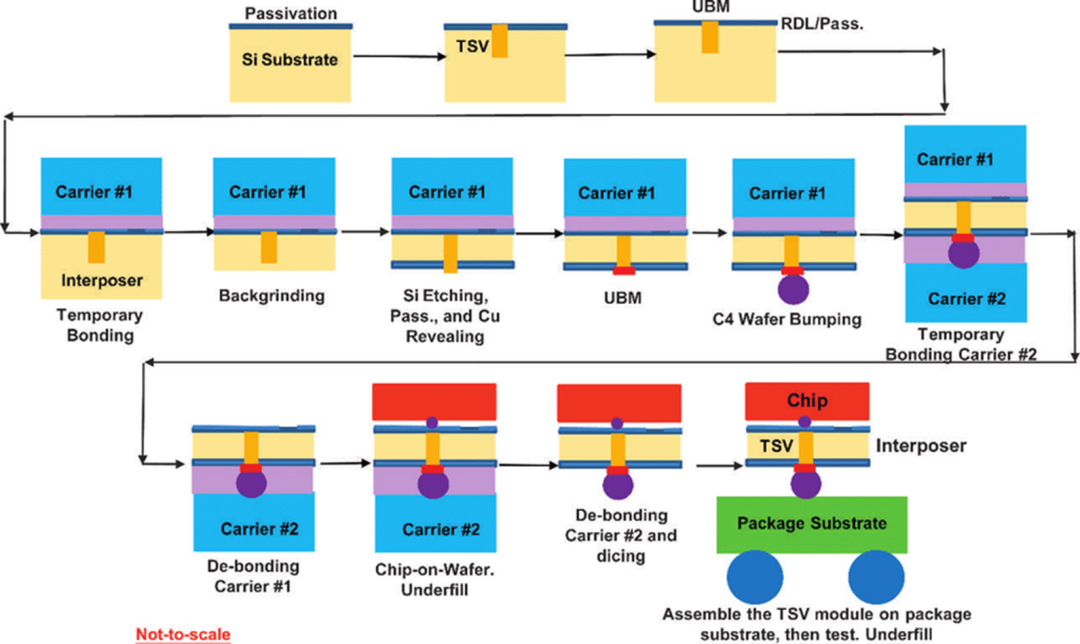

CoWoS(Chip On Wafer On Substrate)是一種三維堆疊技術。顧名思義,便是通過將多個芯片堆疊在晶圓上形成一個整體的芯片。具體而言,通過將低功耗芯片、高性能芯片和其他功能芯片組合在一起,實現(xiàn)芯片級封裝。

CoWoS技術的優(yōu)點主要有以下幾點:

1. 提高芯片的集成度。通過堆疊多個芯片,可以實現(xiàn)芯片級封裝,使整個芯片結構更加緊湊。

2. 降低芯片功耗。芯片的多層堆疊可以實現(xiàn)更好的功耗控制,從而提高芯片的能效比。

3. 提高芯片工作速度。通過使用高速通信總線,可以實現(xiàn)堆疊芯片之間的高速數(shù)據(jù)傳輸,從而提高芯片的工作速度。

4. 提高芯片的穩(wěn)定性。采用三維堆疊的技術可以提高芯片的穩(wěn)定性,降低故障率。

三、Chiplet和CoWoS的應用

Chiplet和CoWoS技術在現(xiàn)代半導體工業(yè)中有著廣泛的應用。其中,Chiplet技術主要應用于AI芯片、網(wǎng)絡芯片、計算芯片、存儲芯片等領域,主要的目的是提高芯片的靈活性和可維護性,同時降低芯片設計和制造的難度和成本。CoWoS技術主要應用于高性能計算、圖像處理、高速通訊、高密度存儲和人工智能等領域,主要目的是降低芯片功耗,提高芯片的集成度和工作速度,提高芯片的穩(wěn)定性。

四、Chiplet和CoWoS的關系

Chiplet和CoWoS是兩種不同的技術,在不同的領域有不同的應用。但是,兩者都是為了提高芯片的靈活性、可維護性和性能而產(chǎn)生的技術。Chiplet技術通過分解芯片的復雜性,使芯片的設計和制造更加簡單易行;而CoWoS技術則是通過將多個芯片堆疊在一起實現(xiàn)芯片級封裝,從而提高芯片的集成度和工作速度。

綜合來看,Chiplet和CoWoS兩種技術都具有很高的技術含量和經(jīng)濟意義,都是現(xiàn)代半導體工業(yè)中的重要組成部分。兩者之間并不存在絕對的等價關系,而是各自的應用范圍和優(yōu)點有所不同。在今后的半導體工業(yè)中,Chiplet和CoWoS的發(fā)展將繼續(xù)不斷地推動著芯片技術的飛速發(fā)展。

-

存儲器

+關注

關注

38文章

7643瀏覽量

166847 -

芯片設計

+關注

關注

15文章

1077瀏覽量

55552 -

CoWoS

+關注

關注

0文章

154瀏覽量

11023 -

AI芯片

+關注

關注

17文章

1978瀏覽量

35783 -

chiplet

+關注

關注

6文章

453瀏覽量

12933

發(fā)布評論請先 登錄

Chiplet與先進封裝設計中EDA工具面臨的挑戰(zhàn)

日月光擴大CoWoS先進封裝產(chǎn)能

黃仁勛:對CoWoS 產(chǎn)能需求仍增加但轉移為CoWoS-L

黃仁勛:英偉達CoWoS產(chǎn)能將大幅增加

先進封裝行業(yè):CoWoS五問五答

機構:臺積電CoWoS今年擴產(chǎn)至約7萬片,英偉達占總需求63%

解鎖Chiplet潛力:封裝技術是關鍵

CoWoS先進封裝技術介紹

Chiplet技術有哪些優(yōu)勢

明年全球CoWoS產(chǎn)能需求將增長113%

潤欣科技與奇異摩爾簽署CoWoS-S封裝服務協(xié)議

CoWoS工藝流程說明

IMEC組建汽車Chiplet聯(lián)盟

chiplet和cowos的關系

chiplet和cowos的關系

評論