閾值電壓對傳播延遲和躍遷延遲的影響:

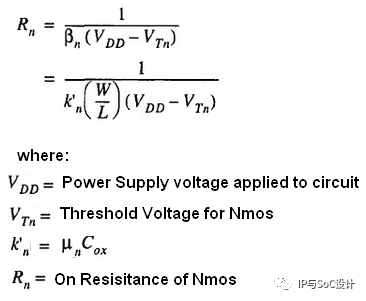

如果你能看到下面的方程式-我相信你可以很容易地弄清楚閾值電壓對電池延遲的影響。(注:以下電阻公式是關(guān)于NMOS的。您也可以為PMOS導(dǎo)出類似的公式(只需將下標(biāo)“n”替換為“p”)。

從上面的方程我們有以下幾點(diǎn)

MOS的導(dǎo)通電阻與“VDD-VTn”(其中VTn是閾值電壓)成反比。

對于恒定的VDD,減小閾值電壓(低VTn)增加“VDD-VTn”。

增大“VDD-VTn”意味著減小“導(dǎo)通電阻”“ Rn.

減小Rn,則RC減小。

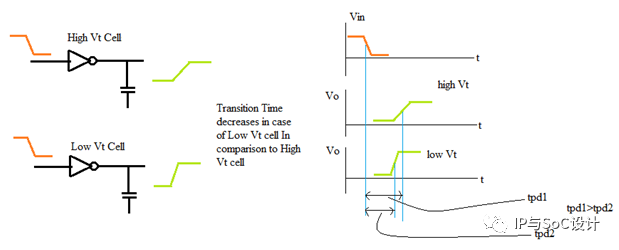

意味著大的驅(qū)動(dòng)能力(源電流或吸收電流的能力)

減少對輸出負(fù)載(電容)充電的時(shí)間(由驅(qū)動(dòng)?xùn)艠O的源極/漏極電容、導(dǎo)線的布線電容和驅(qū)動(dòng)?xùn)艠O的柵極電容組成)**

意味著“門A的輸出轉(zhuǎn)換時(shí)間”和“門B的輸入轉(zhuǎn)換時(shí)間”減少。

減少轉(zhuǎn)換時(shí)間意味著減少傳播時(shí)間。

所以我們可以說。。。

“使用低Vt單元可以減少延遲,但所付出的代價(jià)是高泄漏功率”

直接影響是低Vt單元通常更易泄漏,即泄漏功率增加。

如果你還有什么疑惑,下面的圖應(yīng)該能澄清你的疑惑。

我希望上面的圖表可以消除你對閾值電壓對延遲的影響的疑慮。

在下一篇文章中,我們將總結(jié)/列出所有修復(fù)設(shè)置和保持違規(guī)的方法。

審核編輯:湯梓紅

-

NMOS

+關(guān)注

關(guān)注

3文章

359瀏覽量

35544 -

導(dǎo)通電阻

+關(guān)注

關(guān)注

0文章

390瀏覽量

20181 -

PMOS

+關(guān)注

關(guān)注

4文章

268瀏覽量

30473 -

閾值電壓

+關(guān)注

關(guān)注

0文章

97瀏覽量

51876

原文標(biāo)題:博文速遞:Effect of Threshold voltage

文章出處:【微信號:IP與SoC設(shè)計(jì),微信公眾號:IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

解答74HC14中正向閾值電壓和負(fù)向閾值電壓是什么/電壓為多少

MOS管閾值電壓的問題

導(dǎo)線的傳播延遲與其周圍介質(zhì)關(guān)系

閾值電壓的計(jì)算

allegro軟件的絕對傳輸延遲是什么,絕對傳輸延遲應(yīng)該怎么設(shè)置呢?

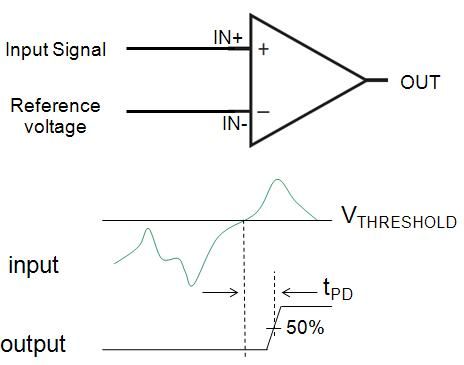

影響比較器傳播延遲測量的參數(shù)

EDA探索之控制閾值電壓

控制閾值電壓

NMOS晶體管的閾值電壓公式 nmos晶體管的閾值電壓與哪些因素有關(guān)

影響MOSFET閾值電壓的因素

什么是MOS管亞閾值電壓?MOSFET中的閾值電壓是如何產(chǎn)生的?

淺談?dòng)绊慚OSFET閾值電壓的因素

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

閾值電壓對傳播延遲和躍遷延遲的影響

閾值電壓對傳播延遲和躍遷延遲的影響

評論