技術(shù)工藝:晶圓級封裝的關(guān)鍵工藝——硅通孔

半導(dǎo)體封裝的四個(gè)主要作用,包括機(jī)械保護(hù)、電氣連接、機(jī)械連接和散熱。封裝的形狀和尺寸各異,保護(hù)和連接脆弱集成電路的方法也各不相同。

半導(dǎo)體封裝的分類

半導(dǎo)體封裝方法,大致可以分為兩種:傳統(tǒng)封裝和晶圓級(Wafer-Level)封裝。傳統(tǒng)封裝首先將晶圓切割成芯片,然后對芯片進(jìn)行封裝;而晶圓級封裝則是先在晶圓上進(jìn)行部分或全部封裝,之后再將其切割成單件。

晶圓級封裝方法可進(jìn)一步細(xì)分為四種不同類型:

1)晶圓級芯片封裝(WLCSP),可直接在晶圓頂部形成導(dǎo)線和錫球(Solder Balls),無需基板;

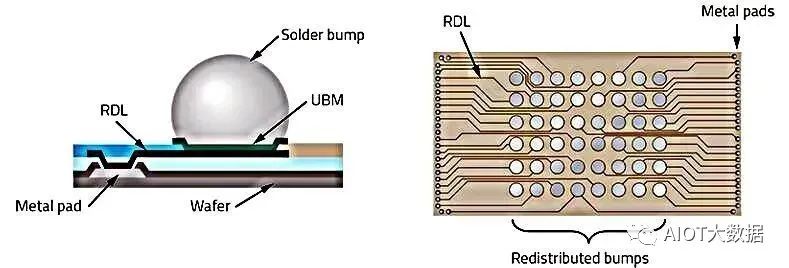

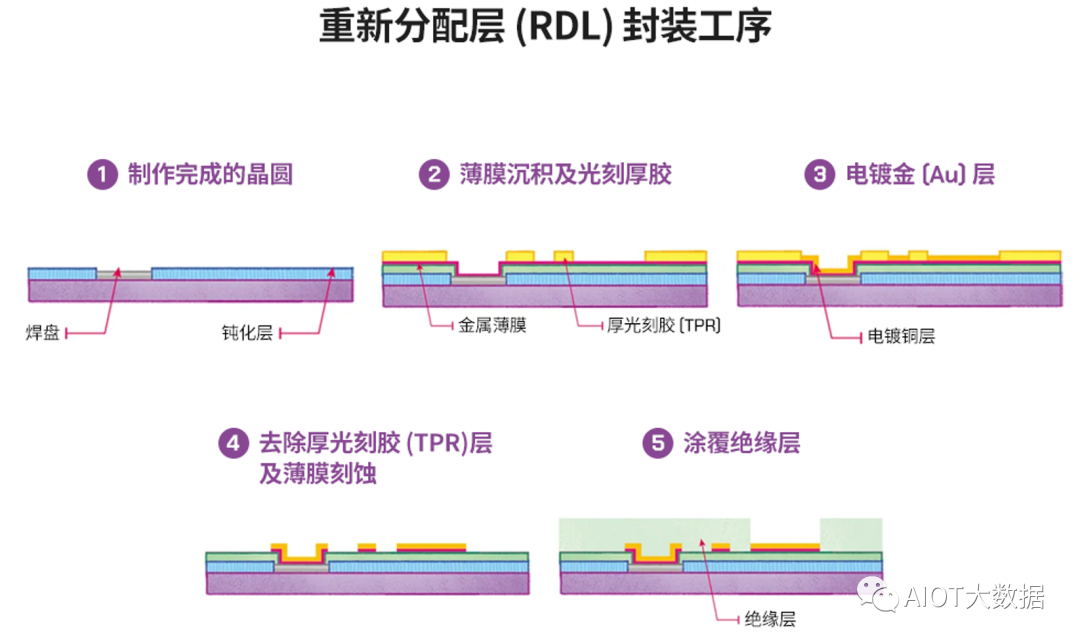

2)重新分配層(RDL),使用晶圓級工藝重新排列芯片上的焊盤位置1,焊盤與外部采取電氣連接方式;

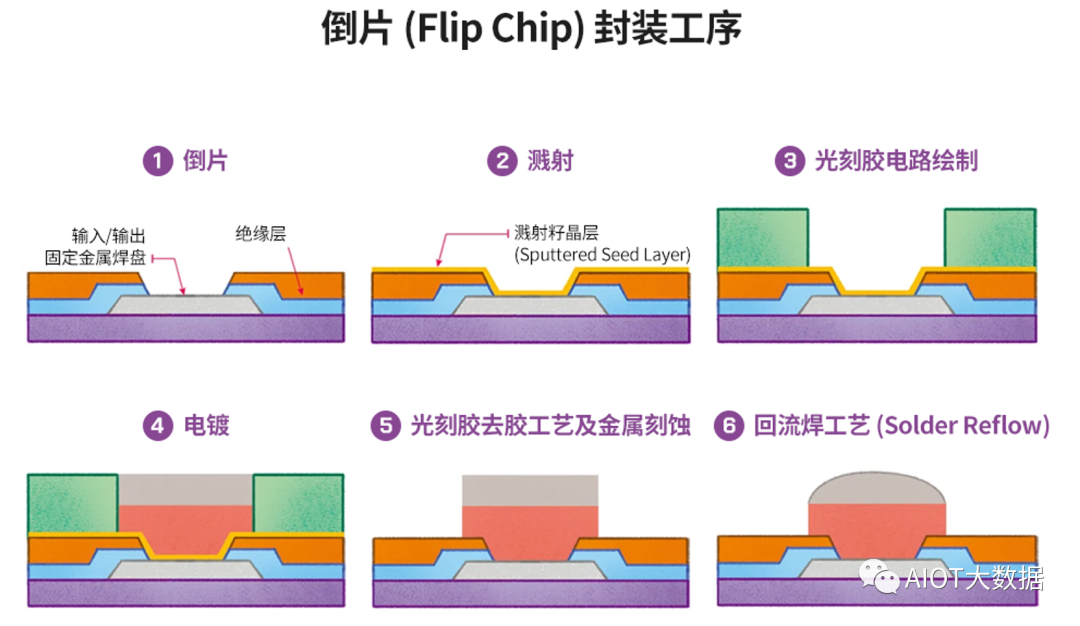

3)倒片(Flip Chip)封裝,在晶圓上形成焊接凸點(diǎn)2進(jìn)而完成封裝工藝;

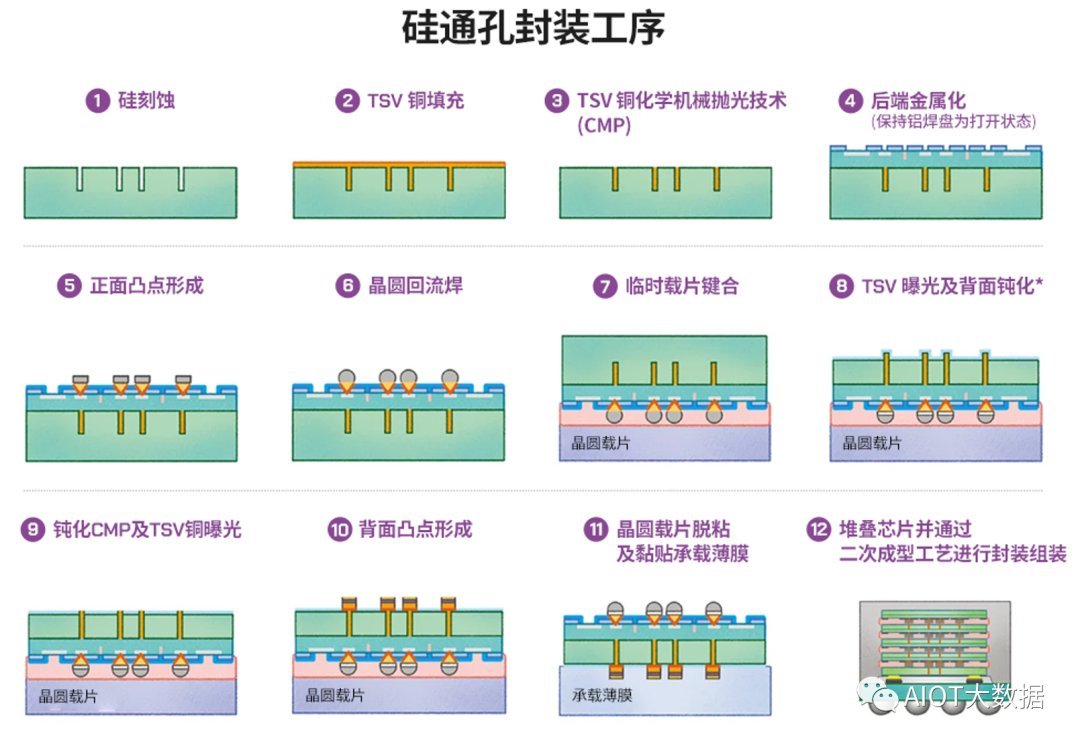

4)硅通孔(TSV)封裝,通過硅通孔技術(shù),在堆疊芯片內(nèi)部實(shí)現(xiàn)內(nèi)部連接。

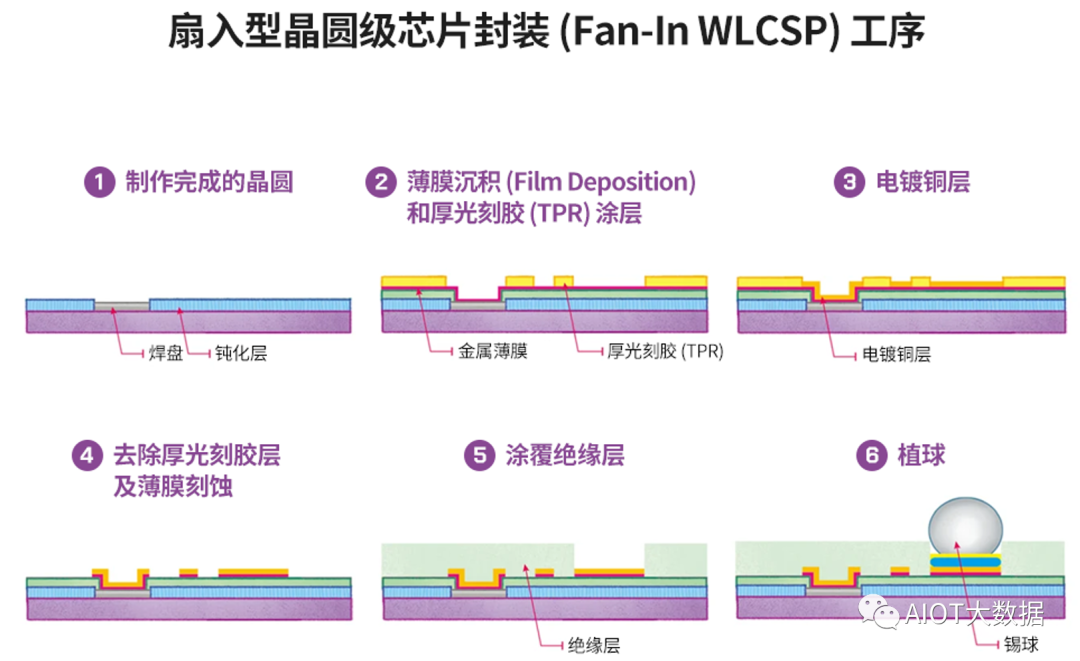

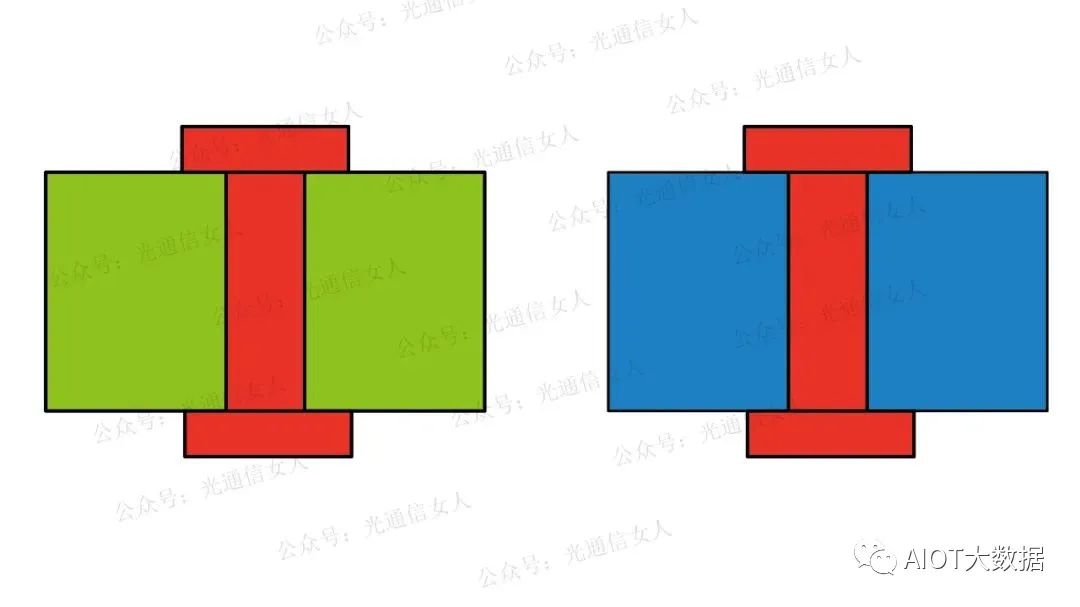

晶圓級芯片封裝分為扇入型WLCSP和扇出型WLCSP。

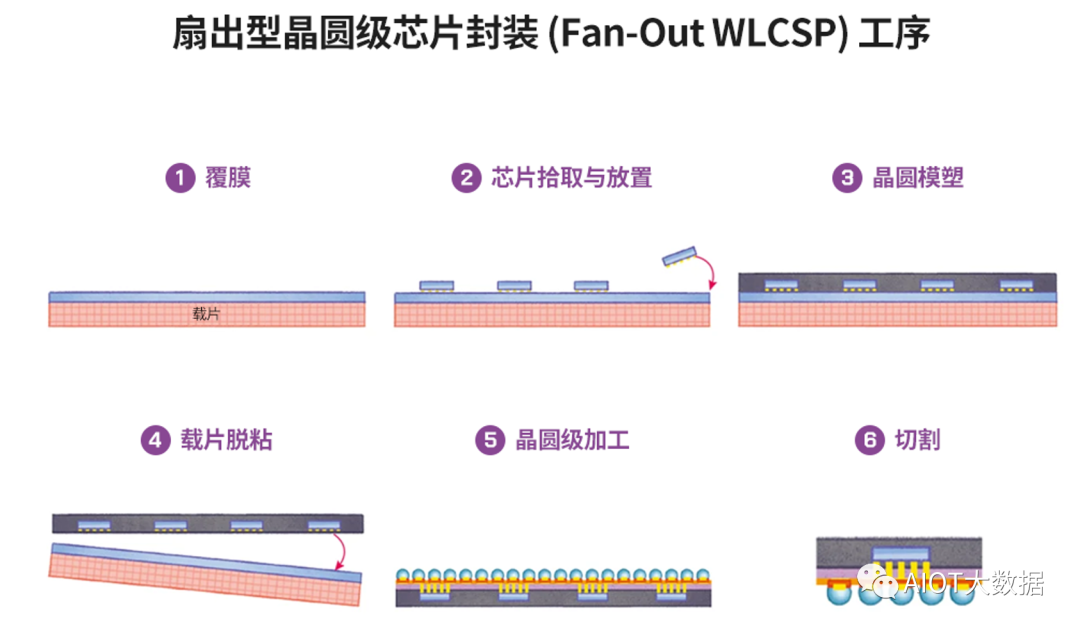

扇入型WLCSP工藝將導(dǎo)線和錫球固定在晶圓頂部,而扇出型WLCSP則將芯片重新排列為模塑3晶圓。這樣做是為了通過晶圓級工藝形成布線層,并將錫球固定在比芯片尺寸更大的封裝上。

扇入型 (Fan-In) WLCSP (Wafer Level Chip Scale Package)

晶圓級芯片封裝的大多數(shù)制造過程都是在晶圓上完成的,是晶圓級封裝的典型代表。然而,從廣義上講,晶圓級封裝還包括在晶圓上完成部分工藝的封裝,例如,使用重新分配層、倒片技術(shù)和硅通孔技術(shù)的封裝。在扇入型WLCSP和扇出型WLCSP中,“扇”是指芯片尺寸。扇入型WLCSP的封裝布線、絕緣層和錫球直接位于晶圓頂部。與傳統(tǒng)封裝方法相比,扇入型WLCSP既有優(yōu)點(diǎn),也有缺點(diǎn)。

在扇入型WLCSP中,封裝尺寸與芯片尺寸相同,都可以將尺寸縮至最小。此外,扇入型WLCSP的錫球直接固定在芯片上,無需基板等媒介,電氣傳輸路徑相對較短,因而電氣特性得到改善。而且,扇入型WLCSP無需基板和導(dǎo)線等封裝材料,工藝成本較低。這種封裝工藝在晶圓上一次性完成,因而在裸片(Net Die,晶圓上的芯片)數(shù)量多且生產(chǎn)效率高的情況下,可進(jìn)一步節(jié)約成本。

扇入型WLCSP的缺點(diǎn)在于,因其采用硅(Si)芯片作為封裝外殼,物理和化學(xué)防護(hù)性能較弱。正是由于這個(gè)原因,這些封裝的熱膨脹系數(shù)與其待固定的PCB基板的熱膨脹系數(shù)5存在很大差異。受此影響,連接封裝與PCB基板的錫球會(huì)承受更大的應(yīng)力,進(jìn)而削弱焊點(diǎn)可靠性。

存儲器半導(dǎo)體采用新技術(shù)推出同一容量的芯片時(shí),芯片尺寸會(huì)產(chǎn)生變化,扇入型WLCSP的另一個(gè)缺點(diǎn)就無法使用現(xiàn)有基礎(chǔ)設(shè)施進(jìn)行封裝測試。此外,如果封裝錫球的陳列尺寸大于芯片尺寸,封裝將無法滿足錫球的布局要求,也就無法進(jìn)行封裝。而且,如果晶圓上的芯片數(shù)量較少且生產(chǎn)良率較低,則扇入型WLCSP的封裝成本要高于傳統(tǒng)封裝。

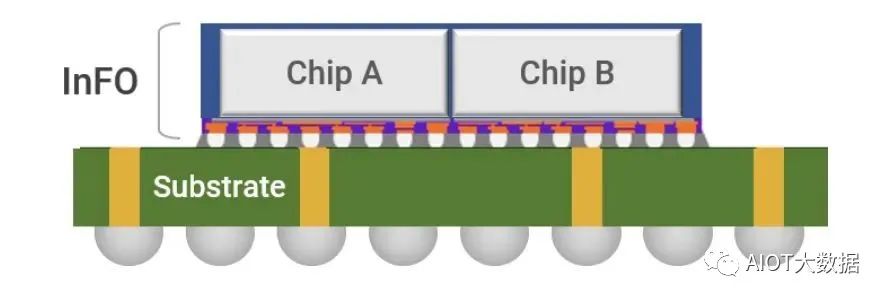

扇出型WLCSP

扇出型WLCSP既保留了扇入型WLCSP的優(yōu)點(diǎn),又克服了其缺點(diǎn)。

扇入型WLCSP的所有封裝錫球都位于芯片表面,而扇出型WLCSP的封裝錫球可以延伸至芯片以外。在扇入型WLCSP中,晶圓切割要等到封裝工序完成后進(jìn)行。因此,芯片尺寸必須與封裝尺寸相同,且錫球必須位于芯片尺寸范圍內(nèi)。在扇出型WLCSP中,芯片先切割再封裝,切割好的芯片排列在載體上,重塑成晶圓。在此過程中,芯片與芯片之間的空間將被填充環(huán)氧樹脂模塑料,以形成晶圓。然后,這些晶圓將從載體中取出,進(jìn)行晶圓級處理,并被切割成扇出型WLCSP單元。

除了具備扇入型WLCSP的良好電氣特性外,扇出型WLCSP還克服了扇入型WLCSP的一些缺點(diǎn)。這其中包括:無法使用現(xiàn)有基礎(chǔ)設(shè)施進(jìn)行封裝測試;封裝錫球陳列尺寸大于芯片尺寸導(dǎo)致無法進(jìn)行封裝;以及因封裝不良芯片導(dǎo)致加工成本增加等問題。得益于上述優(yōu)勢,扇出型WLCSP在近年來的應(yīng)用范圍越來越廣泛。

WLCSP 封裝流程

晶圓片級芯片規(guī)模封裝(Wafer Level Chip Scale Packaging,簡稱WLCSP),即晶圓級芯片封裝方式,不同于傳統(tǒng)的芯片封裝方式(先切割再封測,而封裝后至少增加原芯片20%的體積),此種最新技術(shù)是先在整片晶圓上進(jìn)行封裝和測試,然后才切割成一個(gè)個(gè)的IC顆粒,因此封裝后的體積即等同IC裸晶的原尺寸。

WLCSP封裝的大致流程:(一般分為Bumping,CP test,WLCSP三個(gè)階段)

Bumping階段

1. Customer Wafer

這是第一道工序,主要是將從晶圓廠收到的wafer經(jīng)過Pre-Clean + SRD預(yù)處理,然后使用O2 Plasma等離子清洗并烘干,目的是去除來料wafer表面的雜質(zhì)。

2. PI coating

PI是一層聚合物薄膜層,可以加強(qiáng)芯片的passivation,起到應(yīng)力緩沖的作用。做法是將預(yù)處理后的wafer置于設(shè)備吸盤上,wafer正面朝上,在wafer正面噴涂高度光敏感性的光刻膠,設(shè)備吸盤高速旋轉(zhuǎn),使光刻膠均勻噴涂在整個(gè)wafer表面。

3.PI Expose

PI曝光是在噴涂光刻膠的wafer與光源(紫外光)中間放入掩膜版(mask),再用紫外光透過掩模照射在硅片表面,被光線照射到的光刻膠會(huì)發(fā)生反應(yīng)。光刻膠有正性光刻膠和負(fù)性光刻膠兩種。正性光刻膠是掩膜版遮擋的區(qū)域進(jìn)行曝光,而負(fù)性光刻膠是對掩膜版未遮擋的區(qū)域進(jìn)行曝光。

4.PI Develop

PI顯影。與PI Coating原理類似,在wafer正面噴涂顯影液,顯影液與之前曝光區(qū)域形成化學(xué)反應(yīng)后,會(huì)將曝光區(qū)域顯影出來,即形成后續(xù)工藝中UBM層所需的一層開口區(qū)域。

5.PI CURE

對已顯影的wafer進(jìn)行烘烤,目的是蒸發(fā)掉剩余的溶劑使光刻膠變硬,提高光刻膠對硅片表面的粘附性。

6.Sputter Ti

濺射Ti層。Ti層是組成UBM(under

ball metal)的第一層。UBM層一般有兩層組成(有些廠家做三層),第一層為Ti,第二層為Cu。Ti具有高強(qiáng)度,耐腐蝕性等特點(diǎn),能與AL

PAD和Passivation連接良好,所以Ti層能為UBM層提供高強(qiáng)度的支撐。Sputter

原理是在真空環(huán)境下,電極兩端加上高壓產(chǎn)生直流光輝放電,使加入腔體內(nèi)的工藝氣體(如Plasma)進(jìn)行電離,電離后的正離子在電壓的作用下高速轟擊靶材,靶材逸出的原子和分子向wafer表面沉積形成薄膜層,即Ti層。

7.Sputter Cu

濺射UBM的第二層Cu. 此處的Cu一般只有1um左右,只是為了形成一個(gè)鈍化層面,為后續(xù)電鍍Cu提供堅(jiān)實(shí)的基礎(chǔ)。SputterCu的原理與Sputter Ti類似。

8. PR Coating

PR膠是一種負(fù)性光刻膠,是一種間接材料,與PI時(shí)的正性光刻膠作用相反。它的作用是為了在后續(xù)工藝中將不需要電鍍Cu的地方覆蓋,這樣在電鍍Cu時(shí),只在PR膠未覆蓋的地方”長”Cu,即UBM開口區(qū)域。

9.PR曝光

PR膠曝光同PI曝光原理類似,為了形成UBM開口區(qū)域,需通過曝光和顯影工序?qū)BM開口區(qū)域多余的化學(xué)層去除。

10.PR顯影

PR膠顯影與PI顯影原理類似,在PR曝光區(qū)域,利用顯影液將曝光區(qū)域去除,只留出UBM開口區(qū)域。

11.Plating Cu

電鍍Cu層,將剛濺射的Cu電鍍到一定厚度,不僅為置球提供良好的支撐,也為錫球與wafer內(nèi)部電路層提供良好的導(dǎo)電連接。此時(shí)PR膠覆蓋區(qū)域就不會(huì)”長”Cu,而未覆蓋區(qū)域”長”出所需要的Cu層。

12.刻蝕(PR, Cu , Ti )

利用化學(xué)品分別刻蝕掉UBM開口四周多余的PR層,Cu層,Ti層。至此,一個(gè)完整的UBM開口區(qū)域就形成了。

13.Ball Mount

置球。UBM開口形成后,就需要將球置于UBM開口上。將帶有UBM開口的wafer置于鋼網(wǎng)(Stencil)下面,UBM開口與鋼網(wǎng)開口一一對齊,然后在鋼網(wǎng)上刷上一層助焊劑Flux,最后用刮刀將錫球從鋼網(wǎng)開口”落”在UBM開口區(qū)域

14.Reflow

回流焊。將置好球的wafer放入回流爐中,錫球在助焊劑flux和高溫(大約260°)的作用下慢慢”長大”,并完美的填充UBM開口區(qū)域,與wafer形成良好的連接。錫球的作用是建立wafer內(nèi)部電路與外部電路的”橋梁”。至此,整個(gè)Bumping工藝完全結(jié)束。

CP test階段

晶圓測試。將完成回流焊的wafer進(jìn)行測試,目的是將在bumping工藝中的不良篩選出來,提高后續(xù)封裝的良率,監(jiān)測整個(gè)bumping工藝的質(zhì)量。

WLCSP階段

1. Backside Grind

在wafer正面(球面)貼上一層藍(lán)膜,保護(hù)錫球,然后在Wafer背面用磨輪磨至wafer指定厚度。

2. Wafer Backside Coating

在wafer背面刷一層背膠。目的是為了增強(qiáng)wafer的硬度,避免容易造成chipping。然后在一定溫度下進(jìn)行烘烤。(這一步選做,可做可不做)。

3. Marking(絲印)

在wafer背面按照產(chǎn)品要求打上Marking,包括公司Logo,生產(chǎn)日期,產(chǎn)品批次等相關(guān)信息。

4.Wafer Saw

Wafer切割。將打好絲印的wafer切割成一粒一粒的芯片。在切割之前,需在wafer背面貼上藍(lán)膜,目的是為切割后的單顆芯片提供保護(hù),不會(huì)散落。

5.Tape & Reel

先由頂針將切割后的芯片從藍(lán)膜上一顆一顆頂起,然后由吸嘴吸起來,放在編帶中進(jìn)行卷帶,最后包裝出貨。

以上步驟是整個(gè)流程的大致步驟,忽略了一些檢驗(yàn),ball shear之類的動(dòng)作。

晶圓級封裝(WLP)

晶圓級封裝的五項(xiàng)基本工藝,包括:光刻(Photolithography)工藝、濺射(Sputtering)工藝、電鍍(Electroplating)工藝、光刻膠去膠(PR Stripping)工藝和金屬刻蝕(Metal Etching)工藝。

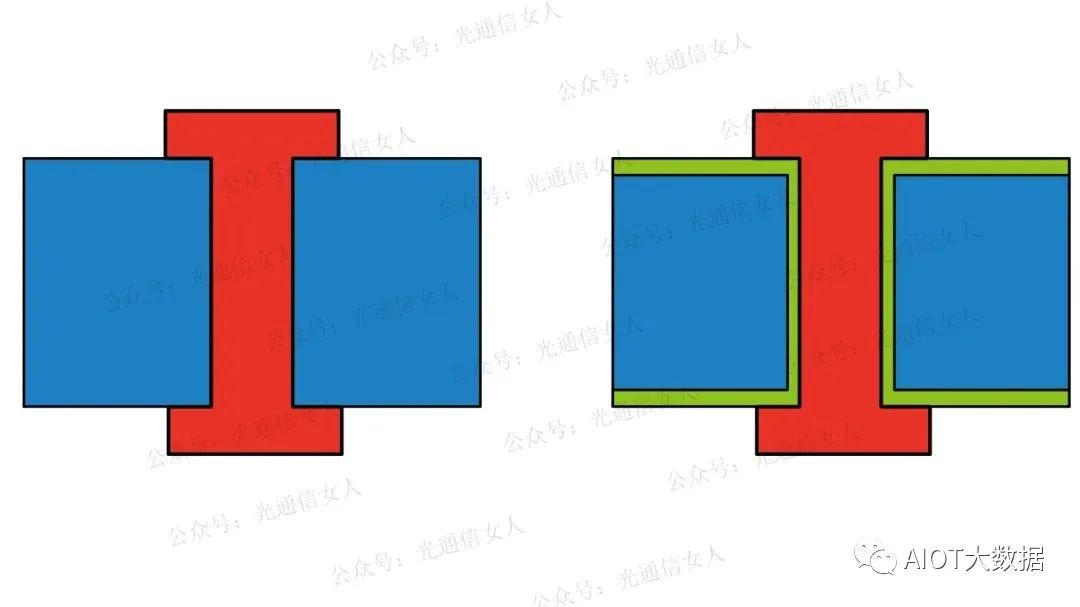

RDL(ReDistribution Layer)重布線層,起著XY平面電氣延伸和互聯(lián)的作用。

來自于《SiP與先進(jìn)封裝技術(shù)》

在芯片設(shè)計(jì)和制造時(shí),IO Pad一般分布在芯片的邊沿或者四周:

IO pad是一個(gè)芯片管腳處理模塊,即可以將芯片管腳的信號經(jīng)過處理送給芯片內(nèi)部,又可以將芯片內(nèi)部輸出的信號經(jīng)過處理送到芯片管腳。

這對于Bond Wire工藝來說自然很方便,但對于Flip Chip來說就有些勉為其難了。

因此,RDL就成為了此時(shí)的關(guān)鍵鑰匙:

在晶元表面沉積金屬層和相應(yīng)的介質(zhì)層,并形成金屬布線,對IO端口進(jìn)行重新布局,將其布局到新的,占位更為寬松的區(qū)域,并形成面陣列排布。

來自于臺積電官網(wǎng)(CoWos-R)示意圖

在先進(jìn)封裝的FIWLP (Fan-InWaferLevel Package) 、FOWLP (Fan-Out WaferLevel Package) 中:

RDL是最為關(guān)鍵的技術(shù)。

也正是這項(xiàng)技術(shù)的興起,使得封裝廠得以在扇出型封裝技術(shù)上與晶圓廠一較高下。

通過RDL將IOPad進(jìn)行FIWLP或者FOWLP,形成不同類型的晶圓級封裝。

在FIWLP中:

bump全部長在die上,而die和pad的連接主要就是靠RDL的metal line,封裝后的IC幾乎和die面積接近。Fan-out,bump可以長到die外面,封裝后IC也較die面積大(1.2倍)。

FOWLP是:先將die從晶圓上切割下來,倒置粘在載板上(Carrier)

此時(shí)載板和die粘合起來形成了一個(gè)新的wafer,叫做重組晶圓(Reconstituted Wafer);在重組晶圓中,再曝光長RDL。

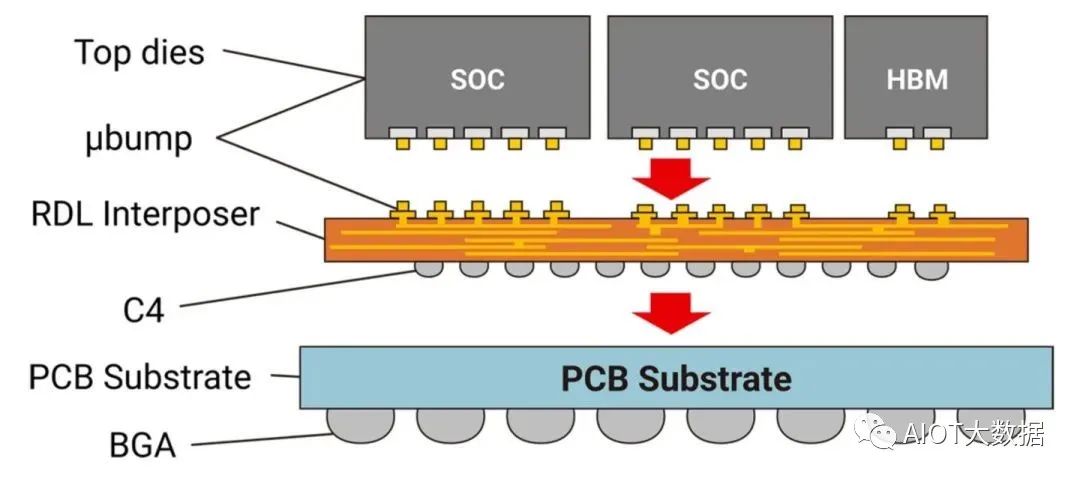

特別是在2.5D先進(jìn)封裝中,除了硅基板上的TSV,RDL同樣不可或缺:

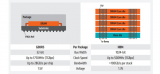

來自臺積電的InFO(集成扇出)晶圓級封裝

以臺積電的2.5D先進(jìn)封裝的代表InFO為例:

InFO 在載體上使用(單個(gè)或多個(gè))裸片,隨后將這些裸片嵌入molding compound的重構(gòu)晶圓中。

隨后在晶圓上制造 RDL 互連和介電層,這是“chip first”的工藝流程。

單die InFO 提供了高凸點(diǎn)數(shù)選項(xiàng),RDL 線從芯片區(qū)域向外延伸——即“扇出”拓?fù)洹?/p>

講到這,我們也應(yīng)該也對RDL技術(shù)有了一定的了解。

放眼未來:

RDL工藝的出現(xiàn)和演變也和TSV等先進(jìn)封裝其他工藝一樣,是一個(gè)不斷演變與進(jìn)化的過程。

但,當(dāng)下可知的是:

RDL工藝的誕生,已經(jīng)為先進(jìn)封裝中的異質(zhì)集成提供了操作上的基礎(chǔ)。

高密度扇出封裝與細(xì)間距嵌入式線路RDL;具有有機(jī)介電層的雙大馬士革工藝(Dual Damascene, DM)銅制程克服了細(xì)線路定義的挑戰(zhàn)。

封裝完整晶圓

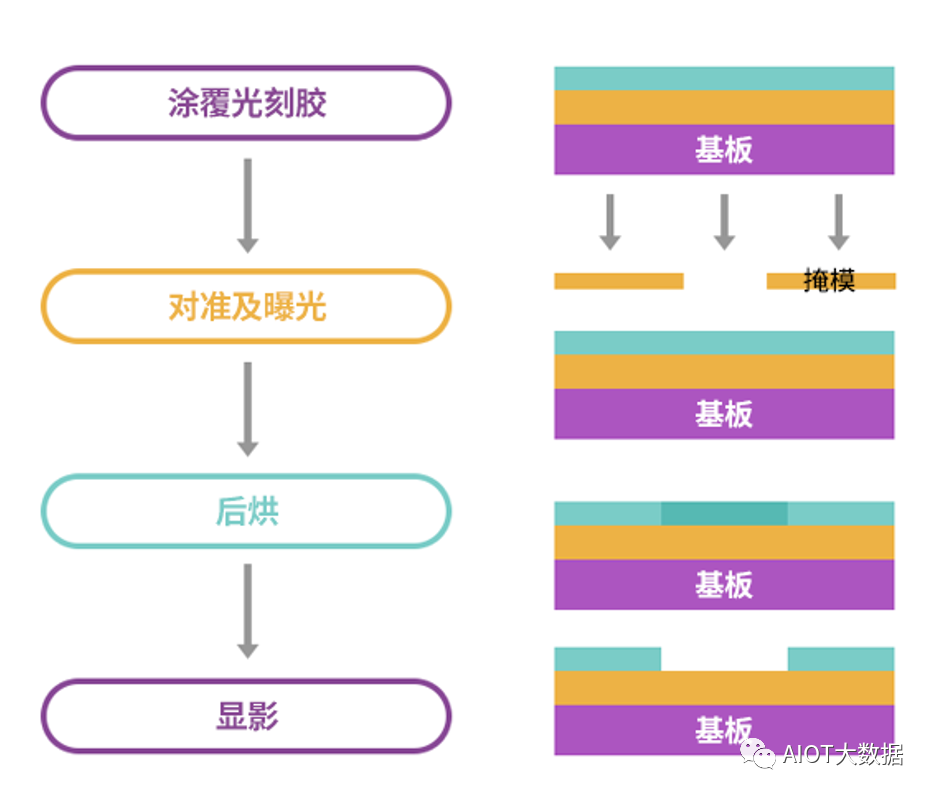

晶圓級封裝是指晶圓切割前的工藝。晶圓級封裝分為扇入型晶圓級芯片封裝(Fan-In WLCSP)和扇出型晶圓級芯片封裝(Fan-Out WLCSP),其特點(diǎn)是在整個(gè)封裝過程中,晶圓始終保持完整。除此之外,重新分配層(RDL)封裝、倒片(Flip Chip)封裝及硅通孔1(TSV)封裝通常也被歸類為晶圓級封裝,盡管這些封裝方法在晶圓切割前僅完成了部分工序。不同封裝方法所使用的金屬及電鍍(Electroplating)2繪制圖案也均不相同。不過,在封裝過程中,這幾種方法基本都遵循如下順序。

1硅通孔(TSV , Through-Silicon Via): 一種可完全穿過硅裸片或晶圓實(shí)現(xiàn)硅片堆疊的垂直互連通道。

2電鍍 (Electroplating): 一項(xiàng)晶圓級封裝工藝,通過在陽極上發(fā)生氧化反應(yīng)來產(chǎn)生電子,并將電子導(dǎo)入到作為陰極的電解質(zhì)溶液中,使該溶液中的金屬離子在晶圓表面被還原成金屬。

完成晶圓測試后,根據(jù)需求在晶圓上制作絕緣層(Dielectric Layer)。初次曝光后,絕緣層通過光刻技術(shù)再次對芯片焊盤進(jìn)行曝光。然后,通過濺射(Sputtering)3工藝在晶圓表面涂覆金屬層。此金屬層可增強(qiáng)在后續(xù)步驟中形成的電鍍金屬層的黏附力,同時(shí)還可作為擴(kuò)散阻擋層以防止金屬內(nèi)部發(fā)生化學(xué)反應(yīng)。

此外,金屬層還可在電鍍過程中充當(dāng)電子通道。之后涂覆光刻膠(Photoresist)以形成電鍍層,并通過光刻工藝?yán)L制圖案,再利用電鍍形成一層厚的金屬層。電鍍完成后,進(jìn)行光刻膠去膠工藝,采用刻蝕工藝去除剩余的薄金屬層。最后,電鍍金屬層就在晶圓表面制作完成了所需圖案。這些圖案可充當(dāng)扇入型WLCSP的引線、重新分配層封裝中的焊盤再分布,以及倒片封裝中的凸點(diǎn)。下文將對每道工序進(jìn)行詳細(xì)介紹。

3濺射 (Sputtering): 一項(xiàng)利用等離子體束對靶材進(jìn)行物理碰擊,使靶材粒子脫落并沉積在晶圓上的工藝。

? ?

? ?

? ?

? ?

▲圖1:各類晶圓級封裝工藝及相關(guān)步驟

光刻工藝:在掩模晶圓上繪制電路圖案

光刻對應(yīng)的英文是Photolithography,由“-litho(石刻)”和“graphy(繪圖)”組成,是一種印刷技術(shù),換句話說,光刻是一種電路圖案繪制工藝。首先在晶圓上涂覆一層被稱為“光刻膠”的光敏聚合物,然后透過刻有所需圖案的掩模,選擇性地對晶圓進(jìn)行曝光,對曝光區(qū)域進(jìn)行顯影,以繪制所需的圖案或圖形。該工藝的步驟如圖2所示。

▲圖2:光刻工藝步驟

在晶圓級封裝中,光刻工藝主要用于在絕緣層上繪制圖案,進(jìn)而使用繪制圖案來創(chuàng)建電鍍層,并通過刻蝕擴(kuò)散層來形成金屬線路。

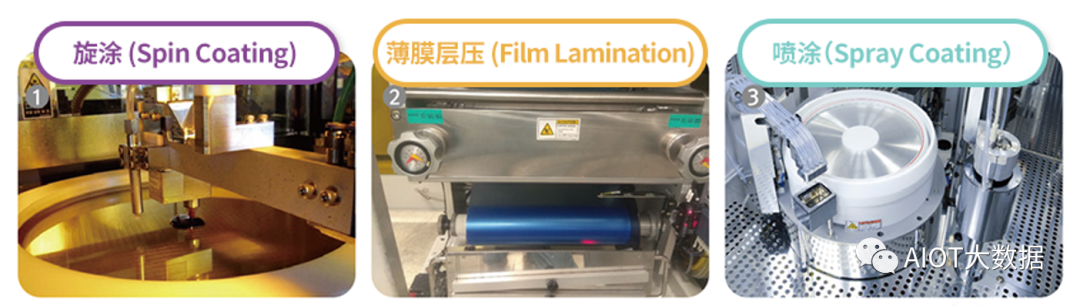

為更加清楚地了解光刻工藝,不妨將其與攝影技術(shù)進(jìn)行比較。攝影以太陽光作為光源來捕捉拍攝對象,對象可以是物體、地標(biāo)或人物。而光刻則需要特定光源將掩模上的圖案轉(zhuǎn)移到曝光設(shè)備上。另外,攝像機(jī)中的膠片也可類比為光刻工藝中涂覆在晶圓上的光刻膠。如圖4所示,我們可以通過三種方法將光刻膠涂覆在晶圓上,包括旋涂(Spin Coating)、薄膜層壓(Film Lamination)和噴涂(Spray Coating)。涂覆光刻膠后,需用通過前烘(Soft Baking)來去除溶劑,以確保粘性光刻膠保留在晶圓上且維持其原本厚度。

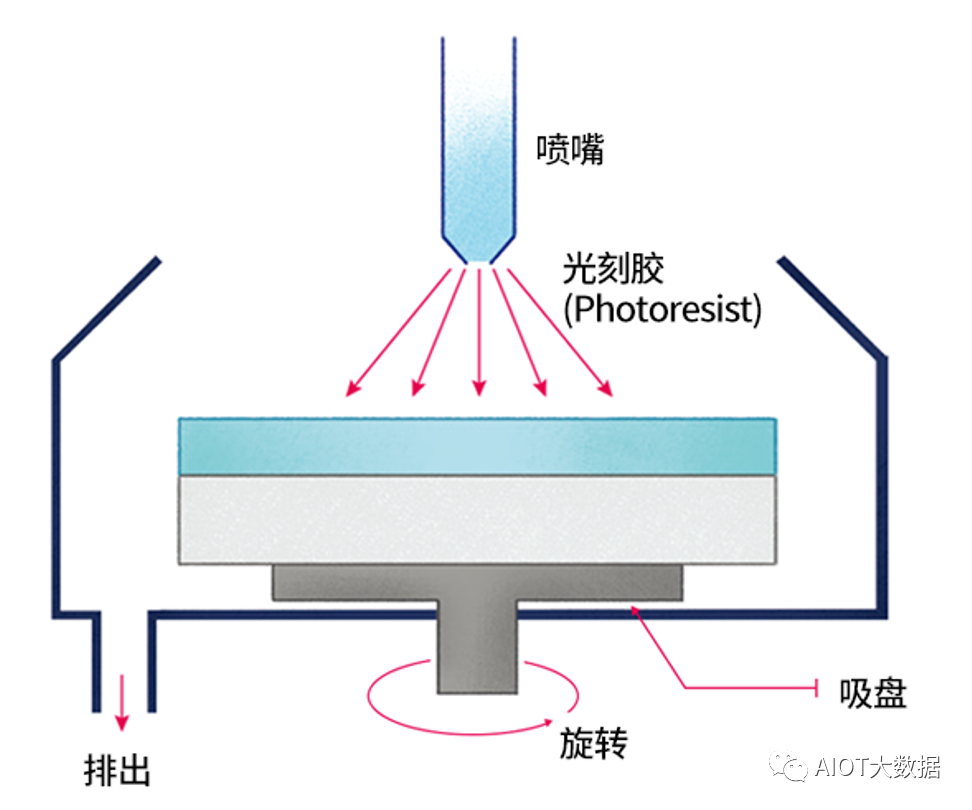

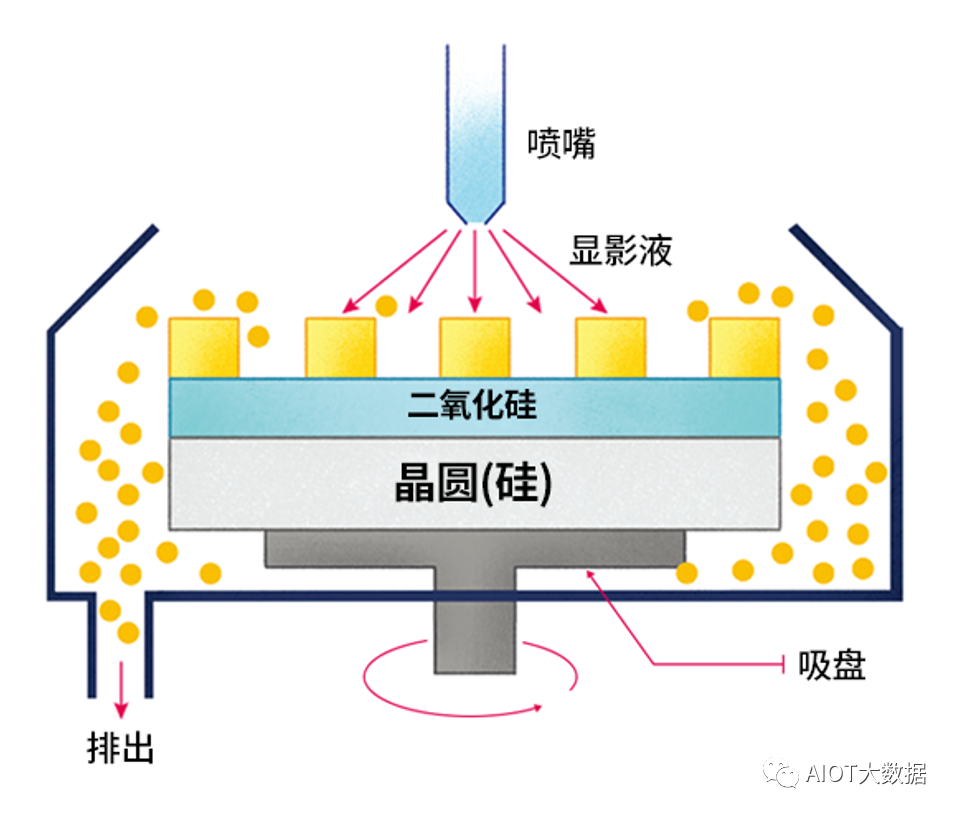

如圖5所示,旋涂將粘性光刻膠涂覆在旋轉(zhuǎn)著的晶圓中心,離心力會(huì)使光刻膠向晶圓邊緣擴(kuò)散,從而以均勻的厚度分散在晶圓上。粘度越高轉(zhuǎn)速越低,光刻膠就越厚。反之,粘度越低轉(zhuǎn)速越高,光刻膠就越薄。對于晶圓級封裝而言,特別是倒片封裝,光刻膠層的厚度須達(dá)到30 μm至100 μm,才能形成焊接凸點(diǎn)。然而,通過單次旋涂很難達(dá)到所需厚度。

在某些情況下,需要反復(fù)旋涂光刻膠并多次進(jìn)行前烘。因此,在所需光刻膠層較厚的情況下,使用層壓方法更加有效,因?yàn)檫@種方法從初始階段就能夠使光刻膠薄膜達(dá)到所需厚度,同時(shí)在處理過程中不會(huì)造成晶圓浪費(fèi),因此成本效益也更高。但是,如果晶圓結(jié)構(gòu)表面粗糙,則很難將光刻膠膜附著在晶圓表面,此種情況下使用層壓方法,會(huì)導(dǎo)致產(chǎn)品缺陷。所以,針對表面非常粗糙的晶圓,可通過噴涂方法,使光刻膠厚度保持均勻。

▲圖4:光刻膠涂覆的三種方法

▲圖5:旋涂方法示意圖

完成光刻膠涂覆和前烘后,接下來就需要進(jìn)行曝光。通過照射,將掩模上的圖案投射到晶圓表面的光刻膠上。由于正性光刻膠(Positive PR)在曝光后會(huì)軟化,因此使用正性光刻膠時(shí),需在掩模去除區(qū)開孔。負(fù)性光刻膠(Negative PR)在曝光后則會(huì)硬化,所以需在掩模保留區(qū)開孔。晶圓級封裝通常采用掩模對準(zhǔn)曝光機(jī)(Mask Aligner)4或步進(jìn)式***(Stepper)5作為光刻工藝設(shè)備。

4掩模對準(zhǔn)曝光機(jī)(Mask Aligner): 一種將掩模上的圖案與晶圓進(jìn)行對準(zhǔn),使光線穿過掩模并照射在晶圓表面的曝光設(shè)備。

5步進(jìn)式***(Stepper): 一種在工件臺逐步移動(dòng)時(shí),通過開啟和關(guān)閉快門控制光線以進(jìn)行光刻的機(jī)器。

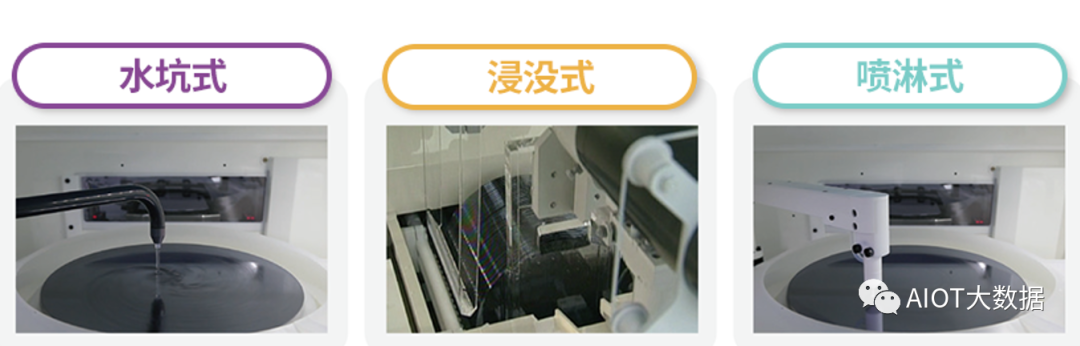

顯影(Development)是一種利用顯影液來溶解因光刻工藝而軟化的光刻膠的工藝。如圖6所示,顯影方法可分為三種,包括:水坑式 顯影(Puddle Development),將顯影液倒入晶圓中心,并進(jìn)行低速旋轉(zhuǎn);浸沒式顯影(Tank Development),將多個(gè)晶圓同時(shí)浸入顯影液中;噴淋式顯影(Spray Development),將顯影液噴灑到晶圓上。圖7顯示了靜態(tài)顯影方法的工作原理。完成靜態(tài)顯影后,通過光刻技術(shù)使光刻膠形成所需的電路圖案。

▲圖6:三種不同的顯影方法

▲圖7:水坑式顯影方法的工作原理

濺射工藝:在晶圓表面形成薄膜

濺射是一種在晶圓表面形成金屬薄膜的物理氣相沉積(PVD)6工藝。如果晶圓上形成的金屬薄膜低于倒片封裝中的凸點(diǎn),則被稱為凸點(diǎn)下金屬層(UBM,Under Bump Metallurgy)。通常凸點(diǎn)下金屬層由兩層或三層金屬薄膜組成,包括:增強(qiáng)晶圓粘合性的黏附層;可在電鍍過程中提供電子的載流層;以及具有焊料潤濕性(Wettability)7,并可阻止鍍層和金屬之間形成化合物的擴(kuò)散阻擋層。例如薄膜由鈦、銅和鎳組成,則鈦層作為黏附層,銅層作為載流層,鎳層作為阻擋層。因此,UBM對確保倒片封裝的質(zhì)量及可靠性十分重要。在RDL和WLCSP等封裝工藝中,金屬層的作用主要是形成金屬引線,因此通常由可提高粘性的黏附層及載流層構(gòu)成。

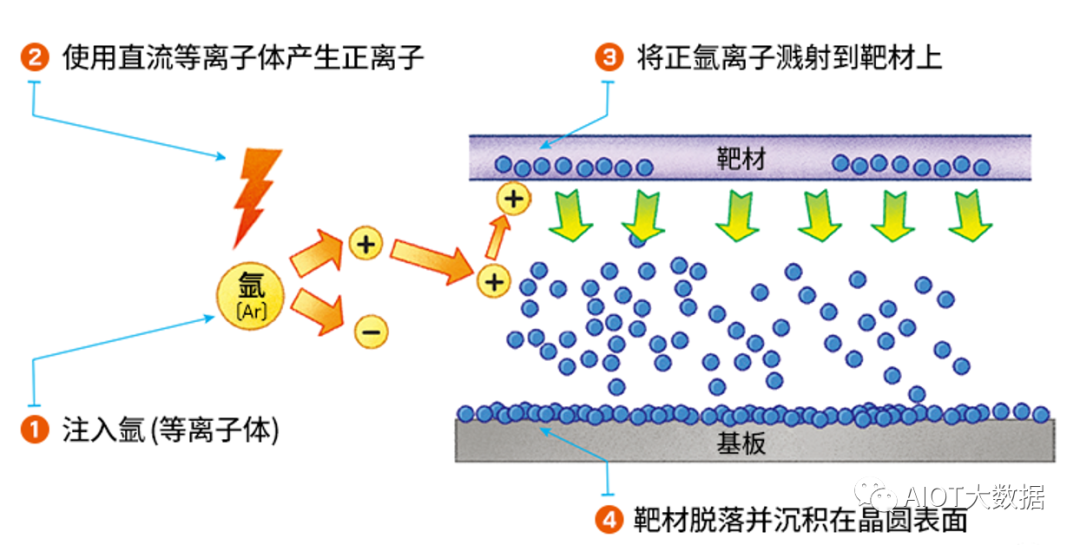

如圖8所示,在濺射工藝中,首先將氬氣轉(zhuǎn)化為等離子體(Plasma)8,然后利用離子束碰擊靶材(Target),靶材的成分與沉積正氬離子的金屬成分相同。碰擊后,靶材上的金屬顆粒會(huì)脫落并沉積在晶圓表面。通過濺射,沉積的金屬顆粒具有一致的方向性。盡管晶圓平坦區(qū)經(jīng)過沉積后厚度均勻,但溝槽或垂直互連通路(通孔)的沉積厚度可能存在差異,因此就沉積厚度而言,此類不規(guī)則形狀會(huì)導(dǎo)致平行于金屬沉積方向的基板表面的沉積厚度,比垂直于金屬沉積方向的基板表面沉積厚度薄。

6物理氣相沉積(PVD): 一種產(chǎn)生金屬蒸氣,并將其作為一種厚度較薄且具有粘性的純金屬或合金涂層沉積在導(dǎo)電材料上的工藝。

7潤濕性(Wettability): 因液體和固體表面的相互作用,使液體在固體表面擴(kuò)散的現(xiàn)象。

8等離子體(Plasma): 一種因質(zhì)子和電子的自由運(yùn)動(dòng)而呈電中性的物質(zhì)狀態(tài)。當(dāng)持續(xù)對氣體狀物質(zhì)進(jìn)行加熱使其升溫時(shí),便會(huì)產(chǎn)生由離子和自由電子組成的粒子集合體。等離子體也被視為固態(tài)、液態(tài)和氣態(tài)之外的“第四種物質(zhì)狀態(tài)”。

▲圖8:濺射的基本原理

電鍍工藝:形成用于鍵合的金屬層

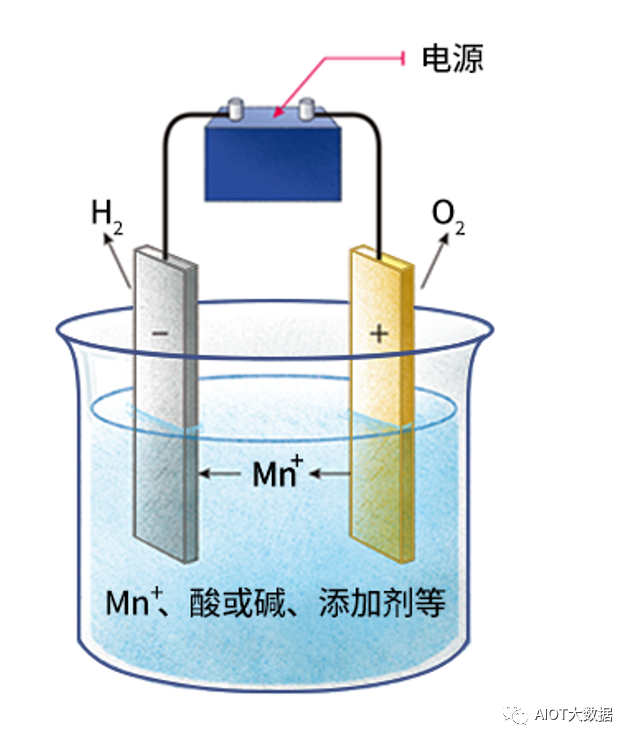

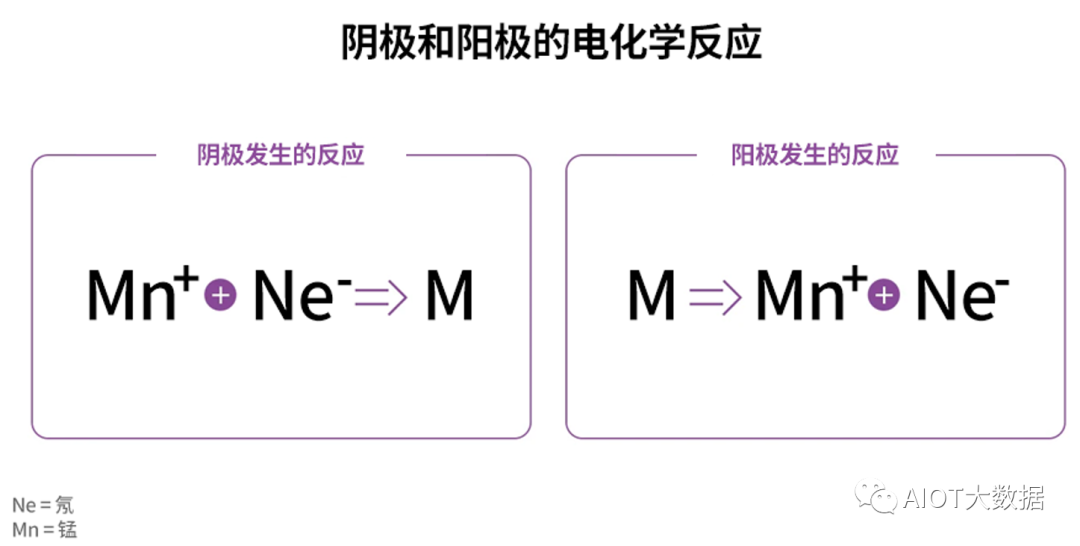

電鍍是將電解質(zhì)溶液中的金屬離子還原為金屬并沉積在晶圓表面的過程,此過程是需要通過外部提供的電子進(jìn)行還原反應(yīng)來實(shí)現(xiàn)的。在晶圓級封裝中,采用電鍍工藝形成厚金屬層。厚金屬層可充當(dāng)實(shí)現(xiàn)電氣連接的金屬引線,或是焊接處的凸點(diǎn)。如圖9所示,陽極上的金屬會(huì)被氧化成離子,并向外部電路釋放電子。在陽極處被氧化的及存在于溶液中的金屬離子可接收電子,在經(jīng)過還原反應(yīng)后成為金屬。

在晶圓級封裝的電鍍工藝中,陰極為晶圓。陽極由作為電鍍層的金屬制成,但也可使用如鉑金的不溶性電極(Insoluble Electrode)9。如果陽極板由作為鍍層的金屬制成,金屬離子就會(huì)從陽極板上溶解并持續(xù)擴(kuò)散,以保持溶液中離子濃度的一致性。如果使用不溶性電極,則必須定期補(bǔ)充溶液中因沉積到晶圓表面而消耗的金屬離子,以維持金屬離子濃度。圖10展示了陰極和陽極分別發(fā)生的電化學(xué)反應(yīng)。

9不溶性電極(Insoluble Electrode): 一種主要用于電解和電鍍的電極。它既不溶于化學(xué)溶液,也不溶于電化學(xué)溶液。鉑金等材料常被用于制作不溶性電極。

▲圖9:電鍍過程

▲圖10:陰極和陽極電化學(xué)反應(yīng)公式

在放置晶圓電鍍設(shè)備時(shí),通常需確保晶圓的待鍍面朝下,同時(shí)將陽極置于電解質(zhì)溶液中。當(dāng)電解質(zhì)溶液流向晶圓并與晶圓表面發(fā)生強(qiáng)力碰撞時(shí),就會(huì)發(fā)生電鍍。此時(shí),由光刻膠形成的電路圖案會(huì)與待鍍晶圓上的電解質(zhì)溶液接觸。電子分布在晶圓邊緣的電鍍設(shè)備上,最終電解質(zhì)溶液中的金屬離子與光刻膠在晶圓上繪制的圖案相遇。隨后,電子與電解質(zhì)溶液中的金屬離子結(jié)合,在光刻膠繪制圖案的地方進(jìn)行還原反應(yīng),形成金屬引線或凸點(diǎn)。

光刻膠去膠工藝和金屬刻蝕工藝:去除光刻膠

在所有使用光刻膠圖案的工藝步驟完成后,必須通過光刻膠去膠工藝來清除光刻膠。光刻膠去膠工藝是一種濕法工藝,采用一種被稱為剝離液(Stripper)的化學(xué)溶液,通過水坑式、浸沒式,或噴淋式等方法來實(shí)現(xiàn)。通過電鍍工藝形成金屬引線或凸點(diǎn)后,需清除因?yàn)R射形成的金屬薄膜。這是非常必要的一個(gè)步驟,因?yàn)槿绻蝗コ饘俦∧ぃ麄€(gè)晶圓都將被電氣連接從而導(dǎo)致短路。可采用濕刻蝕(Wet Etching)工藝去除金屬薄膜,以酸性刻蝕劑(Etchant)溶解金屬。這種工藝類似于光刻膠去膠工藝,隨著晶圓上的電路圖案變得越來越精細(xì),水坑式方法也得到了更廣泛的應(yīng)用。

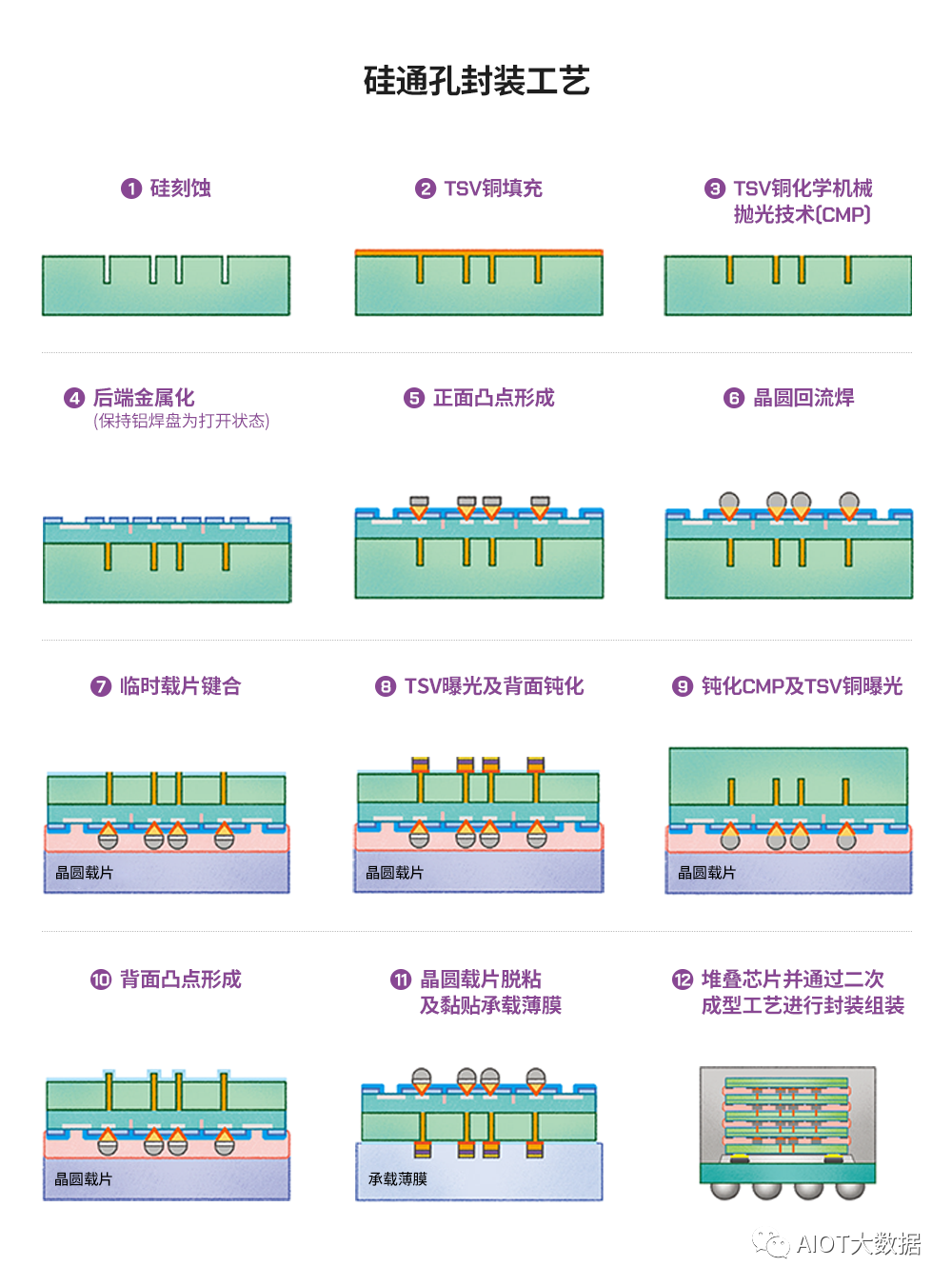

硅通孔封裝工藝

圖6展示了采用中通孔(Via-middle)5方法的硅通孔封裝工藝步驟。首先在晶圓制造過程中形成通孔。隨后在封裝過程中,于晶圓正面形成焊接凸點(diǎn)。之后將晶圓貼附在晶圓載片上并進(jìn)行背面研磨,在晶圓背面形成凸點(diǎn)后,將晶圓切割成獨(dú)立芯片單元,并進(jìn)行堆疊。5中通孔(Via Middle):一種硅通孔工藝方法,在互補(bǔ)金屬氧化物半導(dǎo)體形成后及金屬層形成之前開展的工序。接下來,將簡單概括中通孔的基本工序。首先在前道工序(Front-end of Line)中,在晶圓上制作晶體管,如互補(bǔ)金屬氧化物半導(dǎo)體等。

隨后使用硬掩模(Hard Mask)6在硅通孔形成區(qū)域繪制電路圖案。之后利用干刻蝕(Dry Etching)工藝去除未覆蓋硬掩膜的區(qū)域,形成深槽。再利用化學(xué)氣相沉積工藝(Chemical Vapor Deposition)制備絕緣膜,如氧化物等。這層絕緣膜將用于隔絕填入槽中的銅等金屬物質(zhì),防止硅片被金屬物質(zhì)污染。此外絕緣層上還將制備一層金屬薄層作為屏障。6硬掩膜(Hard Mask):一種由硬質(zhì)材料而非軟質(zhì)材料制成的薄膜,用于繪制更為精細(xì)的電路圖案。硬掩膜本身對光線并不敏感,所以需使用光刻膠才能進(jìn)一步繪制電路圖案,以最終實(shí)施刻蝕工藝。此金屬薄層將被用于電鍍銅層。電鍍完成后,采用化學(xué)機(jī)械拋光(Chemical Mechanical Polishing)技術(shù)使晶圓表面保持平滑,同時(shí)清除其表面銅基材,確保銅基材只留在溝槽中。然后通過后道工序(Back-end of Line)完成晶圓制造。

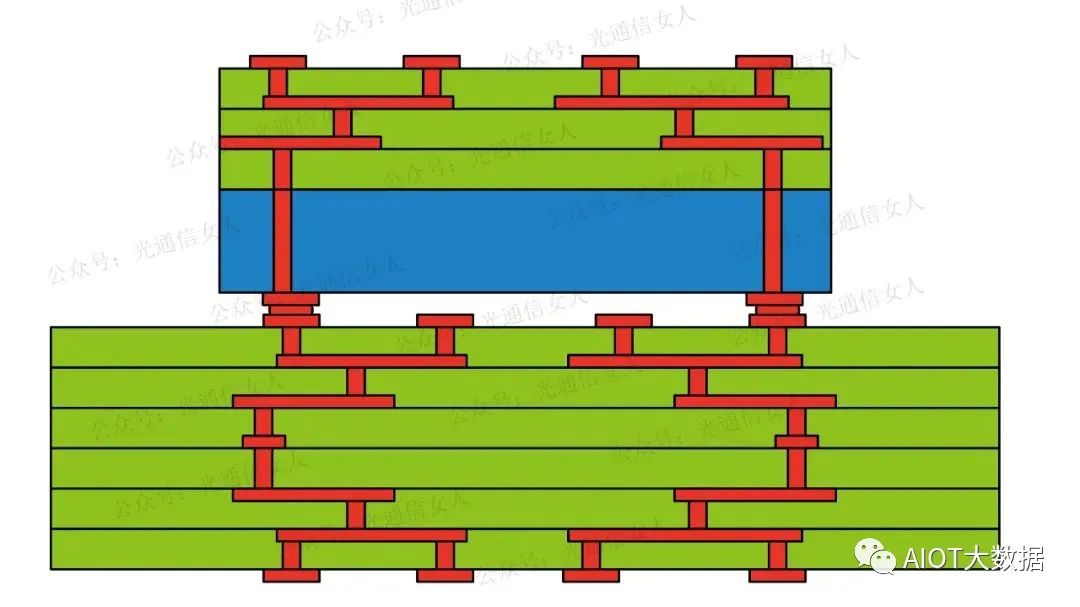

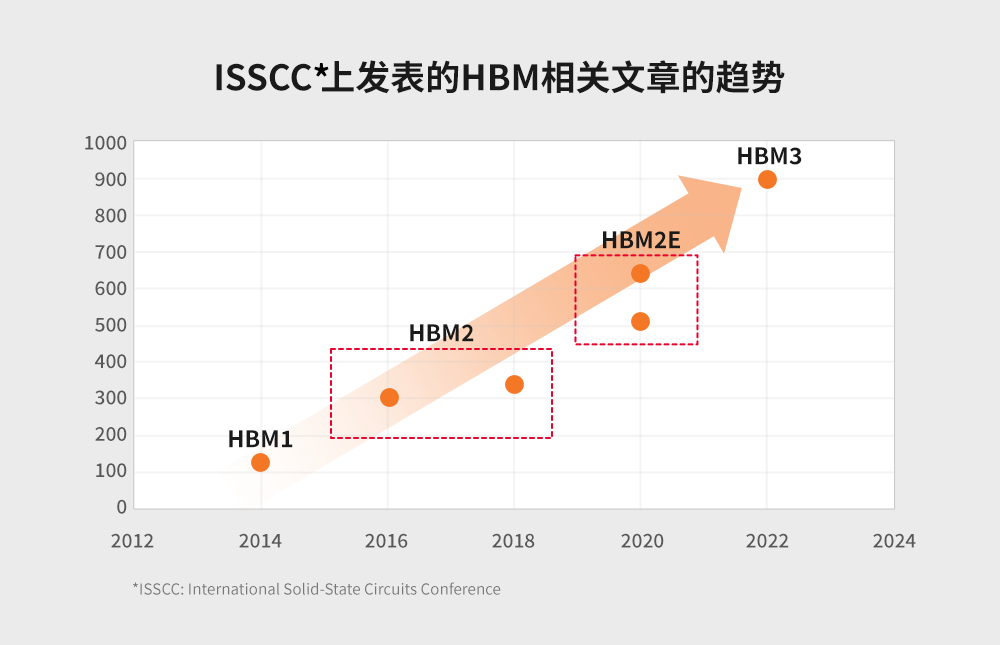

▲圖6:硅通孔封裝工序(? HANOL出版社)使用硅通孔技術(shù)制造芯片堆疊封裝體時(shí),一般可采用兩種類型的封裝方法。第一種方法是利用3D芯片堆疊技術(shù)的基板封裝。第二種方法則需創(chuàng)建KGSD,然后基于KGSD來制作2.5D或3D封裝。下文將詳細(xì)介紹如何創(chuàng)建KGSD,以及如何基于KGSD來制作2.5D封裝的過程。作為利用硅通孔技術(shù)制作而成的芯片堆疊封裝體,制作KGSD必需經(jīng)歷額外封裝工藝,如2.5D封裝、3D封裝以及扇出型晶圓級芯片封裝等,高帶寬存儲器(HBM)就是KGSD產(chǎn)品的一個(gè)典型例子。由于KGSD需經(jīng)歷額外封裝工藝,其作為連接引腳的焊接凸點(diǎn)需要比傳統(tǒng)錫球更加精細(xì)。因此3D封裝體中芯片堆疊在基板上,而KGSD中的芯片則堆疊于晶圓上方,晶圓也可以視為KGSD的最底層芯片。就HBM而言,位于最底層的芯片被稱為基礎(chǔ)芯片或基礎(chǔ)晶圓,而位于其上方的芯片則被稱為核心芯片。此方法工序如下:首先,通過倒片工藝在基礎(chǔ)晶圓和核心晶圓的正面制作凸點(diǎn)。在制作2.5D封裝體時(shí),基底晶圓需要排列凸點(diǎn),使之能夠附著到中介層(Interposer);相反,核心晶圓上的凸點(diǎn)布局則是有助于晶圓正面的芯片堆疊。在晶圓正面形成凸點(diǎn)后,應(yīng)減薄晶圓,同時(shí)也需在晶圓背面形成凸點(diǎn)。然而,正如前文在介紹背面研磨工藝時(shí)所述,需注意在減薄過程中導(dǎo)致晶圓彎曲。在傳統(tǒng)封裝工藝中,進(jìn)行減薄之前,可將晶圓貼附到貼片環(huán)架上,以防止晶圓彎曲,但在硅通孔封裝工藝中,由于凸點(diǎn)形成于晶圓背面,所以這種保護(hù)方法并不適用。為解決此問題,晶圓承載系統(tǒng)(Wafer Support System)應(yīng)運(yùn)而生。利用晶圓承載系統(tǒng),可借助臨時(shí)粘合劑將帶有凸點(diǎn)的晶圓正面貼附于晶圓載片上,同時(shí)對晶圓背面進(jìn)行減薄處理。此時(shí)晶圓貼附于晶圓載片上,即使經(jīng)過減薄也不會(huì)發(fā)生彎曲。此外,因晶圓載片與晶圓形式相同,因此也可使用晶圓設(shè)備對其進(jìn)行加工。

基于此原理,可在核心晶圓的背面制作凸點(diǎn),當(dāng)核心晶圓正面及背面上的凸點(diǎn)均制作完成時(shí),便可對載片進(jìn)行脫粘。隨后將晶圓貼附于貼片環(huán)架中,并參照傳統(tǒng)封裝工藝,對晶圓進(jìn)行切割。基礎(chǔ)晶圓始終貼附于晶圓載片上,從核心晶圓上切割下來的芯片則堆疊于基礎(chǔ)晶圓之上。芯片堆疊完成后,再對基礎(chǔ)晶圓進(jìn)行模塑,而后進(jìn)行晶圓載片脫粘。至此,基礎(chǔ)晶圓就變成了堆疊有核心晶圓的模制晶圓。隨后對晶圓進(jìn)行研磨,使其厚度達(dá)到制作2.5D封裝體所需標(biāo)準(zhǔn),然后再將其切割成獨(dú)立的芯片單元,以制作KGSD。HBM成品包裝后將運(yùn)送至制作2.5D封裝體的客戶手中。

硅通孔(TSV)

硅通孔(TSV) 是當(dāng)前技術(shù)先進(jìn)性最高的封裝互連技術(shù)之一。基于 TSV 封裝的核心工藝包括 TSV 制造、RDL/微凸點(diǎn)加工、襯底減薄、圓片鍵合與薄圓片拿持等。

(1)TSV 制造:TSV 制造可以分為兩種類型,類型I是孔底部不需要直接導(dǎo)電連接的制造類型,類型II是孔底部需要直接導(dǎo)電連接的制造類型。TSV 制造的主要工藝步驟包括孔刻蝕、絕緣層沉積、擴(kuò)散阻擋層/種子層沉積、導(dǎo)電材料填充及表面平坦化等。對于孔底部需要直接導(dǎo)電連接的類型,在完成絕緣層沉積后,需要選擇性地將孔底部絕緣層去除。

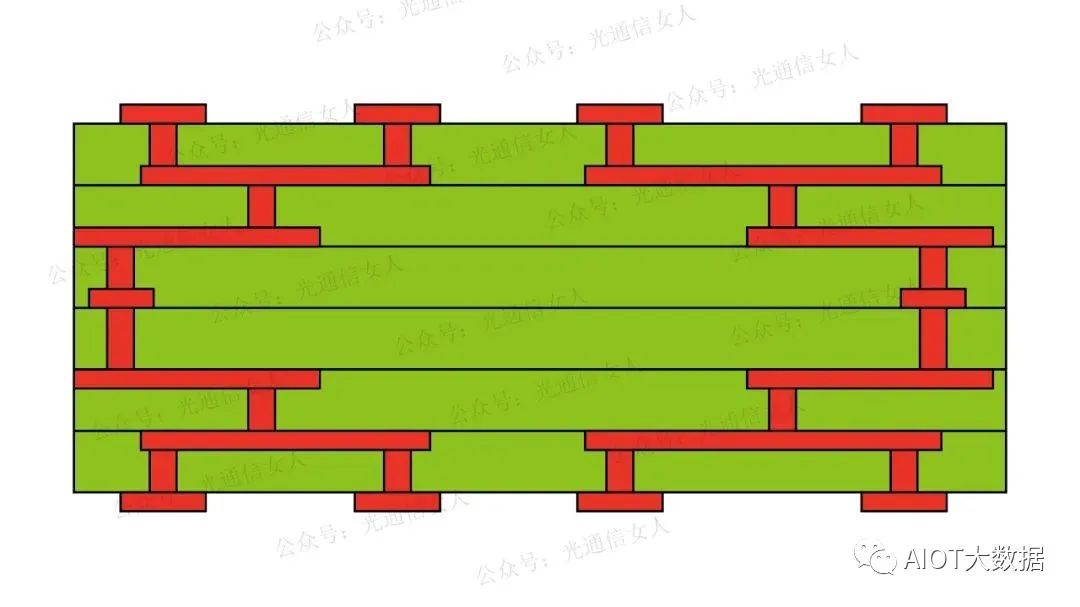

(2)RDL/微凸點(diǎn)加工:再布線層提供了 TSV 及討底上已有電路或器件的電學(xué)重分布,可為 TSV 提供更多的連接自由度,微凸點(diǎn)主要用于實(shí)現(xiàn)TSV襯底與其他芯片或封裝基板的直接電學(xué)連接。對于線寬小于 1μm 的RDL,需要用到鑲嵌工藝(又稱大馬士革工藝);對于線寬為 1μm 以上的 RDL,可采用厚膜掩模電鍍加成式工藝來實(shí)現(xiàn)。

(3)襯底減薄:根據(jù)工藝流程設(shè)計(jì),襯底減薄分為有 TSV 孔的減薄和無TSV 孔的減薄兩種情況。對于減薄時(shí)襯底內(nèi)無 TSV 的情況,僅需要處理硅材料,相對比較容易,只要保證處理后的表面平整度即可。對于減薄時(shí)襯底內(nèi)包含TSV 的情況,在減薄完成后,需要將 TSV 從襯底背面露出來,因此應(yīng)考慮硅與TSV 填充材料(如銅)的同步研磨或拋光,并應(yīng)控制填充材料不能與襯底硅導(dǎo)通或污染襯底硅。

(4)圓片鍵合與薄圓片拿持:在圓片減薄完成后,往往還需要很多后續(xù)工藝或臨時(shí)性工藝,其日的是提高生產(chǎn)過程中的成品率與效率,因此要保證薄圓片在這些工藝步驟中的安全,通常這是通過與承載片鍵合保護(hù)來實(shí)現(xiàn)的。如果承載片是功能性的,則鍵合 是一種永久鍵合。根據(jù)所使用的中間層材料,永久鍵合可以分為氧化硅鍵合、聚合物鍵合、金屬鍵合,以區(qū)這些鍵合的混合形式等。當(dāng)承載圓片是非功能性的襯底時(shí),需要臨時(shí)性的鍵合,以便在后續(xù)工藝過程中實(shí)現(xiàn)鍵合分離。

實(shí)現(xiàn)薄圓片拿持的基本工藝思路是,首先將待減薄圓片與一個(gè)承載圓片鍵合,之后進(jìn)行圓片減薄及減薄后的工藝加工,最后將承載圓片拆除,從而完成薄圓片的加工。

根據(jù)工藝集成方案中TSV、有源器件片內(nèi)互連的工藝順序,TSV 封裝工藝可以分為 Via First、Via Middle、Via Last 三種工藝方案。Via First 是指先完成 TSV的制作,再做有源芯片及其互連;Via Middle 是指先做有源器件,然后制作ISV,之后再進(jìn)行片內(nèi)互連工藝;Via Last 是指先完成有源芯片和有源芯片片內(nèi)互連層,最后制作TSV。 Via Middle 和 Via Last 工藝是目前應(yīng)用較廣泛的 TSV 解決方案。

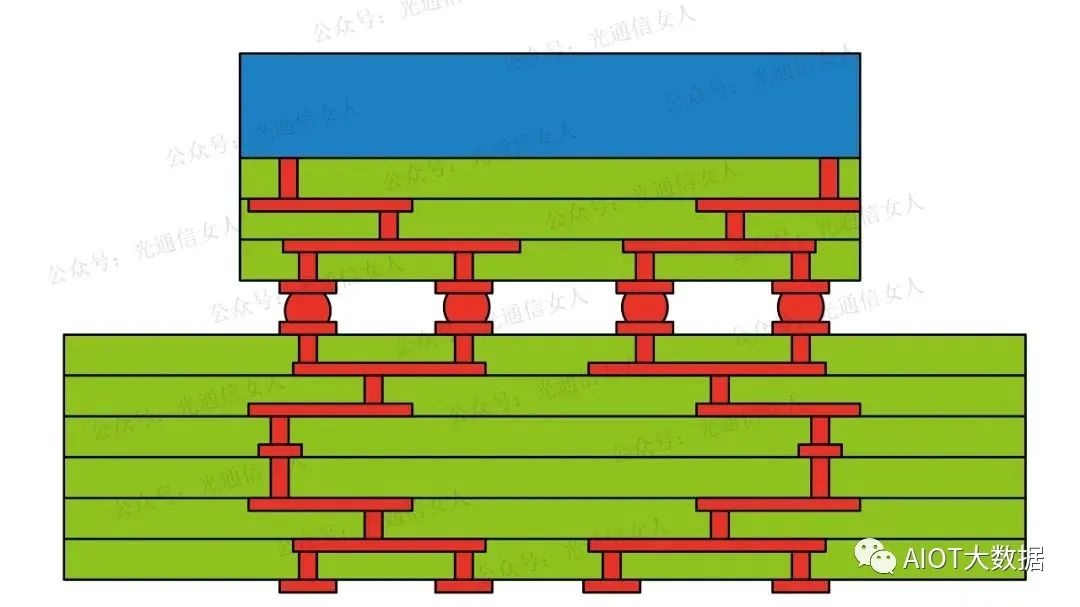

目前,TSV 主要有三大應(yīng)用領(lǐng)域,分別是三維集成電路(3D 1C)封裝、維圓片級芯片尺寸封裝(3D WLCSP)和2.5D 中介轉(zhuǎn)接層(Interposer)封裝。

(1)3D1C封裝:目前,3D IC 的應(yīng)用方向主要是存儲類產(chǎn)品,其原因是存儲類產(chǎn)品引腳密度小,版圖布局規(guī)律,芯片功率密度小等。通過 TSV 通孔實(shí)現(xiàn)三維集成,可以增加存儲容量,降低功耗,增加帶寬,減小延遲,實(shí)現(xiàn)小型化。

(2)3D WICSP: 主要應(yīng)用于圖像 指紋、濾波器、加速度計(jì)等傳感器封裝領(lǐng)域。其特點(diǎn)是采用 Via Last 工藝,TSV 深寬比較小(1:1~3:1),孔徑較大。出于對成本的考慮,目前圖像傳感器封裝大多采取低深寬比的 TSV 結(jié)構(gòu)。

(3) 2.5D 中介轉(zhuǎn)接層封裝:細(xì)線條布線中介轉(zhuǎn)接層針對的是 FPCA、CPU等高性能的應(yīng)用,其特征是正面有多層細(xì)節(jié)距再布線層和細(xì)節(jié)距微凸點(diǎn),主流ISV 深寬比達(dá)到 10:1,厚度約為 100wm。由于受技術(shù)難點(diǎn)和成本的限制,以及封裝厚度增加等問題,目前2.5D 中介轉(zhuǎn)按層處于小批量生產(chǎn)階段。

硅通孔最大的敵人,寄生電容

硅通孔對于帶寬的影響很大,尤其是寄生電容很大,導(dǎo)致RC常數(shù)很大,帶寬降低,需要各種小心避免。

換句話說,硅不做“通”孔,就沒有這些麻煩。

換第二句話說,PCB做“通”孔,也沒有這些麻煩

換第三句話說,LTCC低溫共燒陶瓷的多層布線做“通”孔,也沒有這些麻煩

今天略聊一下,硅的“通”孔戳了啥馬蜂窩

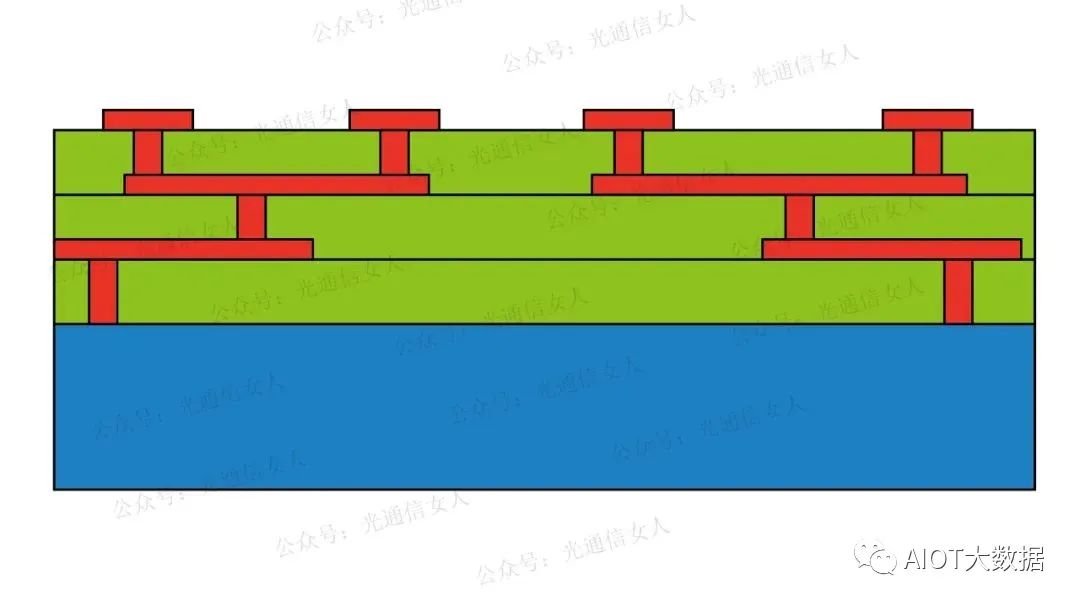

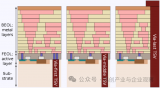

見過硅光工藝的布線吧,很多家工藝有單層的多層的,在綠色的氧化硅層縱向打孔,橫向走線,可以起到互聯(lián)作用。

層和層之間有氮化硅層

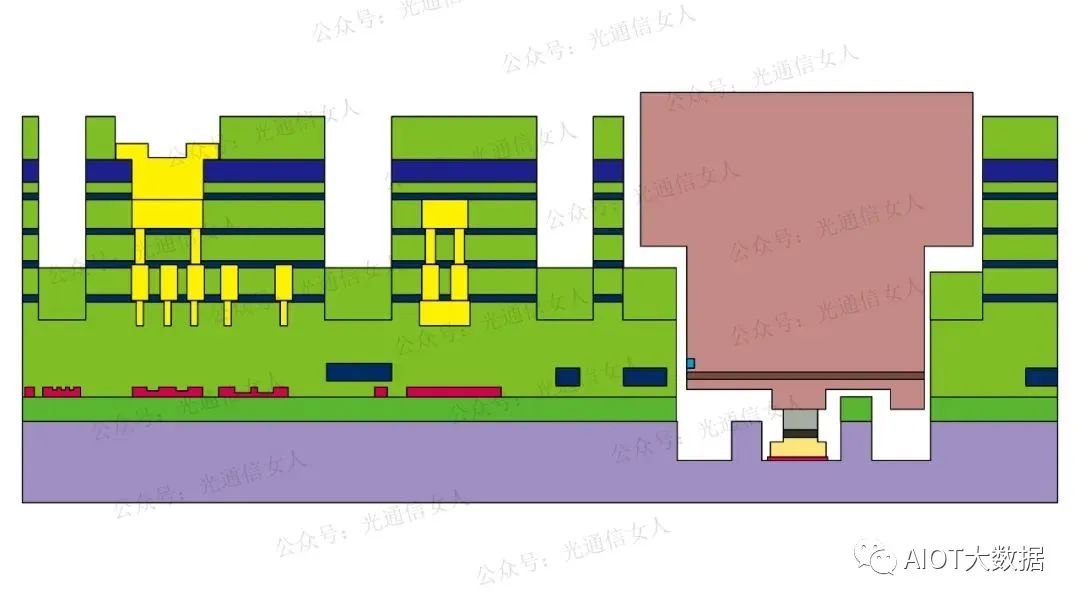

下圖是IMEC的不包括硅通孔的硅光工藝

也寫過基于硅通孔的工藝細(xì)節(jié),用于各種熱插拔和CPO的高密度封裝。我個(gè)人習(xí)慣用綠色來表示氧化硅,粉色表示硅。

下圖是Marvell的基于硅通孔的硅光芯片/光纖/激光器/DRV/TIA的組裝結(jié)構(gòu)。

從這些結(jié)構(gòu)看不出來,硅通孔與非通孔有啥本質(zhì)區(qū)別。我換個(gè)角度來聊。

只分三類材料,

第一類:導(dǎo)電的材料,都用橙色表示,比如PCB板中的銅、鎳、金,比如集成電路中的鎢、鈦、鎳、鉑、金、鋁、銅..., 總之,他們的目的是用來做“導(dǎo)體”路徑的。

第二類:絕緣的材料,都用綠色表示,比如PCB板中的玻璃纖維、樹脂等,比如集成電路中的氧化硅、氮化硅等,比如LTCC中的陶瓷..., 他們的目的是用來做“隔離”的,讓各個(gè)導(dǎo)體之間不會(huì)短路。

有了導(dǎo)體和絕緣體,就可以做多層布線了,傳統(tǒng)的PCB比較便宜,LTCC的多層陶瓷性能比較好,但也比較貴,等等。這些的核心性能是一致的,該導(dǎo)電的導(dǎo)電,不導(dǎo)電的就做好隔離工作。

PCB和LTCC做通孔,就不難。因?yàn)樗麄冎挥袃纱箢惒牧希瑢?dǎo)電的材料和不導(dǎo)電的材料。

第三類材料,半導(dǎo)體材料(這里我把半絕緣材料也籠統(tǒng)的包進(jìn)來,先不做細(xì)分)。半導(dǎo)體,就是半導(dǎo)電的固體材料,比如硅,這些材料有啥作用?

摻雜后形成P型半導(dǎo)體,N型半導(dǎo)體,PN之間,正向?qū)ǚ聪蚪刂梗@啥意思呢,正向偏壓的時(shí)候看著像“導(dǎo)體”,反向偏壓的時(shí)候看著像“絕緣體”,這就打開了另一個(gè)世界的通道,可控,聽話,我們的信號就有了“開關(guān)”兩個(gè)狀態(tài)了,是吧。

P型半導(dǎo)體和N型半導(dǎo)體再復(fù)雜一些,就可以是NPN、PNP等雙極性“開關(guān)”,就可以是NMOS、PMOS、CMOS等場控效應(yīng)的“開關(guān)”,比如DSP就是很典型的半導(dǎo)體集成“電路”

利用PN還可以控制光學(xué)信號,比如PN半導(dǎo)體中,正偏壓、反偏壓,來控制光學(xué)折射率,做激光器、探測器、調(diào)制器、濾波器、諧振腔....等等,如果用硅這種半導(dǎo)體來控制光學(xué),就是咱常聽到硅光集成,也就是半導(dǎo)體集成“光路”

我們天藍(lán)色來表示半導(dǎo)體,當(dāng)半導(dǎo)體集成電路或者集成光路,制作萬功能后,剩下的就是做多層互聯(lián),這時(shí)候不需要半導(dǎo)體再次表現(xiàn)出“正向反向”啥的變化,對于后期的信號線的布局,只需要該導(dǎo)電就導(dǎo)電,不導(dǎo)電就絕緣。

一般在頂層做線路互聯(lián)時(shí),導(dǎo)電的材料是金屬(銅、鋁、鎢等),絕緣的材料是氧化硅和氮化硅。一層層向晶圓的頂層引出就行。

傳統(tǒng)的集成電路和集成光路的布線層在頂面的幾層

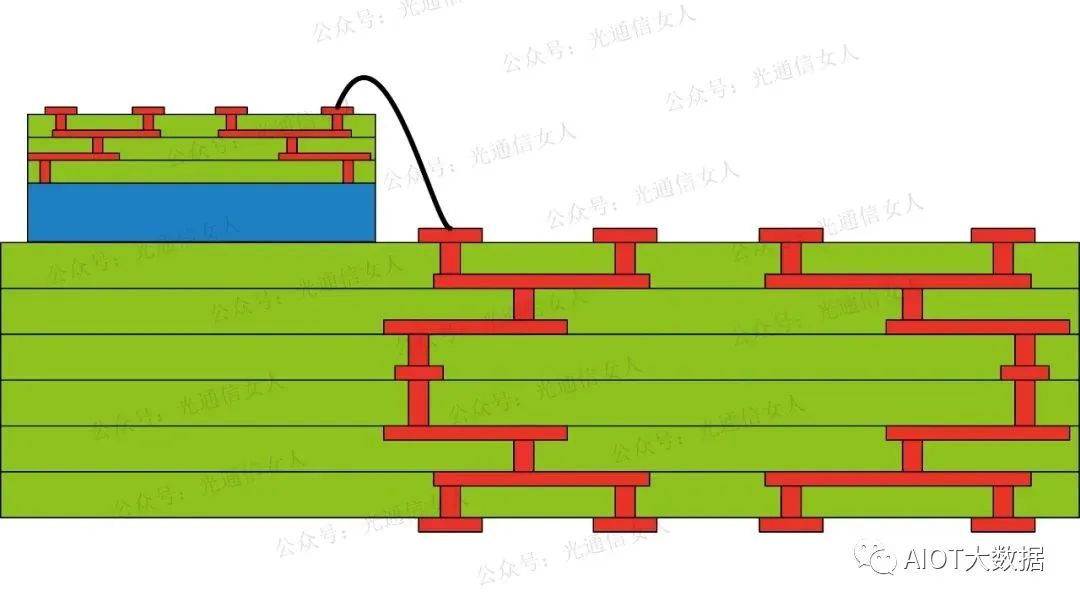

如果要把硅光芯片和PCB/LTCC的多層布線連在一起呢,也有三種形式,

一是“引線”鍵合,這種工藝用的最多了,有些引線,咱做光模塊的能看到,比如COB工藝。有些引線咱看不到,是因?yàn)檫@些引線被封裝起來了。

二是Flip Chip,倒裝焊,把芯片翻個(gè)面,引線的部分就和我們的PCB/LTCC焊在一起。同樣的,F(xiàn)lip Chip的結(jié)構(gòu),在光模塊的封裝工藝中,有些是可以看到的,有些看不到,芯片倒裝焊在一個(gè)基板后封裝好了再賣給我們的,我們只需拿來做SMT的貼裝就行。

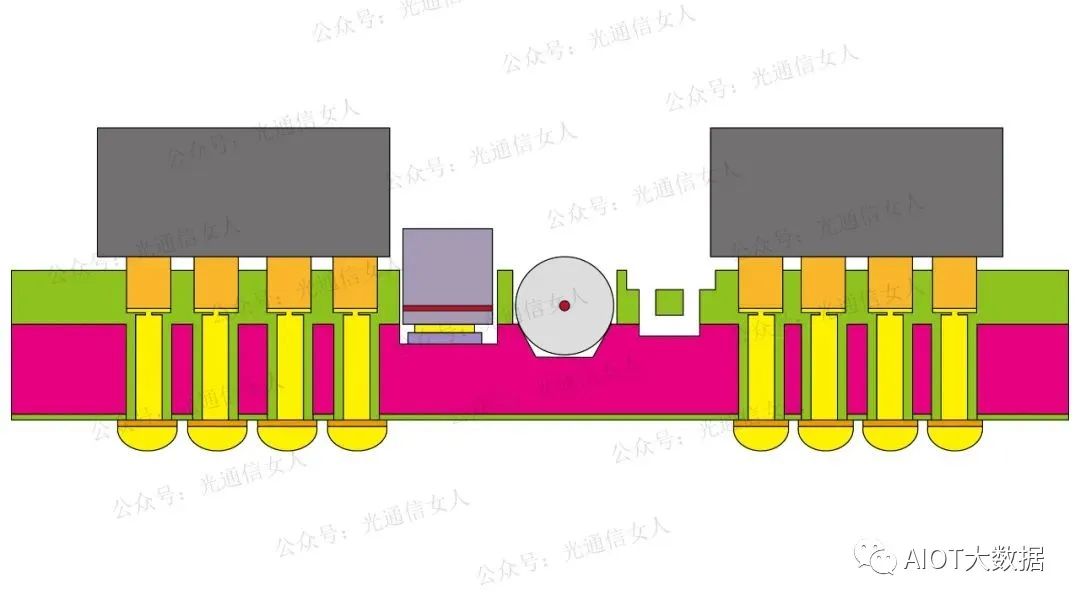

三,就是硅通孔,既不像第一種用外部金絲,也不像第二種反面。而是直接把藍(lán)色區(qū)域穿個(gè)孔,把導(dǎo)電引過來。

戳了馬蜂窩的,就是金屬線穿過藍(lán)色的“半導(dǎo)”電的區(qū)域。

我們非常習(xí)慣的是導(dǎo)體在絕緣體中穿過來又穿過去,雖然導(dǎo)體有好的不好的各種優(yōu)缺點(diǎn),絕緣體材料也是各種優(yōu)缺點(diǎn),總的來說,信號的絕大部分是在導(dǎo)體中傳送的。

但如果導(dǎo)體布線,并且直接在半導(dǎo)體中穿過來穿過去,就要了親命了,直接連不行,半導(dǎo)體雖然不是很導(dǎo)電,但也是半導(dǎo),信號的很大一部分能量就被半導(dǎo)體給消耗了,這壓根就不能用。

下圖左邊,就是我們常見的什么PCB板、陶瓷板、玻璃基板、集成電路/光路的上半部分的結(jié)構(gòu),導(dǎo)體穿越的是絕緣體。這是可行的。

下圖右側(cè),如果導(dǎo)體作為互聯(lián)的信號線而言,直接穿越半導(dǎo)體,是不行的。

一個(gè)變通的方法,就是在半導(dǎo)體中打個(gè)孔,然后涂覆一層絕緣體,用絕緣體把導(dǎo)體和半導(dǎo)體隔離開,這總行了吧。嗯,這行

這就是硅要把下半部分打穿,形成“通”孔,常見的工藝,在硅這個(gè)半導(dǎo)體材料上,先氧化一下,形成薄薄的一層氧化硅絕緣體,里邊再填注各種金屬做導(dǎo)線。

馬蜂窩,就是這個(gè)藍(lán)/綠/橙三色疊加體,其他地方看不到的奇觀,藍(lán)是半導(dǎo)體硅,綠是氧化硅絕緣體,橙是金屬導(dǎo)體

半導(dǎo)體-氧化硅-金屬,這是個(gè)電容

這個(gè)電容導(dǎo)致帶寬不足。

最后呼應(yīng)一下前頭換的那三句話。

換句話說,硅不做“通”孔,就沒有這些麻煩,鍵合絲工藝或者Flip Chip工藝,都無需在半導(dǎo)體中穿孔,不會(huì)額外增加個(gè)大電容。

換第二句話說,PCB做“通”孔,也沒有這些麻煩,因?yàn)镻CB只做互聯(lián),就兩類材料,導(dǎo)電的和不導(dǎo)電的,有寄生電容也很小,不是這種半導(dǎo)體-絕緣體-導(dǎo)體所寄生的大電容。

換第三句話說,LTCC低溫共燒陶瓷的多層布線做“通”孔,也沒有這些麻煩,理由與第二句話一樣,陶瓷是絕緣體。

審核編輯:劉清

-

晶圓

+關(guān)注

關(guān)注

53文章

5160瀏覽量

129763 -

半導(dǎo)體封裝

+關(guān)注

關(guān)注

4文章

293瀏覽量

14460 -

WLCSP封裝

+關(guān)注

關(guān)注

2文章

10瀏覽量

16405 -

硅通孔

+關(guān)注

關(guān)注

2文章

26瀏覽量

11992 -

HBM

+關(guān)注

關(guān)注

2文章

411瀏覽量

15233

原文標(biāo)題:技術(shù)前沿:HBM的關(guān)鍵工藝——硅通孔的能與不能

文章出處:【微信號:AIOT大數(shù)據(jù),微信公眾號:AIOT大數(shù)據(jù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

硅通孔封裝工藝流程與技術(shù)

簡單介紹硅通孔(TSV)封裝工藝

深度解析HBM內(nèi)存技術(shù)

一文詳解硅通孔技術(shù)(TSV)

TSV硅通孔填充材料

表面硅MEMS加工技術(shù)的關(guān)鍵工藝

PCB導(dǎo)電孔塞孔工藝及原因詳解

3D IC集成與硅通孔TSV互連

3D封裝與硅通孔(TSV)工藝技術(shù)

詳解TSV(硅通孔技術(shù))封裝技術(shù)

HBM的關(guān)鍵工藝—硅通孔的能與不能

HBM的關(guān)鍵工藝—硅通孔的能與不能

評論