3、狀態機建模工具使用示例

3.1. 使用狀態機建立電阻模型

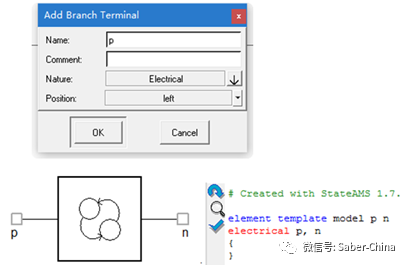

第一步****添加電阻端口

假設電阻阻值為r_normal,首先打開狀態機建模工具,添加電阻端口,電阻端口包含貫通變量電流和跨接變量電壓,使用分支型端口。

第二步****添加變量

添加電阻阻值r_normal為外部靜態變量

添加電流變量ipn

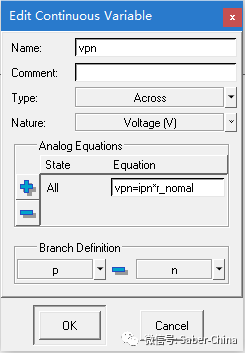

添加電壓變量vpn

第三步****添加狀態圖

電阻在整過過程中沒有狀態變化,雙擊變量vpn,設置如下

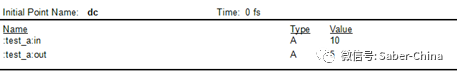

設置完成后,保存模型,搭建一個簡單的電路測試電阻模型是否正確。

3.2. 使用狀態機創建可變電阻

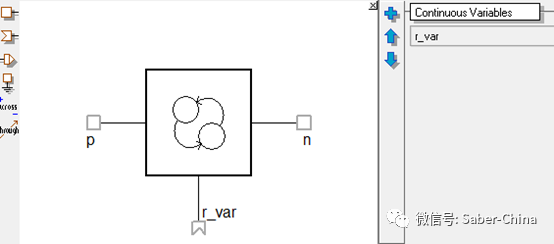

可變電阻的電阻值由外部管腳r_var控制。

首先建立symbol端子如下,設置p和n為electrical量

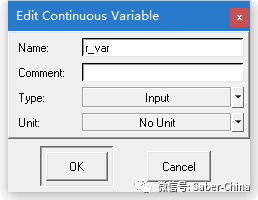

其中r_var是可變電阻的控制端。變量類型為

添加電阻的電壓變量vpn(依次點擊左側across圖標、p端口、n端口)和電流變量ipn(依次點擊左側through圖標、p端口、n端口)

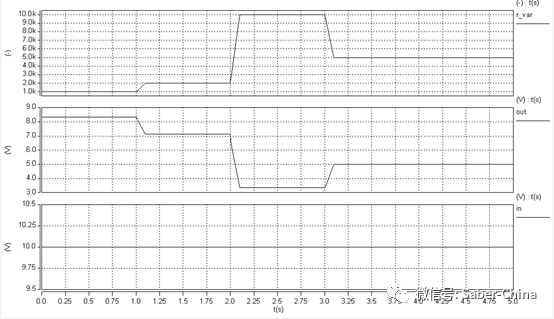

保存模型,搭建簡單電路進行驗證。

3.3. 創建基于公式的模型

如下公式是壓控電機中的一部分算法,三相正弦交流電壓幅值由控制電壓U_control,增益gain。偏置U_offset控制。頻率由f控制。

U_amp=U_control*gain+U_offset

U_a=U_ampsin(2pift)

U_b=U_ampsin(2pift+ 2*pi/3)

U_c=U_ampsin(2pift -2*pi/3)

建模時分兩個狀態機進行創建,vfconst和uf2abc。vfconst實現第一個公式,uf2abc實現后三個公式。

3.3.1. vfconst

建立symbol端子如下圖,u_offset和f是輸入,uout和fout是輸出,單位都是 nunit。

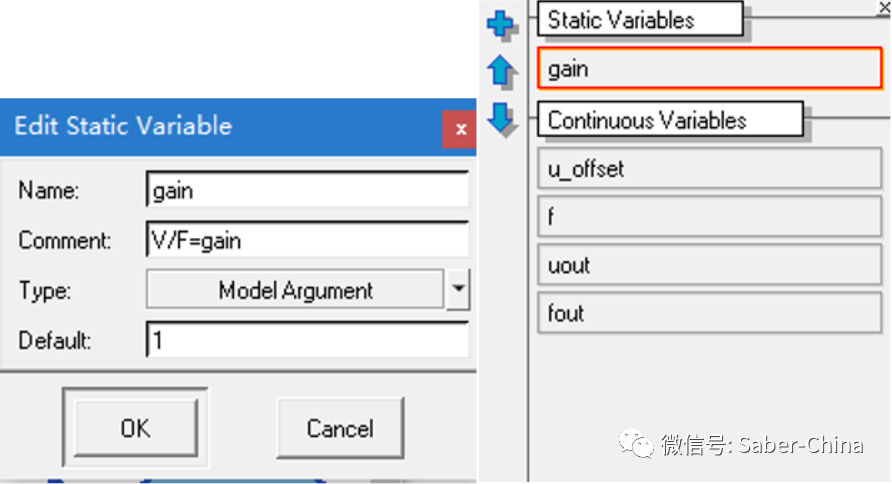

創建模型靜態變量gain

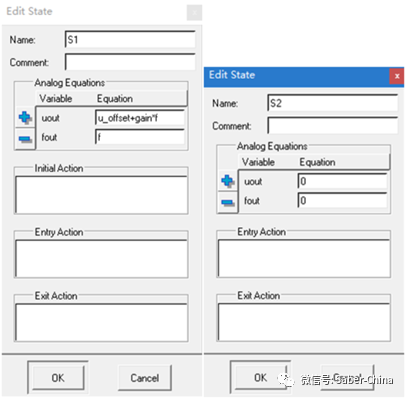

建立兩個狀態圖S1和S2,狀態關系為如果頻率小于等于0時,進入state2,如果頻率大于0時進入state1。、

鼠標雙擊state1和state2設置兩個輸出變量的公式,保存模型。

3.3.2. uf2abc建模

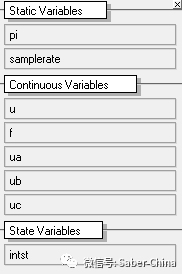

建立輸入輸出管腳,輸入管腳u,f,輸出管腳 ua,ub,uc。單位都是no unit。

創建兩個ststic 變量,pi和samolerate,pi即3.141593,samplerate用來控制模型的最大采樣間隔時間。創建一個state變量,配合下文的clk模塊正常運行。

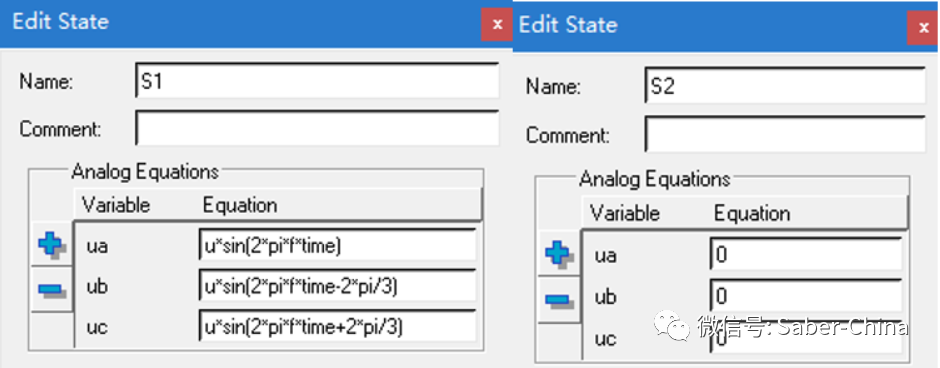

建立兩個狀態圖S1和S2,狀態關系為如果頻率小于等于0時,進入state2,如果頻率大于0時進入state1。

鼠標雙擊state1和state2設置兩個輸出變量的公式

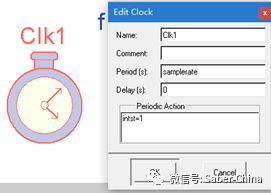

添加一個時鐘源clk1,時鐘源的周期為samplerate,每個周期內做的事為給intst變量賦值為1,這樣處理的意義是:保證saber仿真器在計算ua,ub,uc的值在一個1/f周期內有足夠的采樣點。因為仿真器的步長會變,如果f變大的話,可能導致一個1/f周期內采樣點不夠,導致波形失真。samplerate可以依據1/20*fmax來考慮。

模型創建好后可以搭建一個簡單電路進行驗證。

3.4. 創建IGBT信號驅動模型

IGBT驅動器模型可將邏輯數字信號轉換為電壓信號輸出以驅動IGBT模型工作。

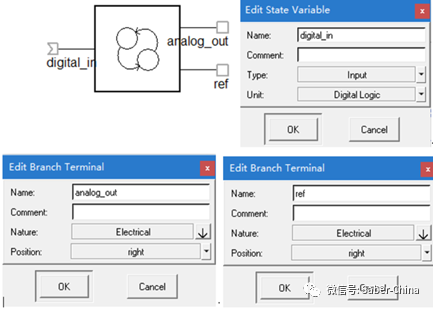

輸入為數字邏輯信號digital_in,輸出是模型信號analog_out,參考ref,高電平輸出電壓為vgon,低電平輸出電壓為vgoff,電平切換時間transition_time。

創建模型端口,digital_in輸入,邏輯信號。analog_out和ref輸出,電信號。

創建全局變量vgon,vgoff和transition_time

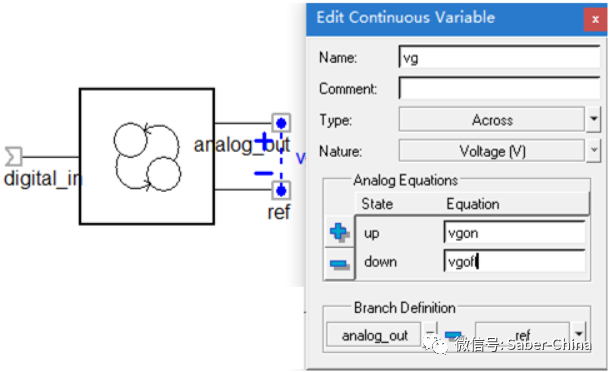

設置analog_out的電壓輸出變量vg。

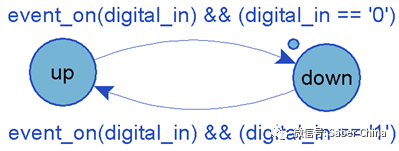

創建兩個state,分別命名為up和down。up狀態下設置vg=vgon,down狀態下設置vg=vgoff。digital_in=0時切換到down模式,等于1時,切換到up。

使用event_on函數判斷digital_in的狀態變化,使用digital_in == '0'或digital_in == '1‘判斷邏輯電平是高還是低。

mast語言中,高電平使用’1’表示,低電平使用’0’表示。

狀態切換時間設置為transition_time

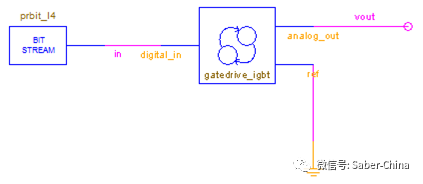

設置完成后保存模型,建立驗證電路測試模型。

-

可變電阻

+關注

關注

0文章

47瀏覽量

16013 -

狀態機

+關注

關注

2文章

493瀏覽量

28306 -

交流電壓

+關注

關注

2文章

189瀏覽量

17460 -

控制電壓

+關注

關注

0文章

36瀏覽量

16336 -

CLK

+關注

關注

0文章

128瀏覽量

17648

發布評論請先 登錄

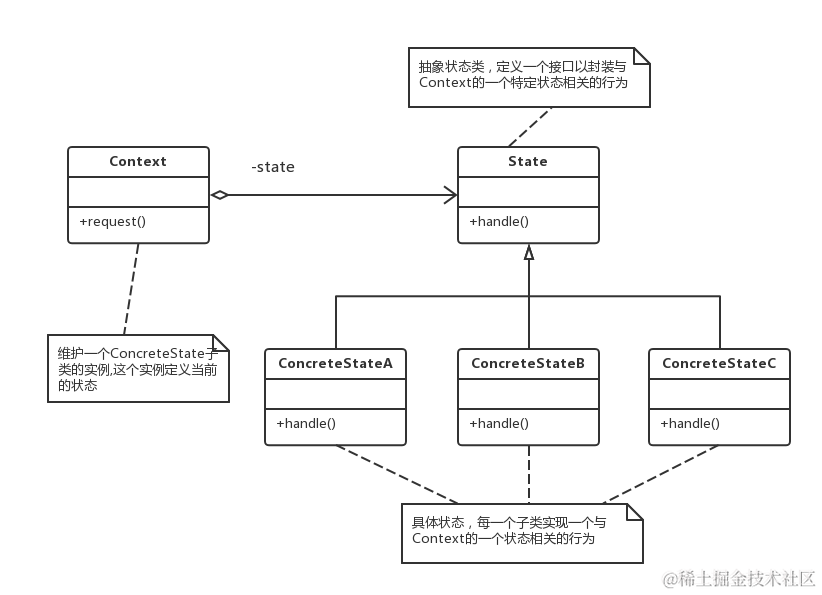

有限狀態機的建模與優化設計

如何構建基于狀態機的軟件系統

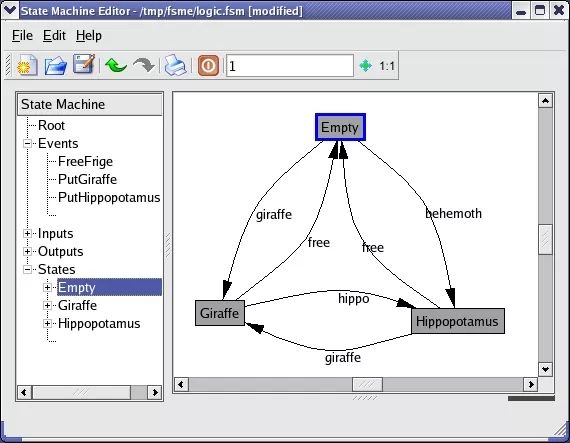

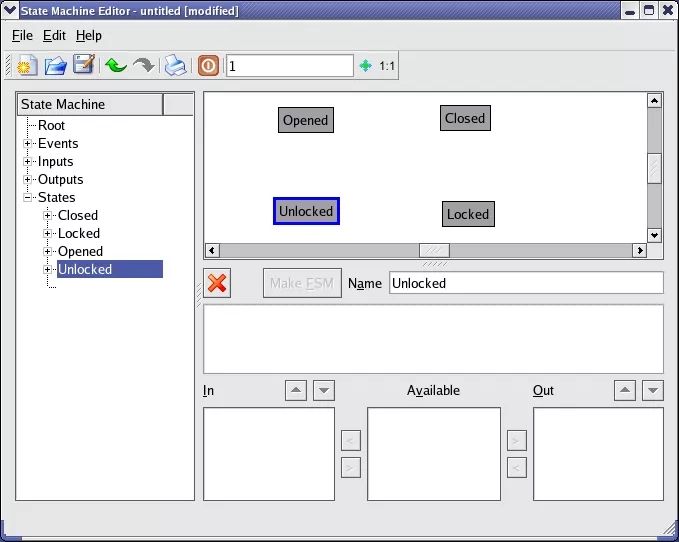

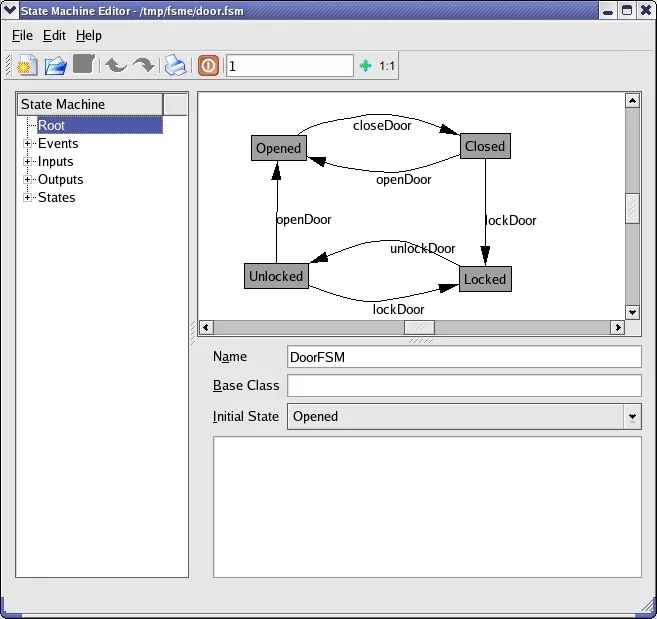

狀態機自動生成工具FSME

自動生成程序狀態機代碼狀態機建模方法

如何生成狀態機框架

什么是狀態機?狀態機的種類與實現

什么是有限狀態機?如何解決傳統有限狀態機「狀態爆炸」問題?

SaberRD狀態機建模工具介紹(二)狀態機建模工具使用示例

SaberRD狀態機建模工具介紹(二)狀態機建模工具使用示例

評論