SEMI-e 第六屆深圳國際半導體技術暨應用展覽會將持續關注產業核心技術和發展前沿,向20多個應用領域提供一站式采購與技術交流平臺。

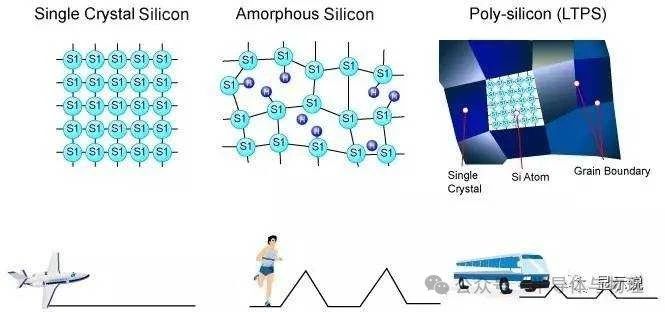

在SiC MOSFET 器件制備工藝中,多晶硅(Polysilicon)被廣泛用于柵電極,多晶電極對關鍵線寬(CD)要求極高,業界趨向于采用較低的射頻能量并能產生低壓和高密度的等離子體來實現多晶硅的干法刻蝕。其中感應耦合等離子刻蝕技術(ICP)得到大力應用。

隨著功率器件尺寸的不斷縮小,多晶硅柵的刻蝕越來越具有難度和挑戰性。此外,作為柵電極的多晶硅需要通過摻雜磷元素的手段來實現更好的電導通特性,多晶原位摻雜對設備能力要求較高,當前業界仍多采用離子注入和退火推結的方式對多晶硅進行摻雜磷處理。摻磷擴散后的多晶硅表面完全不同于未摻雜多晶硅,這對干法刻蝕形貌提出了更高的要求。

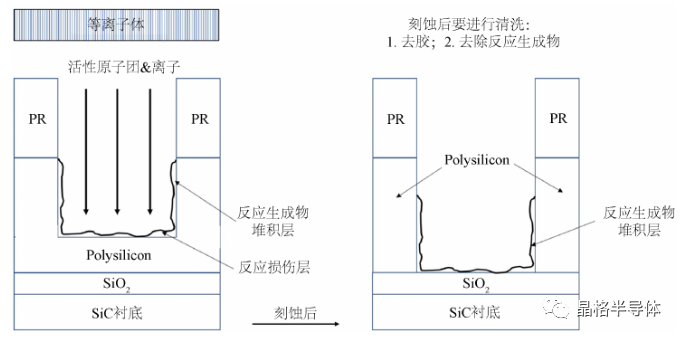

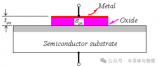

為了保護 MOSFET 的柵極氧化層不被損傷,通常要把多晶硅刻蝕分成幾個步驟:主刻蝕、著陸刻蝕和過刻蝕。主刻蝕通常有比較高的刻蝕速率,但是對氧化硅的選擇比較小。通過主刻蝕可基本決定多晶硅的剖面輪廓和關鍵尺寸。著陸刻蝕通常對柵極氧化層有比較高的選擇比以確保柵極氧化層不被損傷。一旦觸及到柵極氧化層后就必須轉成對氧化硅選擇比更高的過刻蝕步驟以確保把殘余的硅清除干凈而不損傷到柵極氧化層。

刻蝕終點檢測系統的原理如下,當發生側面刻蝕時,可以借助于使刻蝕減少到最低量從而能控制線寬和邊緣剖面到一定的程度。具體方法包括:

1) 刻蝕層的直接宏觀檢測;

2) 監測從刻蝕層的發射出的光波;

3) 用發射光譜法對等離子體刻蝕劑粒子的濃度檢測;

4) 用發射光譜法或質譜法對刻蝕產物的檢測;

5) 等離子體阻抗變化的檢測。

終點檢測對于刻蝕中工藝控制和工藝判斷,都是一個有用的輔助手段,可以使材料組份和厚度的波動或工作參數的改變而引起的刻蝕速率的變化得到補償。

多晶硅刻蝕原理(如圖所示),F原子對 Si 的刻蝕是各向同性的,所以以 F原子為基礎的化合物氣體如 CF4、SF6等都不適宜用作多晶硅的刻蝕氣體;而 Cl 原子對硅具有的各向異性刻蝕作用,所以 Cl2、HCl、SiCl4等氣體都可以被采用。使用這些氣體還有一個好處是,以 Cl 所形成的等離子體對 Si 及SiO2刻蝕的選擇比較好,因此在多晶硅刻蝕結束后,可以使用同樣性質的等離子體對聚酰亞胺(Polycide)進行過刻蝕,以確保多晶硅被刻凈,而又不會刻蝕太多的 SiO2層。

平面型 SiCMOSFET 柵結構采用的多晶硅溝槽深度為 5000 A,屬于淺溝槽刻蝕,其難點在于溝槽深度的均勻性控制,此外,為了滿足溝槽隔離氧化物的填充要求,溝槽剖面輪廓的控制也非常重要,因為太垂直的輪廓不利于化學氣相沉積(CVD)的沉積,通常會要求有適當的傾斜度。隨著工藝尺寸的縮小,要求達到更高的深寬比使得剖面輪廓控制和深度均勻性控制受到更大的挑戰。

當然 CD 的均勻性和剩余柵氧化層的均勻性也是重要的技術指標。對于淺溝槽的刻蝕,Cl2和HBr 依然是主刻蝕氣體,再配合小流量的氧氣和氮氣來產生氮氧化硅形成側壁鈍化層從而達到理想的刻蝕剖面輪廓,Ar 和He 通常用作輔助稀釋的作用。

由于溝槽底部輪廓同樣影響到氧化物的填充,采用 Cl2作為主刻蝕的氣體容易形成比較直的剖面輪廓和凸型的底部輪廓,采用 HBr 作為主刻蝕氣體能得到比較斜的剖面輪廓和凹形的底部輪廓。

審核編輯:劉清

-

多晶硅

+關注

關注

3文章

249瀏覽量

29849 -

MOSFET

+關注

關注

150文章

8620瀏覽量

220484 -

功率器件

+關注

關注

42文章

1933瀏覽量

92753 -

ICP

+關注

關注

0文章

75瀏覽量

13279

原文標題:多晶硅的刻蝕機理

文章出處:【微信號:Smart6500781,微信公眾號:SEMIEXPO半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

多晶硅在芯片制造中的作用

基于厚度梯度設計的TOPCon多晶硅指狀結構,實現25.28%量產效率突破

多晶硅錠定向凝固生長方法

單晶圓系統:多晶硅與氮化硅的沉積

為什么采用多晶硅作為柵極材料

多晶硅的存儲條件是什么

多晶硅生產過程中硅芯的作用

多晶硅柵工藝的制造流程

光伏多晶硅的應用領域有哪些

光伏多晶硅的分片方法及優缺點

多晶硅柵耗盡效應簡述

多晶硅的刻蝕機理介紹

多晶硅的刻蝕機理介紹

評論