在高速的同步電路設(shè)計(jì)中,時(shí)序決定了一切,要求所有時(shí)序路徑都必須在約束限制的時(shí)鐘周期內(nèi),這成為設(shè)計(jì)人員最大的難題,因此,首先確定和分析基本時(shí)序路徑有助于設(shè)計(jì)者快速,準(zhǔn)確地計(jì)算時(shí)序裕量,使系統(tǒng)穩(wěn)定工作,XILINX公司提倡的幾種常用基本路徑。

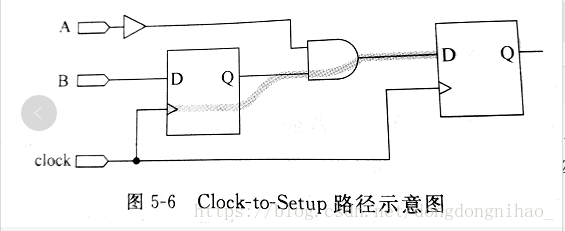

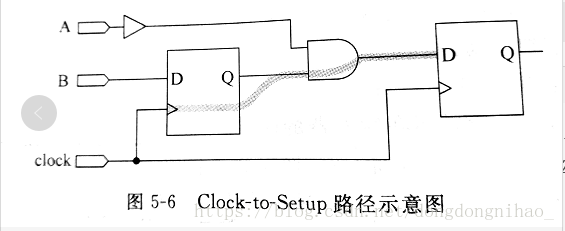

(1)Clock-to-Setup路徑:

clock-to-setup路徑從觸發(fā)器的輸入端開始,結(jié)束于下一級觸發(fā)器,鎖存器或者RAM的輸入端,對終止端的數(shù)據(jù)信號要求一定的建立時(shí)間。

如下圖所示:

該條路徑包括了觸發(fā)器內(nèi)部clock-to-Q的延遲,觸發(fā)器之間的由組合邏輯造成的路徑延遲以及目標(biāo)觸發(fā)器的建立時(shí)間,其延時(shí)是數(shù)據(jù)從源觸發(fā)器開始,在下一個(gè)時(shí)鐘沿來到之前通過組合邏輯和布線的最大時(shí)間,Clock-to-Setup時(shí)間可通過約束文件中的周期約束來限制。

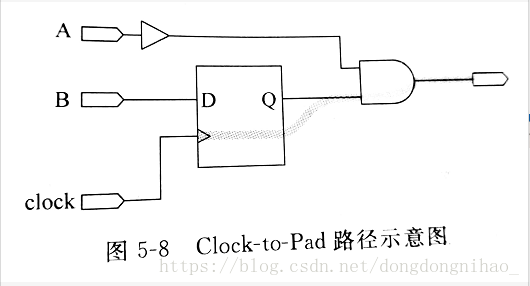

(2)Clock-to-pad路徑:

Clock-to-Pad路徑從寄存器或者鎖存器的時(shí)鐘輸入端開始,終止于芯片的輸出引腳,中間經(jīng)過了觸發(fā)器輸出端以及所有的組合邏輯,如下圖所示:

這條路徑包括了經(jīng)過觸發(fā)器的延時(shí)和從觸發(fā)器到輸出引腳之間的邏輯延遲,在約束文件中,可以通過OFFSET語句和FROM:TO來約束,如果使用OFFSET語句,那么時(shí)延計(jì)算時(shí)會包含時(shí)鐘輸入BUFFER/ROUTING延時(shí);如果使用FROM:TO約束,則延時(shí)從觸發(fā)器自身開始,不包括輸入路徑,比較精確,所以使用相對更頻繁一些。

① OFFSET語句:OFFSET說明了外部時(shí)鐘和與其相關(guān)的輸入,輸出數(shù)據(jù)引腳之間的時(shí)序關(guān)系。其語法規(guī)則如下:

OFFSET={IN/OUT}"offset_time"[unit] {BEFORE/AFTER} "clk_name"[TIMEGRP"group_name"];

OFFSET可以用于設(shè)置多類約束,對于Clock-to-Pad需要將屬性配置為OUT AFTER, 例如:

NET Q_out OFFSET = OUT 35.0 AFTER "CLK_SYS"

② FROM :TO 語句 :FROM:TO定義了兩組信號之間時(shí)序關(guān)系。

其語法規(guī)則如下:

#TIMESPEC "TSname" = FROM "group1"TO "group2" value;

其中,TSname 必須以TS開頭,group1是起始路徑,group2是目的路徑,value值的默認(rèn)單位為ns,也可以使用MHZ。

實(shí)例:

TIMESPEC TS_aa = FROM FFS TO PAD 10;

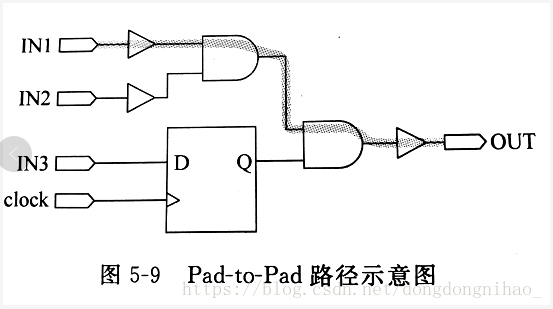

(3)Pad-to-Pad路徑:

Pad-to-Pad路徑從芯片輸入信號端口開始,結(jié)束于芯片輸出信號端口,中間包含所有組合邏輯,但并不包含任何同步邏輯如圖所示:

Pad-to-Pad路徑延時(shí)是數(shù)據(jù)輸入到芯片,經(jīng)過邏輯延時(shí)和布線時(shí)延后再輸出芯片的最大時(shí)間要求,在約束文件中任然通過FROM:TO來約束,其語法如下:

TIMESPEC TS_aa = FROMPADSTO PADS 10 ;

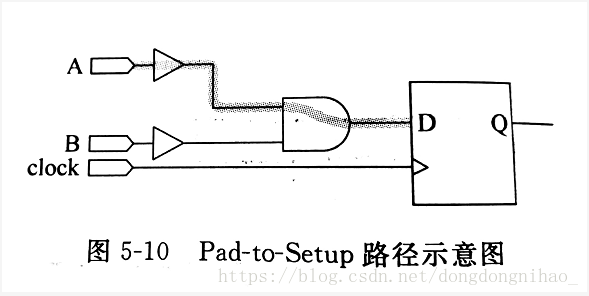

(4)Pad-to-Setup路徑

Pad-to-setup路徑從芯片的輸入信號端口開始,結(jié)束于同步電路模塊(觸發(fā)器,鎖存器和RAM),對相應(yīng)的數(shù)據(jù)信號要求一定的建立時(shí)間,如下圖所示:

該路徑可以通過BUFFER和所有組合邏輯,不包含任何同步電路木塊和雙向端口,是數(shù)據(jù)到達(dá)芯片的最大時(shí)間要求,和Clock-to-Pad一樣,該路徑可以通過OFFSET和FROM:TO來設(shè)計(jì),其中OFFSET語句的屬性設(shè)置為OFFSET IN BEFORE。

例如:

OFFSET = IN 10 ns BEFORE my_clk TIMEGRP My_FFS;

-

FPGA

+關(guān)注

關(guān)注

1645文章

22021瀏覽量

617356 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2039瀏覽量

62059 -

時(shí)序

+關(guān)注

關(guān)注

5文章

397瀏覽量

37909

原文標(biāo)題:FPGA設(shè)計(jì)的常用基本時(shí)序路徑分析

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

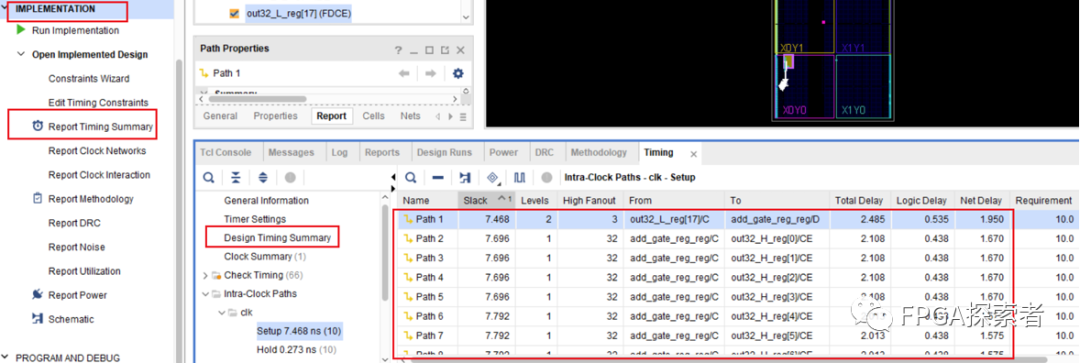

FPGA案例之時(shí)序路徑與時(shí)序模型解析

詳細(xì)解析vivado約束時(shí)序路徑分析問題

FPGA設(shè)計(jì)的常用基本時(shí)序路徑分析

vivado約束案例:跨時(shí)鐘域路徑分析報(bào)告

FPGA時(shí)序約束之偽路徑和多周期路徑

FPGA時(shí)序分析之關(guān)鍵路徑

FPGA時(shí)序約束之時(shí)序路徑和時(shí)序模型

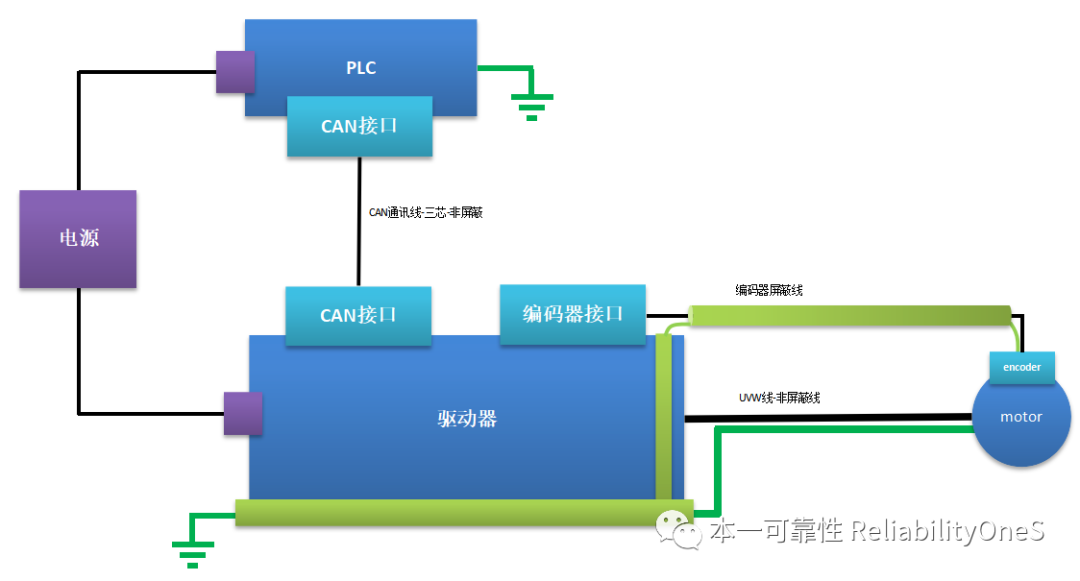

驅(qū)動器共模電流路徑與數(shù)學(xué)模型分析

大西瓜FPGA--FPGA設(shè)計(jì)高級篇--時(shí)序分析技巧

ArcGIS的路徑分析

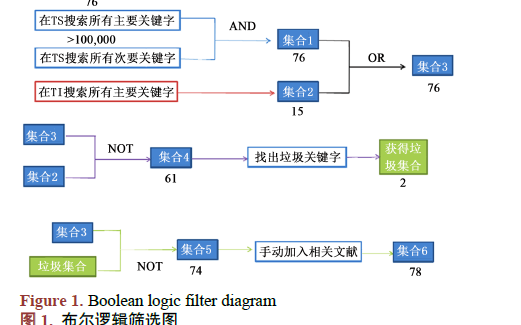

如何使用WOS進(jìn)行負(fù)面口碑發(fā)展之路徑分析

時(shí)序路徑分析提速

FPGA設(shè)計(jì)的常用基本時(shí)序路徑分析

FPGA設(shè)計(jì)的常用基本時(shí)序路徑分析

評論