組合邏輯電路的定義

對于一個邏輯電路,其輸出狀態(tài)在任何時刻只取決于同一時刻的輸入狀態(tài),而與電路原來的狀態(tài)無關(guān),這種電路被定義為組合邏輯電路。

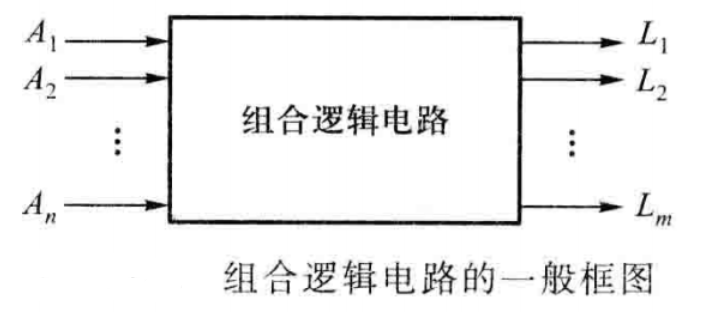

組合邏輯電路的一般框圖如圖

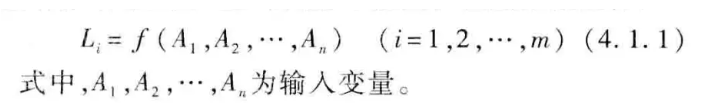

其輸出與輸入之間的邏輯關(guān)系可用如下的邏輯函數(shù)來描述,即

組合邏輯電路的結(jié)構(gòu)具有如下的特點:

(1)輸出、輸入之間沒有反饋延遲通路;

(2)電路中不含具有記憶功能的元件。

【注意】:所謂記憶單元,指的是第五章里提到的鎖存器之類的器件。

組合邏輯電路特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關(guān)。具體來說,組合邏輯電路的輸出是由輸入信號經(jīng)過邏輯門電路后得到的,不包含存儲元件。

組合邏輯電路的分析方法主要包括:

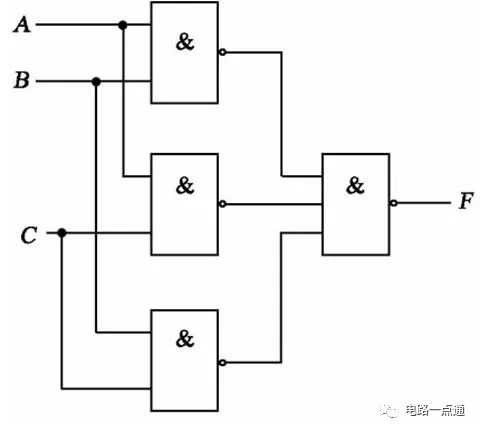

根據(jù)給定的邏輯電路,寫出輸出函數(shù)的邏輯表達式。

進行表達式的變換與化簡,直接利用公式或定理對表達式進行變換,也可通過卡諾圖的方法進行化簡。

根據(jù)表達式列出真值表。真值表能直接反映出輸入變量和輸出結(jié)果之間的邏輯關(guān)系,它直觀地描述了電路的邏輯功能。

對給定電路的功能進行邏輯描述。

常用的組合邏輯電路包括:二進制普通編碼器、BCD普通編碼器、優(yōu)先編碼器等。組合邏輯電路的應用非常廣泛,如計算機的CPU內(nèi)部、各種數(shù)字控制系統(tǒng)、電子儀表、電子通訊等領(lǐng)域的數(shù)字處理中。

組合邏輯電路的分析方法

分析組合邏輯電路的一種常用方法是使用真值表或卡諾圖。以下是這兩種方法的簡要介紹:

1. 真值表方法:

- 首先,列出輸入端口和輸出端口的所有可能值組合,構(gòu)成真值表。

- 對于每個輸入組合,確定對應的輸出值。

- 根據(jù)真值表中的輸出值,找出邏輯門的邏輯運算規(guī)則或布爾表達式。

例如,對于一個有兩個輸入端口和一個輸出端口的邏輯門,可以通過真值表列出所有可能的輸入組合,然后找出對應的輸出值。最后,我們可以根據(jù)真值表中的輸出值得出邏輯門的邏輯規(guī)則。

2. 卡諾圖方法(Karnaugh Map):

- 對于每個輸入端口,構(gòu)建一個表格,并將所有可能的輸入組合填入表格中。

- 分析表格中每一個組合對應的輸出值。

- 根據(jù)卡諾圖中相鄰的1(或0)的分組情況,找出邏輯門的簡化布爾表達式。

卡諾圖是一種直觀且有效的方法,它將二進制數(shù)的輸入組合和邏輯門的輸出用方格表示。通過觀察卡諾圖中相鄰的1(或0)的分組,我們可以識別出邏輯門的簡化布爾表達式,以減少邏輯門的數(shù)量和簡化電路的復雜度。

審核編輯:黃飛

-

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43285 -

編碼器

+關(guān)注

關(guān)注

45文章

3787瀏覽量

137696 -

cpu

+關(guān)注

關(guān)注

68文章

11067瀏覽量

216635

發(fā)布評論請先 登錄

組合邏輯電路的分析、設(shè)計和調(diào)試

組合邏輯電路的分析與設(shè)計-邏輯代數(shù)

組合邏輯電路的設(shè)計

組合邏輯電路設(shè)計步驟詳解(教程)

組合邏輯電路的定義及電路分析方法

組合邏輯電路的定義及電路分析方法

評論