在高速數據傳輸系統中,差分信號作為一種常見的信號傳輸方式,具有抗噪聲能力強、傳輸距離遠等優點。然而,差分信號的傳輸質量受到諸多因素的影響,其中阻抗匹配是確保信號穩定傳輸的關鍵因素之一。本文將詳細探討高速差分信號阻抗匹配的原理、方法及其重要性,以期為工程師和技術人員在實際應用中提供參考。

一、差分信號阻抗匹配的原理

差分信號由兩個相位相反、幅值相等的信號組成,通過差分線進行傳輸。在差分信號傳輸過程中,差分阻抗(Z_{diff})是一個重要的參數,它指的是差分信號在差分對中受到的阻抗。差分阻抗匹配的原理是使差分信號的源端阻抗與傳輸線的特征阻抗相匹配,從而減少信號的反射和失真,提高信號的傳輸質量。

差分阻抗匹配的實現方式有多種,包括串聯端接、并聯端接、戴維寧端接和RC網絡端接等。這些匹配方式各有特點,適用于不同的應用場景。

二、差分信號阻抗匹配的方法

串聯端接

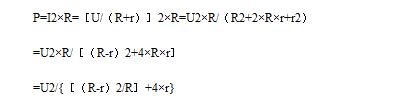

串聯端接是一種常用的差分信號阻抗匹配方法。在信號源端阻抗低于傳輸線特征阻抗的條件下,通過在信號的源端和傳輸線之間串接一個電阻R,使源端的輸出阻抗與傳輸線的特征阻抗相匹配。匹配電阻的選擇原則是使匹配電阻值與驅動器的輸出阻抗之和等于傳輸線的特征阻抗。串聯端接的優點是器件單一、抑制振鈴、減少過沖和增強信號完整性,但缺點是接收端的反向反射依然存在,影響信號上升時間并增加信號延時。

并聯端接

并聯端接是在信號源端阻抗很小的情況下,通過增加并聯電阻使負載端輸入阻抗與傳輸線的特征阻抗相匹配,達到消除負載端反射的目的。并聯端接的實現形式分為單電阻和雙電阻兩種形式。單電阻并聯端接簡單易行,但可能無法完全消除反射;雙電阻并聯端接可以更好地抑制反射,但電路結構相對復雜。

戴維寧端接

戴維寧端接是一種利用戴維寧定理實現的阻抗匹配方法。它通過在傳輸線的末端連接一個等效電路(包括一個電壓源和一個串聯電阻),使得從傳輸線看過去的阻抗與源端阻抗相等。戴維寧端接可以實現較寬的頻帶匹配,但電路結構較為復雜。

RC網絡端接

RC網絡端接是通過在傳輸線的末端連接一個RC網絡(包括一個電阻和一個電容)來實現阻抗匹配的。RC網絡端接可以在較寬的頻帶范圍內實現阻抗匹配,并且可以通過調整RC參數來優化匹配效果。但是,RC網絡端接會增加電路的復雜性和成本。

三、差分信號阻抗匹配的重要性

差分信號阻抗匹配對于高速數據傳輸系統的重要性不言而喻。首先,阻抗匹配可以減少信號的反射和失真,提高信號的傳輸質量和可靠性。在高速數據傳輸中,信號的反射和失真會導致數據丟失和誤碼率增加,嚴重影響系統的性能。其次,阻抗匹配可以保護驅動器免受損壞。當驅動器的輸出阻抗與傳輸線的特征阻抗不匹配時,驅動器可能會承受過大的電壓或電流,從而導致損壞。最后,阻抗匹配還可以降低系統的電磁干擾(EMI)和射頻干擾(RFI)水平。通過優化阻抗匹配,可以減少系統中的噪聲和干擾,提高系統的穩定性和可靠性。

四、總結與展望

高速差分信號阻抗匹配是確保高速數據傳輸系統穩定傳輸的關鍵因素之一。本文詳細介紹了差分信號阻抗匹配的原理、方法及其重要性,并探討了不同匹配方式的特點和應用場景。在實際應用中,工程師和技術人員應根據具體的應用需求選擇合適的匹配方式,并注意優化匹配效果以提高系統的性能和穩定性。

隨著電子技術的不斷發展和高速數據傳輸系統的廣泛應用,差分信號阻抗匹配技術也將不斷發展和完善。未來,我們可以期待更先進的阻抗匹配方法和更高效的優化算法的出現,以滿足日益增長的數據傳輸需求。

-

阻抗匹配

+關注

關注

14文章

358瀏覽量

31295 -

差分信號

+關注

關注

4文章

392瀏覽量

28143

發布評論請先 登錄

詳解高速PCB設計中的阻抗匹配

高速PCB中的阻抗匹配

高速差分信號阻抗匹配詳解

高速差分信號阻抗匹配詳解

評論