在拯救摩爾定律的道路上,大家似乎都卯足了勁。不久前,IBM宣布研發成功7nm芯片,而現在,又有研發團隊宣稱制備成功了有史以來最小的晶體管——只有單個分子大小。

實現這一驚人成就的是來自一支德國、日本和美國的聯合研究團隊,他們在砷化銦晶體襯底上使用12個帶正電的銦原子環繞一個酞菁分子,然后就得到了一個晶體管。

早在2012年,IBM就宣稱成功將單個比特的信息集成到了12個原子構成的結構上,而這一次晶體管的制備成功又是在這一基礎上的巨大飛躍。這個晶體管直徑僅為167皮米(10-12米),比之前最小的電路還要小42倍。

這一成就的基礎是研究人員意外發現酞菁分子的取向會受到其上電荷的影響,然后通過掃描隧道電子顯微鏡的電子流限制銦原子的運動,將銦原子精確地限制在特定的柵格內。

但是這一研究成果還處于早期階段,實用化還遙遙無期,但這一研究成果鋪平了實現大規模量子計算的道路,但具體的情況還有待進一步驗證。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

IBM

+關注

關注

3文章

1810瀏覽量

75512 -

摩爾定律

+關注

關注

4文章

638瀏覽量

79708 -

晶體管

+關注

關注

77文章

9989瀏覽量

140802

發布評論請先 登錄

相關推薦

熱點推薦

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電子發燒友網報道(文/黃山明)在半導體行業邁向3nm及以下節點的今天,光刻工藝的精度與效率已成為決定芯片性能與成本的核心要素。光刻掩模作為光刻技術的“底片”,其設計質量直接決定了晶體管結構的精準度

玻璃基板在芯片封裝中的應用

自集成電路誕生以來,摩爾定律一直是其發展的核心驅動力。根據摩爾定律,集成電路單位面積上的晶體管數量每18到24個月翻一番,性能也隨之提升。然而,隨著晶體管尺寸的不斷縮小,制造工藝的復雜

多值電場型電壓選擇晶體管結構

,有沒有一種簡單且有效的器件實現對電壓的選擇呢?本文將介紹一種電場型多值電壓選擇晶體管,之所以叫電壓型,是因為通過調控晶體管內建電場大小來實現對電壓的選擇,原理是PN結有內建電場,通過外加電場來增大或減小

發表于 04-15 10:24

混合鍵合中的銅連接:或成摩爾定律救星

將兩塊或多塊芯片疊放在同一個封裝中。這使芯片制造商能夠增加處理器和內存中的晶體管數量,雖然晶體管的縮小速度已普遍放緩,但這曾推動摩爾定律發展。2024年5月,在美國丹佛舉行的IEEE電子器件與技術大會(ECTC)上,來自

互補場效應晶體管的結構和作用

, Gate-all-Around)全環繞柵極晶體管(GAAFET)等先進結構,在減少漏電、降低功耗方面雖然取得了顯著成就,但進一步微縮的挑戰日益顯現。為了延續摩爾定律的發展趨勢,并滿足未來高性能計算的需求,業界正積極研發下一代晶體管

石墨烯互連技術:延續摩爾定律的新希望

半導體行業長期秉持的摩爾定律(該定律規定芯片上的晶體管密度大約每兩年應翻一番)越來越難以維持。縮小晶體管及其間互連的能力正遭遇一些基本的物理限制。特別是,當銅互連按比例縮小時,其電阻率

摩爾定律是什么 影響了我們哪些方面

摩爾定律是由英特爾公司創始人戈登·摩爾提出的,它揭示了集成電路上可容納的晶體管數量大約每18-24個月增加一倍的趨勢。該定律不僅推動了計算機硬件的快速發展,也對多個領域產生了深遠影響。

晶體管與場效應管的區別 晶體管的封裝類型及其特點

晶體管與場效應管的區別 工作原理 : 晶體管 :晶體管(BJT)基于雙極型晶體管的原理,即通過控制基極電流來控制集電極和發射極之間的電流。

奇異摩爾專用DSA加速解決方案重塑人工智能與高性能計算

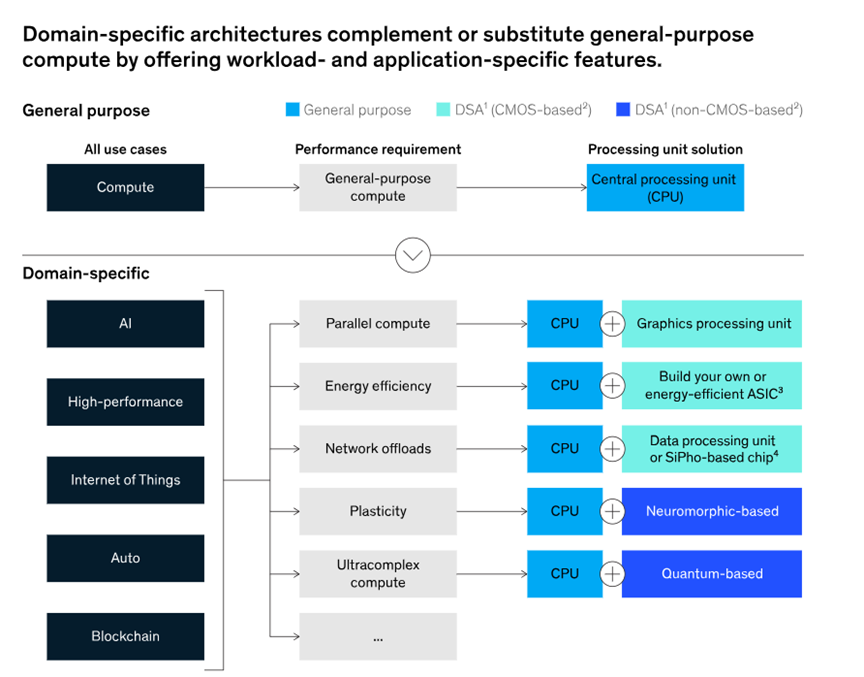

隨著摩爾定律下的晶體管縮放速度放緩,單純依靠增加晶體管密度的通用計算的邊際效益不斷遞減,促使專用計算日益多樣化,于是,針對特定計算任務的專用架構成為計算創新的焦點。

NMOS晶體管和PMOS晶體管的區別

NMOS晶體管和PMOS晶體管是兩種常見的金屬氧化物半導體場效應晶體管(MOSFET)類型,它們在多個方面存在顯著的差異。以下將從結構、工作原理、性能特點、應用場景等方面詳細闡述NMOS晶體管

“自我實現的預言”摩爾定律,如何繼續引領創新

未來的自己制定了一個遠大但切實可行的目標一樣, 摩爾定律是半導體行業的自我實現 。雖然被譽為技術創新的“黃金法則”,但一些事情尚未廣為人知……. 1.?戈登·摩爾完善過摩爾定律的定義 在1965年的文章中,戈登·

拯救摩爾定律!僅分子大小世界最小晶體管問世

拯救摩爾定律!僅分子大小世界最小晶體管問世

評論