神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)是人工智能領(lǐng)域的一個(gè)重要研究方向,旨在通過(guò)設(shè)計(jì)專門的硬件來(lái)加速神經(jīng)網(wǎng)絡(luò)的訓(xùn)練和推理過(guò)程,提高計(jì)算效率和能效比。以下將詳細(xì)介紹神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)的方法和技術(shù),并附上相關(guān)的代碼示例。

一、神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)的主要方法

- FPGA(現(xiàn)場(chǎng)可編程門陣列)實(shí)現(xiàn)

FPGA是一種半定制電路,具有大量的通用邏輯單元和可編程的連接。通過(guò)編程,F(xiàn)PGA可以實(shí)現(xiàn)特定的神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)和算法,從而加速神經(jīng)網(wǎng)絡(luò)的計(jì)算。FPGA的優(yōu)點(diǎn)在于其可重配置性和高并行性,非常適合于實(shí)現(xiàn)復(fù)雜的神經(jīng)網(wǎng)絡(luò)模型。

代碼示例 (假設(shè)使用Verilog或VHDL語(yǔ)言):

// 示例:FPGA實(shí)現(xiàn)簡(jiǎn)單的神經(jīng)網(wǎng)絡(luò)層

module neural_layer(

input wire [7:0] in_data[16:0], // 假設(shè)有17個(gè)8位輸入

input wire [7:0] weights[16:0][8:0], // 權(quán)重,假設(shè)每個(gè)神經(jīng)元連接9個(gè)輸入(包括偏置)

output reg [7:0] out_data[8:0] // 假設(shè)有9個(gè)神經(jīng)元輸出

);

// 激活函數(shù)(簡(jiǎn)單示例,實(shí)際應(yīng)用中可能需要更復(fù)雜的實(shí)現(xiàn))

always @(in_data, weights) begin

for (int i = 0; i < 9; i = i + 1) begin

integer sum = 0;

for (int j = 0; j < 17; j = j + 1) begin

sum = sum + (in_data[j] * weights[j][i]);

end

// 添加偏置(這里假設(shè)weights[16][i]為偏置)

sum = sum + weights[16][i];

// 簡(jiǎn)單的ReLU激活函數(shù)

if (sum > 0)

out_data[i] = sum;

else

out_data[i] = 0;

end

end

endmodule

- ASIC(應(yīng)用特定集成電路)實(shí)現(xiàn)

ASIC是為特定應(yīng)用定制的集成電路,與FPGA相比,ASIC具有更高的性能和更低的功耗,但設(shè)計(jì)成本和時(shí)間也更高。神經(jīng)網(wǎng)絡(luò)處理器(NNP)和神經(jīng)網(wǎng)絡(luò)加速器(NNA)是典型的ASIC實(shí)現(xiàn)方式。

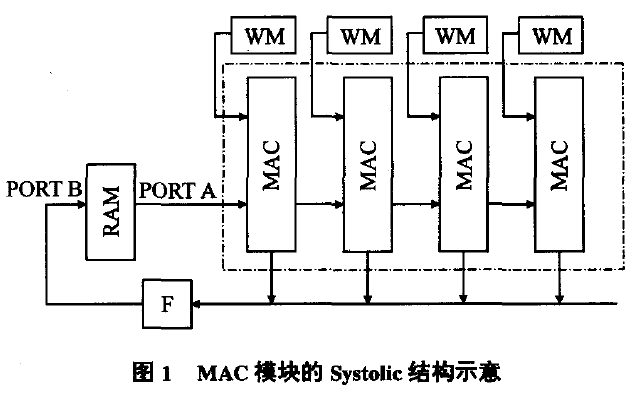

描述 :NNP和NNA通常包含多個(gè)處理單元(PE),每個(gè)PE可以執(zhí)行神經(jīng)網(wǎng)絡(luò)中的基本計(jì)算(如乘法累加、激活函數(shù)等)。這些處理單元通過(guò)高效的數(shù)據(jù)通路和內(nèi)存結(jié)構(gòu)連接,以實(shí)現(xiàn)高并行度的計(jì)算。 - GPU(圖形處理器)和TPU(張量處理器)

GPU和TPU雖然不是專門為神經(jīng)網(wǎng)絡(luò)設(shè)計(jì)的硬件,但由于其強(qiáng)大的并行計(jì)算能力,被廣泛應(yīng)用于神經(jīng)網(wǎng)絡(luò)的訓(xùn)練和推理中。GPU擅長(zhǎng)處理大規(guī)模并行浮點(diǎn)數(shù)運(yùn)算,而TPU則針對(duì)機(jī)器學(xué)習(xí)進(jìn)行了專門的優(yōu)化。

描述 :GPU通過(guò)大量的計(jì)算核心(CUDA核心或流處理器)和高速顯存,可以同時(shí)處理大量的神經(jīng)網(wǎng)絡(luò)計(jì)算任務(wù)。TPU則通過(guò)其專門的矩陣乘法單元和高效的內(nèi)存管理,進(jìn)一步提高了神經(jīng)網(wǎng)絡(luò)的計(jì)算效率。 - 光處理器和量子處理器

光處理器和量子處理器是新興的神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)方式,它們利用光學(xué)和量子物理學(xué)的原理來(lái)實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的計(jì)算。這些技術(shù)仍處于研究階段,但具有巨大的潛力。

描述 :光處理器利用光子的高速傳輸和并行處理能力,可以實(shí)現(xiàn)超高速的神經(jīng)網(wǎng)絡(luò)計(jì)算。量子處理器則利用量子比特的疊加和糾纏特性,實(shí)現(xiàn)比經(jīng)典計(jì)算機(jī)更高效的計(jì)算。

二、神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)的技術(shù)

- 并行計(jì)算技術(shù)

神經(jīng)網(wǎng)絡(luò)計(jì)算具有高度并行的特點(diǎn),因此并行計(jì)算技術(shù)是神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)的關(guān)鍵。通過(guò)設(shè)計(jì)高效的并行計(jì)算架構(gòu)和算法,可以顯著提高神經(jīng)網(wǎng)絡(luò)的計(jì)算效率。 - 數(shù)據(jù)量化與低精度計(jì)算

神經(jīng)網(wǎng)絡(luò)模型通常使用浮點(diǎn)數(shù)進(jìn)行計(jì)算,但浮點(diǎn)數(shù)計(jì)算需要較高的計(jì)算資源和能耗。通過(guò)將模型參數(shù)和計(jì)算過(guò)程進(jìn)行量化和低精度化(如使用8位或16位整數(shù)代替32位浮點(diǎn)數(shù)),可以減少計(jì)算和存儲(chǔ)開(kāi)銷,提高神經(jīng)網(wǎng)絡(luò)的運(yùn)行速度。 - 模型剪枝與壓縮

神經(jīng)網(wǎng)絡(luò)模型通常具有大量的參數(shù)和冗余連接,這導(dǎo)致了計(jì)算和存儲(chǔ)開(kāi)銷的增加。通過(guò)模型剪枝和壓縮技術(shù),可以去除冗余的參數(shù)和連接,從而減少模型的大小和計(jì)算量,提高模型的運(yùn)行效率。 - 存儲(chǔ)優(yōu)化技術(shù)

神經(jīng)網(wǎng)絡(luò)計(jì)算需要大量的內(nèi)存來(lái)存儲(chǔ)權(quán)重、輸入數(shù)據(jù)和中間結(jié)果。通過(guò)設(shè)計(jì)高效的存儲(chǔ)結(jié)構(gòu)和數(shù)據(jù)訪問(wèn)模式(如使用緩存、數(shù)據(jù)重用等),可以減少內(nèi)存訪問(wèn)次數(shù)和降低數(shù)據(jù)移動(dòng)的開(kāi)銷,從而提高神經(jīng)網(wǎng)絡(luò)的執(zhí)行效率。 - 定制化指令集

為了進(jìn)一步提高神經(jīng)網(wǎng)絡(luò)的計(jì)算效率,許多神經(jīng)網(wǎng)絡(luò)專用硬件會(huì)設(shè)計(jì)定制化的指令集。這些指令集針對(duì)神經(jīng)網(wǎng)絡(luò)中常見(jiàn)的計(jì)算模式進(jìn)行了優(yōu)化,如矩陣乘法、卷積操作、池化操作等。通過(guò)使用這些定制化指令,可以減少指令數(shù)量和計(jì)算延遲,提高硬件的利用率和性能。 - 自動(dòng)化設(shè)計(jì)工具

隨著神經(jīng)網(wǎng)絡(luò)硬件的復(fù)雜性增加,手動(dòng)設(shè)計(jì)硬件變得越來(lái)越困難且耗時(shí)。因此,自動(dòng)化設(shè)計(jì)工具在神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)中發(fā)揮著越來(lái)越重要的作用。這些工具可以根據(jù)神經(jīng)網(wǎng)絡(luò)的架構(gòu)和需求,自動(dòng)生成硬件描述語(yǔ)言(HDL)代碼或布局布線文件,大大簡(jiǎn)化了設(shè)計(jì)流程并提高了設(shè)計(jì)效率。 - 電源管理和熱管理技術(shù)

神經(jīng)網(wǎng)絡(luò)專用硬件通常需要處理大量的數(shù)據(jù)和計(jì)算任務(wù),這會(huì)導(dǎo)致較高的功耗和熱量產(chǎn)生。因此,電源管理和熱管理技術(shù)對(duì)于確保硬件的穩(wěn)定運(yùn)行和延長(zhǎng)使用壽命至關(guān)重要。這些技術(shù)包括動(dòng)態(tài)電壓頻率調(diào)整(DVFS)、低功耗待機(jī)模式、以及有效的散熱設(shè)計(jì)等。

三、未來(lái)趨勢(shì)和展望

- 異構(gòu)計(jì)算

隨著神經(jīng)網(wǎng)絡(luò)應(yīng)用的不斷擴(kuò)展,單一類型的硬件已經(jīng)難以滿足所有需求。因此,異構(gòu)計(jì)算成為了一個(gè)重要的趨勢(shì)。通過(guò)將不同類型的硬件(如GPU、FPGA、ASIC等)組合在一起,可以充分發(fā)揮各自的優(yōu)勢(shì),實(shí)現(xiàn)更高效的神經(jīng)網(wǎng)絡(luò)計(jì)算。 - 邊緣計(jì)算

隨著物聯(lián)網(wǎng)和智能設(shè)備的普及,邊緣計(jì)算變得越來(lái)越重要。將神經(jīng)網(wǎng)絡(luò)模型部署到邊緣設(shè)備上,可以實(shí)現(xiàn)更快的響應(yīng)時(shí)間和更低的延遲。因此,未來(lái)神經(jīng)網(wǎng)絡(luò)專用硬件將更加注重低功耗、小體積和高效能的設(shè)計(jì),以適應(yīng)邊緣計(jì)算的需求。 - 可重構(gòu)計(jì)算

可重構(gòu)計(jì)算是一種介于FPGA和ASIC之間的硬件實(shí)現(xiàn)方式。它可以在運(yùn)行時(shí)動(dòng)態(tài)地改變硬件的配置,以適應(yīng)不同的計(jì)算任務(wù)。這種靈活性使得可重構(gòu)計(jì)算在神經(jīng)網(wǎng)絡(luò)專用硬件中具有很大的潛力,可以根據(jù)不同的網(wǎng)絡(luò)結(jié)構(gòu)和應(yīng)用需求進(jìn)行優(yōu)化。 - 新型材料和技術(shù)

隨著新型材料和技術(shù)的發(fā)展,如量子計(jì)算、光計(jì)算、神經(jīng)形態(tài)計(jì)算等,未來(lái)神經(jīng)網(wǎng)絡(luò)專用硬件的實(shí)現(xiàn)方式也將發(fā)生革命性的變化。這些新技術(shù)有望帶來(lái)更高的計(jì)算速度和更低的能耗,為神經(jīng)網(wǎng)絡(luò)的發(fā)展提供新的動(dòng)力。

結(jié)論

神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)是人工智能領(lǐng)域的一個(gè)重要研究方向,通過(guò)設(shè)計(jì)專門的硬件來(lái)加速神經(jīng)網(wǎng)絡(luò)的訓(xùn)練和推理過(guò)程,可以顯著提高計(jì)算效率和能效比。本文介紹了神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)的主要方法和技術(shù),包括FPGA、ASIC、GPU/TPU、光處理器和量子處理器等,并探討了并行計(jì)算、數(shù)據(jù)量化與低精度計(jì)算、模型剪枝與壓縮、存儲(chǔ)優(yōu)化、定制化指令集、自動(dòng)化設(shè)計(jì)工具以及電源管理和熱管理等技術(shù)。同時(shí),本文還展望了神經(jīng)網(wǎng)絡(luò)專用硬件的未來(lái)趨勢(shì)和發(fā)展方向,包括異構(gòu)計(jì)算、邊緣計(jì)算、可重構(gòu)計(jì)算以及新型材料和技術(shù)等。隨著技術(shù)的不斷進(jìn)步和創(chuàng)新,相信神經(jīng)網(wǎng)絡(luò)專用硬件將在未來(lái)的人工智能應(yīng)用中發(fā)揮更加重要的作用。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22020瀏覽量

617075 -

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4812瀏覽量

103292 -

人工智能

+關(guān)注

關(guān)注

1805文章

48940瀏覽量

248322

發(fā)布評(píng)論請(qǐng)先 登錄

labview BP神經(jīng)網(wǎng)絡(luò)的實(shí)現(xiàn)

基于賽靈思FPGA的卷積神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)設(shè)計(jì)

人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法有哪些?

如何設(shè)計(jì)BP神經(jīng)網(wǎng)絡(luò)圖像壓縮算法?

基于FPGA的神經(jīng)網(wǎng)絡(luò)的性能評(píng)估及局限性

如何構(gòu)建神經(jīng)網(wǎng)絡(luò)?

matlab實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò) 精選資料分享

神經(jīng)網(wǎng)絡(luò)移植到STM32的方法

基于FPGA的人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法的研究

基于FPGA的人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法的研究

如何使用FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)硬件的設(shè)計(jì)方法

基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)

基于FPGA的神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)方法

基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)的硬件實(shí)現(xiàn)

神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)的方法和技術(shù)

神經(jīng)網(wǎng)絡(luò)專用硬件實(shí)現(xiàn)的方法和技術(shù)

評(píng)論