原創(chuàng):DrChip芯片行業(yè)

隨著先進封裝技術的發(fā)展,翹曲問題日益嚴重。這種現(xiàn)象通常由多種材料混合造成的不均勻應力點引起,影響封裝的組裝和實際使用中的長期可靠性。

翹曲在確定先進封裝是否能夠成功組裝以及滿足長期可靠性目標方面扮演了關鍵角色。新進展,如改進了熱性能的模塑材料、高級建模技術以及涉及兩步模塑的創(chuàng)新架構,正在使對封裝翹曲的控制變得更加有效,同時也提供了優(yōu)化多芯片系統(tǒng)的更大靈活性。

翹曲是由硅芯片、模塑材料、銅、聚酰亞胺等材料之間的熱膨脹系數(shù)(CTE)不匹配所導致的必然結果。它在整個組裝過程中變化不定,可能會導致裂紋或剝離失效。最容易出現(xiàn)問題的區(qū)域包括低介電常數(shù)核心,這些區(qū)域容易發(fā)生裂紋和短路,或者在微凸點中出現(xiàn)非濕潤失效。

“目前關于封裝翹曲和應力的討論非常熱門,”Synopsys產(chǎn)品管理高級總監(jiān)Kenneth Larsen表示,“這不僅僅是在制造過程中,溫度變化可能導致翹曲,還包括當你將設備插入插座時,可能會遇到翹曲問題。”

即便在組裝和封裝過程中有效地解決了翹曲問題,設備在實際使用中仍可能出現(xiàn)翹曲。這在異質(zhì)設計中尤其明顯,其中芯片采用不同材料或工藝,而邏輯集中在不對稱封裝的特定區(qū)域。

由于對更高處理速度和低延遲的需求,尤其是在移動、汽車和高性能計算/AI應用中,多芯片封裝的過渡正迅速加速。工程師們越來越依賴建模和仿真來理解溫度依賴的翹曲,這種翹曲可能因芯片厚度、模具與硅比例及基板類型而異。盡管有機基板因其價格低廉且可以定制到任何尺寸而非常有吸引力,但它們比硅基板更具柔韌性,容易發(fā)生翹曲。

所有這些考慮都指向了對復雜異質(zhì)組裝和封裝進行熱學和結構建模的必要性。“高級建模允許公司模擬不同材料、熱動態(tài)和機械應力在組裝過程中的行為,”Amkor芯片/FCBGA集成副總裁Mike Kelly表示,“通過這種虛擬實驗,可以預測和緩解潛在挑戰(zhàn),確保最終產(chǎn)品滿足嚴格的質(zhì)量和可靠性標準。”

翹曲的發(fā)生機制

組裝過程中包含多個加熱和冷卻步驟,這會在具有不同熱和機械性能的相鄰材料之間引起一定程度的變形。在先進封裝中,100微米范圍的翹曲并不罕見。

翹曲問題的一個原因是芯片的尺寸較大,而芯片、重新分布層(RDL)、基板和各種尺寸的凸點的加工窗口非常緊湊。相鄰材料的膨脹和收縮取決于材料的CTE,即每度溫度變化引起的尺寸增加(ppm/°C)。

“芯片通常是相對較大的芯片,”Promex Industries首席執(zhí)行官Dick Otte表示,“例如iPad中,芯片尺寸為20 x 30毫米,可能有多達10,000個I/O,通常為銅柱。僅僅將單個芯片放置在基板上就可能是一個挑戰(zhàn),因為間距非常小。因此,對于這些組裝而言,控制翹曲和平整度至關重要。在整個回流焊接過程中,它需要保持平整,以彌合銅柱與電路板上的接觸點之間的間隙而不發(fā)生翹曲。”

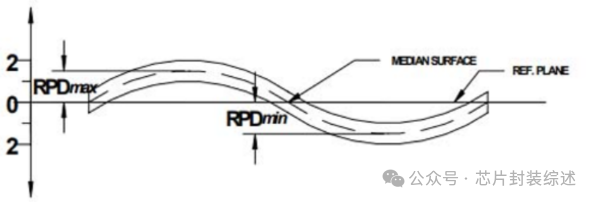

翹曲可以向上發(fā)生(邊緣彎曲,稱為“微笑”),也可以向下發(fā)生(稱為“哭泣”),這取決于堆疊材料的相對CTE。例如,硅的CTE為2.8,銅為17,F(xiàn)R4 PCB為14至17 ppm/°C。硅互連層與有機基板之間的CTE不匹配最為嚴重。

將封裝堆疊視作材料組合有助于理解這一現(xiàn)象。“你需要考慮材料的CTE及其在溫度下的反應,”O(jiān)tte說,“比如你在上面有相對低膨脹的銅,而底部有焊料,它們的膨脹量基本相等,中間則有一個高膨脹的介電材料,所以當你加熱它時,它的膨脹量也大致相同。如果你把所有的銅放在上面,當你加熱它時,它會向銅的一側(cè)翹曲。銅的CTE是15 ppm/°C,而有機材料的CTE大約是其兩倍,25到30 ppm/°C。”

其他關鍵指標包括材料的模量或彈性,以及玻璃化轉(zhuǎn)變溫度(Tg),即材料開始流動的溫度。這些值也是相關的。例如,聚合物(如環(huán)氧模塑化合物(EMC))的熱行為中,當溫度超過玻璃化轉(zhuǎn)變溫度時,模量通常會急劇下降。這是因為在液態(tài)時,聚合物鏈會自由滑動,而在固態(tài)時則較為剛性。

除了焊料回流外,翹曲還常發(fā)生在模塑后固化階段。ASE的Hung-Chun Yang及其同事最近發(fā)現(xiàn),芯片厚度對現(xiàn)有芯片優(yōu)先流封裝過程中的翹曲水平有顯著影響。研究表明,“固化后出現(xiàn)嚴重的晶圓翹曲,導致對齊失效并在后續(xù)工藝中處理困難。”為減少封裝翹曲,團隊用玻璃載體替代了金屬載體/薄膜方案。團隊還發(fā)現(xiàn),3D有限元法(FEM)能夠捕捉翹曲行為,并與實際測試數(shù)據(jù)相符。

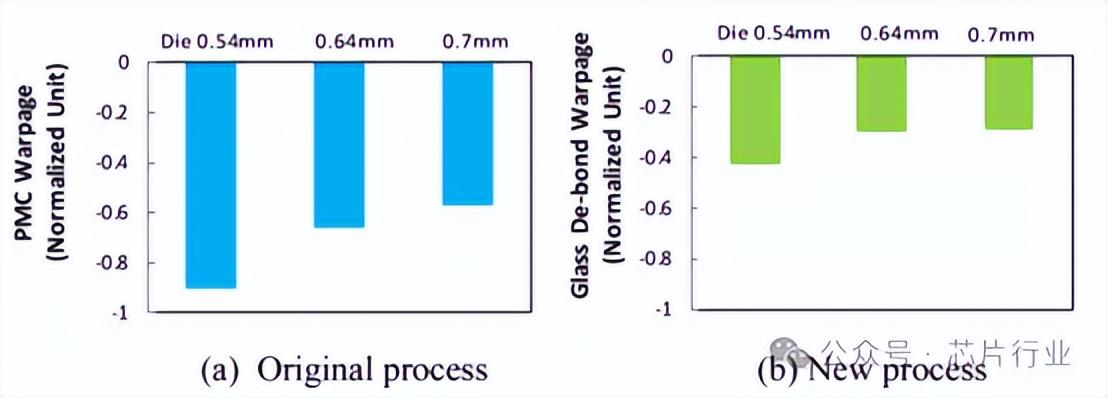

圖1:改進流程中的玻璃載體(右)引起的翹曲較少。增加芯片厚度也顯著減少了翹曲。來源:ASE

芯片優(yōu)先流程從探測制造好的晶圓開始,隨后對其進行薄化并電鍍銅柱,然后切割并放置已知良品的芯片。最初的流程使用了一個金屬載體,該載體在模塑后被去除,替換為薄膜。改進后的流程使用了一個在模塑、固化、模具磨削、RDL和銅柱處理過程中都保持在位的玻璃載體,然后再進行脫粘。

在模塑后固化過程中,翹曲達到最大值,并且在固化步驟和玻璃載體脫粘后變化最為顯著。玻璃載體流程總體上減少了翹曲。此外,ASE工程師確定,通過將晶圓厚度從0.54毫米增加到0.7毫米,可以額外減少35%的翹曲。

第二種減少翹曲的策略是使用具有不同熱性能的EMC,特別是在工藝需要兩步模塑時。Amkor工程師最近通過建模和制造兩個高性能測試樣本評估了兩種高性能多芯片封裝的可靠性表現(xiàn)。一個模塊大約是一個掩模的大小,包含1個ASIC、2個HBM和2個橋接芯片(33 x 26毫米)。第二個模塊為三個掩模的大小,包含2個ASIC、8個HBM和10個橋接芯片(54 x 46毫米)。Heejun Jang及其同事在Amkor Technology Korea使用Ansys Parametric Design Language(APDL)版本16.1進行建模和仿真,并將結果與包含虛擬芯片的測試樣本進行了比較。

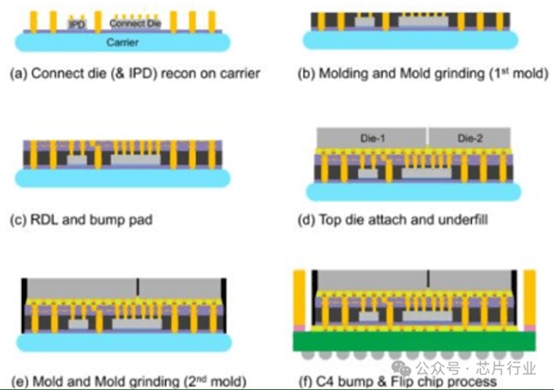

Amkor的“最后封裝”S-Connect流程從載體晶圓開始,制造用于橋接芯片和銅柱的銅柱(見圖2)。集成的被動器件和橋接芯片被嵌入第一模具中,該模具固化后被磨回。RDL沉積在模具上,焊料捕集墊和芯片通過微凸點附著在墊上。然后,焊料被回流和填充。第二模具圍繞正面芯片固化并磨回,然后進行C4凸點加工以實現(xiàn)與基板的翻轉(zhuǎn)連接。仿真分析了9種不同CTE(7到12 ppm Tg以下,22到46 ppm Tg以上)和高至低玻璃化轉(zhuǎn)變溫度(145°C到175°C)的EMC組合下的翹曲情況。

圖2:S-Connect封裝的工藝流程。來源:Amkor

翹曲作為EMC選擇的函數(shù)表明,所有材料在室溫下表現(xiàn)出相同的微笑模式,在高溫(250°C)下表現(xiàn)出哭泣模式。CTE較低的EMC導致的翹曲較少。在模具占據(jù)相對較大區(qū)域時,翹曲水平更加明顯。更重要的是,相對于450μm的芯片,650μm厚的芯片翹曲水平大約高出50%。有趣的是,較厚的硅芯片在控制總體模塊翹曲方面的效果是EMC材料選擇的3倍,因此芯片厚度是減少翹曲的最大杠桿因素。

一旦確定了封裝配置,可靠性測試至關重要。Amkor對其先進封裝測試樣本進行了濕氣抵抗測試、高加速應力測試、熱循環(huán)B條件和高溫存儲測試。這些測試是發(fā)現(xiàn)早期失效問題所必需的,橫截面分析可以揭示可能導致實際使用中故障的裂紋或潛在缺陷。

盡管上述例子可能代表了今天的大型多芯片封裝,但封裝尺寸正在不斷增長,這意味著需要更多關注翹曲問題。越來越多的組裝線將推動數(shù)字雙胞胎或虛擬表示的應用,以實現(xiàn)工藝和封裝優(yōu)化。

“通過創(chuàng)建半導體組裝線的虛擬表示,可以識別潛在的關注點并優(yōu)化控制策略,”Amkor的Kelly表示,“在物理原型甚至尚未創(chuàng)建之前,虛擬制造可以幫助公司評估設計更改對制造過程的影響。這不僅加快了產(chǎn)品開發(fā)周期,還減少了昂貴錯誤的風險。”

及早識別潛在的瓶頸進一步縮短了周期時間,并提升了整體效率。

結論

未來,設計師和封裝工程師團隊將需要更加關注機械和熱學屬性。“新的封裝設計要求在堆疊過程中對機械和電氣公差進行準確分析,”Amkor工程與技術營銷副總裁Curtis Zwenger表示,“隨著工藝能力的要求不斷提高,像CpK這樣的常見指標也越來越重要。通過這種類型的建模,可以在工藝開發(fā)的早期識別這些關鍵交互,從而指導先進工藝控制的投資,確保工藝能力得到保持。”

【近期會議】

10月30-31日,由寬禁帶半導體國家工程研究中心主辦的“化合物半導體先進技術及應用大會”將首次與大家在江蘇·常州相見,邀您齊聚常州新城希爾頓酒店,解耦產(chǎn)業(yè)鏈市場布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二屆半導體先進封測產(chǎn)業(yè)技術創(chuàng)新大會”將再次與各位相見于廈門,秉承“延續(xù)去年,創(chuàng)新今年”的思想,仍將由云天半導體與廈門大學聯(lián)合主辦,雅時國際商訊承辦,邀您齊聚廈門·海滄融信華邑酒店共探行業(yè)發(fā)展!誠邀您報名參會:https://w.lwc.cn/s/n6FFne

聲明:本網(wǎng)站部分文章轉(zhuǎn)載自網(wǎng)絡,轉(zhuǎn)發(fā)僅為更大范圍傳播。 轉(zhuǎn)載文章版權歸原作者所有,如有異議,請聯(lián)系我們修改或刪除。聯(lián)系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

芯片

+關注

關注

460文章

52529瀏覽量

441314 -

晶圓

+關注

關注

53文章

5166瀏覽量

129845 -

先進封裝

+關注

關注

2文章

476瀏覽量

636

發(fā)布評論請先 登錄

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數(shù)據(jù)測量的設備

wafer晶圓幾何形貌測量系統(tǒng):厚度(THK)翹曲度(Warp)彎曲度(Bow)等數(shù)據(jù)測量

wafer晶圓幾何形貌測量系統(tǒng):厚度(THK)翹曲度(Warp)彎曲度(Bow)等數(shù)據(jù)測量

晶圓為什么要減薄

深入剖析:封裝工藝對硅片翹曲的復雜影響

深入剖析PCB翹曲現(xiàn)象:成因、危害與預防策略

晶圓微凸點技術在先進封裝中的應用

先進封裝晶圓翹曲控制!

先進封裝晶圓翹曲控制!

評論