MCU微課堂

第五十二期 2025.02.18

DMA簡(jiǎn)介

直接存儲(chǔ)器存取(DMA)用來(lái)提供在外設(shè)和存儲(chǔ)器之間或者存儲(chǔ)器和存儲(chǔ)器之間的高速數(shù)據(jù)傳輸。無(wú)須CPU干預(yù),數(shù)據(jù)可以通過(guò)DMA快速地移動(dòng),這就節(jié)省了CPU的資源來(lái)做其他操作。兩個(gè)DMA控制器有12個(gè)通道(DMA1有7個(gè)通道,DMA2有5個(gè)通道),每個(gè)通道專門(mén)用來(lái)管理來(lái)自于一個(gè)或多個(gè)外設(shè)對(duì)存儲(chǔ)器訪問(wèn)的請(qǐng)求。還有一個(gè)仲裁器來(lái)協(xié)調(diào)各個(gè)DMA請(qǐng)求的優(yōu)先權(quán)。

DMA主要特性

12個(gè)獨(dú)立的可配置的通道(請(qǐng)求):DMA1有7個(gè)通道,DMA2有5個(gè)通道;

每個(gè)通道都直接連接專用的硬件DMA請(qǐng)求,每個(gè)通道都同樣支持軟件觸發(fā)。這些功能通過(guò)軟件來(lái)配置;

在同一個(gè)DMA模塊上,多個(gè)請(qǐng)求間的優(yōu)先權(quán)可以通過(guò)軟件編程設(shè)置(共有四級(jí):很高、高、中等和低),優(yōu)先權(quán)設(shè)置相等時(shí)由硬件決定(請(qǐng)求0優(yōu)先于請(qǐng)求1,依此類推);

獨(dú)立數(shù)據(jù)源和目標(biāo)數(shù)據(jù)區(qū)的傳輸寬度(字節(jié)、半字、全字),模擬打包和拆包的過(guò)程。源和目標(biāo)地址必須按數(shù)據(jù)傳輸寬度對(duì)齊;

支持循環(huán)的緩沖器管理;

每個(gè)通道都有3個(gè)事件標(biāo)志(DMA半傳輸、DMA傳輸完成和DMA傳輸出錯(cuò)),這3個(gè)事件標(biāo)志邏輯或成為一個(gè)單獨(dú)的中斷請(qǐng)求;

存儲(chǔ)器和存儲(chǔ)器間的傳輸;

外設(shè)和存儲(chǔ)器、存儲(chǔ)器和外設(shè)之間的傳輸;

閃存、SRAM、外設(shè)的SRAM、APB1、APB2和AHB外設(shè)均可作為訪問(wèn)的源和目標(biāo);

可編程的數(shù)據(jù)傳輸數(shù)目:最大為65535。

DMA通道

每個(gè)通道都可以在有固定地址的外設(shè)寄存器和存儲(chǔ)器地址之間執(zhí)行DMA傳輸。DMA傳輸?shù)臄?shù)據(jù)量是可編程的,最大達(dá)到65535。包含要傳輸?shù)臄?shù)據(jù)項(xiàng)數(shù)量的寄存器,在每次傳輸后遞減。

1、可編程的數(shù)據(jù)量

外設(shè)和存儲(chǔ)器的傳輸數(shù)據(jù)量可以通過(guò)DMA_CCRx寄存器中的PSIZE和MSIZE位編程。

2、指針增量

通過(guò)設(shè)置DMA_CCRx寄存器中的PINC和MINC標(biāo)志位,外設(shè)和存儲(chǔ)器的指針在每次傳輸后可以有選擇地完成自動(dòng)增量。當(dāng)設(shè)置為增量模式時(shí),下一個(gè)要傳輸?shù)牡刂穼⑹乔耙粋€(gè)地址加上增量值,增量值取決與所選的數(shù)據(jù)寬度為1、2或4。第一個(gè)傳輸?shù)牡刂肥谴娣旁贒MA_CPARx/DMA_CMARx寄存器中地址。在傳輸過(guò)程中,這些寄存器保持它們初始的數(shù)值,軟件不能改變和讀出當(dāng)前正在傳輸?shù)牡刂?它在內(nèi)部的當(dāng)前外設(shè)/存儲(chǔ)器地址寄存器中)。

當(dāng)通道配置為非循環(huán)模式時(shí),傳輸結(jié)束后(即傳輸計(jì)數(shù)變?yōu)?)將不再產(chǎn)生DMA操作。要開(kāi)始新的DMA傳輸,需要在關(guān)閉DMA通道的情況下,在DMA_CNDTRx寄存器中重新寫(xiě)入傳輸數(shù)目。

在循環(huán)模式下,最后一次傳輸結(jié)束時(shí),DMA_CNDTRx寄存器的內(nèi)容會(huì)自動(dòng)地被重新加載為其初始數(shù)值,內(nèi)部的當(dāng)前外設(shè)/存儲(chǔ)器地址寄存器也被重新加載為DMA_CPARx/DMA_CMARx寄存器設(shè)定的初始基地址。

3、通道配置過(guò)程

下面是配置DMA通道x的過(guò)程(x代表通道號(hào)):

在DMA_CPARx寄存器中設(shè)置外設(shè)寄存器的地址。發(fā)生外設(shè)數(shù)據(jù)傳輸請(qǐng)求時(shí),這個(gè)地址將是數(shù)據(jù)傳輸?shù)脑椿蚰繕?biāo)。

在DMA_CMARx寄存器中設(shè)置數(shù)據(jù)存儲(chǔ)器的地址。發(fā)生外設(shè)數(shù)據(jù)傳輸請(qǐng)求時(shí),傳輸?shù)臄?shù)據(jù)將從這個(gè)地址讀出或?qū)懭脒@個(gè)地址。

在DMA_CNDTRx寄存器中設(shè)置要傳輸?shù)臄?shù)據(jù)量。在每個(gè)數(shù)據(jù)傳輸后,這個(gè)數(shù)值遞減。

在DMA_CCRx寄存器的PL[1:0]位中設(shè)置通道的優(yōu)先級(jí)。

在DMA_CCRx寄存器中設(shè)置數(shù)據(jù)傳輸?shù)姆较颉⒀h(huán)模式、外設(shè)和存儲(chǔ)器的增量模式、外設(shè)和存儲(chǔ)器的數(shù)據(jù)寬度、傳輸一半產(chǎn)生中斷或傳輸完成產(chǎn)生中斷。

設(shè)置DMA_CCRx寄存器的ENABLE位,啟動(dòng)該通道。

一旦啟動(dòng)了DMA通道,它既可響應(yīng)連到該通道上的外設(shè)的DMA請(qǐng)求。當(dāng)傳輸一半的數(shù)據(jù)后,半傳輸標(biāo)志(HTIF)被置1,當(dāng)設(shè)置了允許半傳輸中斷位(HTIE)時(shí),將產(chǎn)生一個(gè)中斷請(qǐng)求。在數(shù)據(jù)傳輸結(jié)束后,傳輸完成標(biāo)志(TCIF)被置1,當(dāng)設(shè)置了允許傳輸完成中斷位(TCIE)時(shí),將產(chǎn)生一個(gè)中斷請(qǐng)求。

4、循環(huán)模式

循環(huán)模式用于處理循環(huán)緩沖區(qū)和連續(xù)的數(shù)據(jù)傳輸(如ADC的掃描模式)。在DMA_CCRx寄存器中的CIRC位用于開(kāi)啟這一功能。當(dāng)啟動(dòng)了循環(huán)模式,數(shù)據(jù)傳輸?shù)臄?shù)目變?yōu)?時(shí),將會(huì)自動(dòng)地被恢復(fù)成配置通道時(shí)設(shè)置的初值,DMA操作將會(huì)繼續(xù)進(jìn)行。

5、存儲(chǔ)器到存儲(chǔ)器模式

DMA通道的操作可以在沒(méi)有外設(shè)請(qǐng)求的情況下進(jìn)行,這種操作就是存儲(chǔ)器到存儲(chǔ)器模式。當(dāng)設(shè)置了DMA_CCRx寄存器中的MEM2MEM位之后,在軟件設(shè)置了DMA_CCRx寄存器中的EN位啟動(dòng)DMA通道時(shí),DMA傳輸將馬上開(kāi)始。當(dāng)DMA_CNDTRx寄存器變?yōu)?時(shí),DMA傳輸結(jié)束。存儲(chǔ)器到存儲(chǔ)器模式不能與循環(huán)模式同時(shí)使用。

中斷

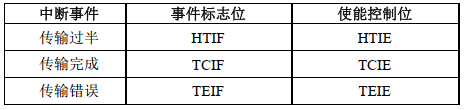

每個(gè)DMA通道都可以在DMA傳輸過(guò)半、傳輸完成和傳輸錯(cuò)誤時(shí)產(chǎn)生中斷。為應(yīng)用的靈活性考慮,通過(guò)設(shè)置寄存器的不同位來(lái)打開(kāi)這些中斷。

表1 DMA中斷請(qǐng)求

DMA請(qǐng)求映射

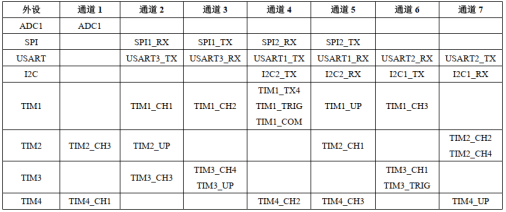

DMA1控制器

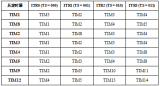

從外設(shè)(TIMx[x=1、2、3、4]、ADC1、SPI1、SPI/I2S2、I2Cx[x=1、2]和USARTx[x=1、2、3])產(chǎn)生的7個(gè)請(qǐng)求,通過(guò)邏輯或輸入到DMA控制器,這意味著同時(shí)只能有一個(gè)請(qǐng)求有效。參見(jiàn)表2各個(gè)通道的DMA1請(qǐng)求一覽。

表1 DMA中斷請(qǐng)求

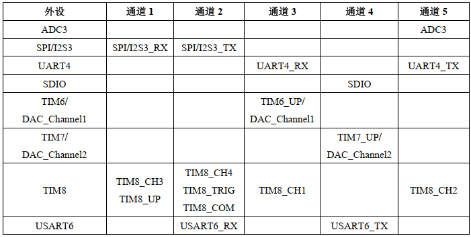

DMA2控制器

從外設(shè)(TIMx[5、6、7、8]、ADC3、SPI/I2S3、UART4、USART6、DAC通道1、2和SDIO)產(chǎn)生的5個(gè)請(qǐng)求,經(jīng)邏輯或輸入到DMA2控制器,這意味著同時(shí)只能有一個(gè)請(qǐng)求有效。參見(jiàn)表3的各個(gè)通道的DMA2請(qǐng)求一覽。外設(shè)的DMA請(qǐng)求,可以通過(guò)設(shè)置相應(yīng)外設(shè)寄存器中的DMA控制位,被獨(dú)立地開(kāi)啟或關(guān)閉。

表3 各個(gè)通道的DMA2請(qǐng)求一覽

-

控制器

+關(guān)注

關(guān)注

114文章

17082瀏覽量

183960 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7645瀏覽量

167150 -

緩沖器

+關(guān)注

關(guān)注

6文章

2048瀏覽量

46955 -

dma

+關(guān)注

關(guān)注

3文章

576瀏覽量

103087

原文標(biāo)題:MCU微課堂|CKS32F107xx DMA

文章出處:【微信號(hào):中科芯MCU,微信公眾號(hào):中科芯MCU】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

使用STM32F101xx和STM32F103xx DMA控制器

CKS32F4xx系列芯片以太網(wǎng)模塊主要功能及框圖解析

CKS32F4xx系列產(chǎn)品串口DMA傳輸

CKS32F4xx系列RNG功能設(shè)置

STM32F0xx的DMA控制器的使用

CKS32F4xx系列FSMC功能簡(jiǎn)介

CKS32F107xx系列時(shí)鐘系統(tǒng)具體配置方法講解

CKS32F107xx系列MCU中ADC介紹

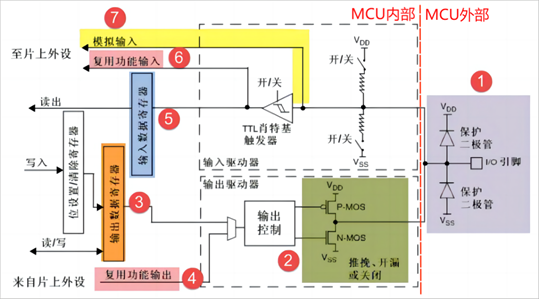

CKS32F107xx系列MCU的GPIO內(nèi)部硬件結(jié)構(gòu)和工作模式

詳解CKS32F107xx系列的定時(shí)器同步功能

CKS32F107xx系列的DMA控制器簡(jiǎn)介

CKS32F107xx系列的DMA控制器簡(jiǎn)介

評(píng)論