電子發燒友網報道(文 / 吳子鵬)芯粒(Chiplet)技術作為半導體領域的一項創新技術,擁有極為廣闊的應用前景。一方面,通過將不同功能的芯粒進行異構集成,能夠在不依賴更先進制程工藝的情況下,實現芯片整體性能的提升,這為突破摩爾定律的限制開辟了新路徑,同時顯著降低復雜 SoC 的設計和制造成本,提高芯片良率;另一方面,芯粒技術與當前 AI 芯片多樣化和快速迭代的發展趨勢高度契合,通過合理搭配不同功能的芯粒,并優化芯粒之間的通信和協同工作機制,采用芯粒架構的 AI 芯片能夠在提高算力的同時,更好地控制功耗,提升能效比,且具備出色的設計靈活性。

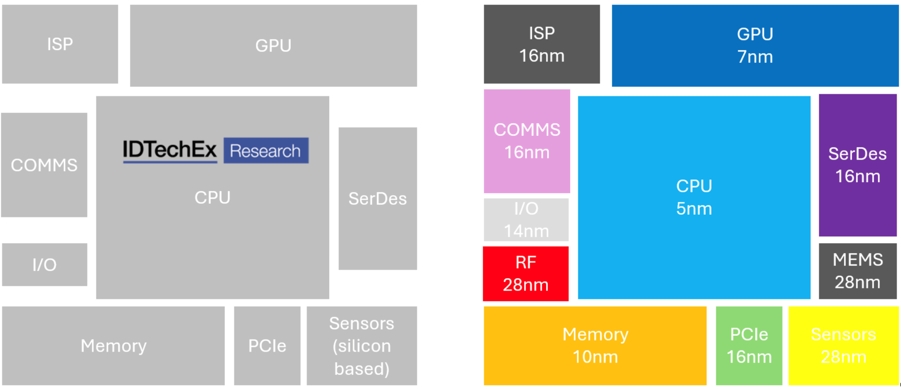

根據 MEMS 麥姆斯咨詢發布的《芯粒(Chiplet)技術及市場 - 2024 版》,在數據中心和人工智能(AI)等領域高性能計算需求的推動下,預計到 2035 年全球芯粒市場規模將達到 4110 億美元。如下圖所示,傳統 SoC 設計和芯粒架構之間存在明顯差異,高速發展的芯粒技術正在顛覆傳統芯片的設計方式。那么,作為從半導體IP大廠轉型成為領先計算平臺公司的 Arm會如何應對這一變革呢?

?

?傳統 SoC 設計和芯粒架構對比,圖源:MEMS 麥姆斯咨詢

芯粒技術:創新與挑戰并存

多年來,摩爾定律主導著芯片技術的發展,持續推動芯片性能不斷提升。但隨著制程工藝逐漸逼近物理極限,繼續按照傳統方式提升芯片性能變得愈發艱難,成本也急劇攀升。這使得不再單純依賴先進制程工藝來實現芯片性能飛躍的芯粒技術,得到了業界的廣泛關注。與傳統大型 SoC 的一體化設計不同,芯粒技術采用模塊化設計理念,各個芯粒可以獨立設計、制造和測試。如果某個芯粒出現問題,只需更換該芯粒,這大大降低了研發和制造成本。在實際設計過程中,不同功能的芯粒還可以根據需求選擇最適合的制程工藝,無需為了滿足所有功能對性能的最高要求,而全部采用最先進(同時也是最昂貴)的制程工藝,這使得芯片設計和制造在成本控制上更加靈活高效。

此外,芯粒技術由于其模塊化的設計方式,也賦予了芯片設計更高的定制化能力。能夠根據具體應用需求,靈活選擇和組合不同功能的芯粒,快速定制出滿足特定需求的芯片。例如,在人工智能領域,對于側重圖像識別的應用,可以將強大的圖形處理芯粒與深度學習專用芯粒相結合;而對于自然語言處理應用,則可以強化計算芯粒與存儲芯粒之間的協同。

不過,芯粒作為一項創新技術,也面臨諸多技術和生態層面的挑戰。首先,盡管芯粒技術前景廣闊,但目前仍面臨接口標準不統一的問題。由于缺乏統一的接口標準,不同供應商生產的芯粒在互操作性上存在較大障礙。在這方面,芯粒技術的模塊化是以標準化為基礎,而現階段因為接口形狀和尺寸各異,很難拼接在一起。

其次是封裝和測試的復雜性提升。隨著芯粒數量的增加和集成度的提高,封裝技術面臨著巨大挑戰。如何在有限的空間內,實現芯粒之間的高速、低延遲通信,是封裝技術需要解決的關鍵問題。另外,由于每個芯粒都有其獨立的功能和性能要求,需要對每個芯粒進行單獨測試,確保其符合設計標準。而且在將多個芯粒集成在一起后,還需要對整個芯片系統進行全面的測試和驗證,這無疑增加了驗證和測試的復雜性。

Arm 如何推動芯粒技術發展

在芯片發展歷程中,Arm 公司的技術創新對行業發展產生了多方面的深遠影響,包括推動架構創新、降低設計門檻、促進異構計算技術發展等。一直以來,Arm 公司都在積極推動芯粒技術的發展。從推出芯粒系統架構 (CSA) 到發布首個公開規范,Arm 為芯粒技術提供了一個基礎的架構框架,建立了統一的行業標準,減少了行業的碎片化現象,進一步推動芯粒技術的標準化。目前,已有超過 60 家行業領先企業參與其中,包括 ADTechnology、Alphawave Semi、AMI、楷登電子、云豹智能、Kalray、Rebellions、西門子和新思科技等。

為了提供加速芯粒應用所需的通用框架,Arm 公司做了大量工作。2024 年 4 月,Arm 攜手合作伙伴共同推動 AMBA CHI 芯片到芯片互連協議等倡議的落地實施。AMBA CHI 協議是 AMBA 總線架構的一部分,主要用于在多芯片系統(如片上系統集成多個芯粒等場景)中實現不同芯片之間的高速數據傳輸和通信。該協議旨在提供一種標準化、高性能、低延遲且具有高可擴展性的芯片間互連解決方案,以滿足現代復雜系統對不同芯片間協同工作的要求。AMBA CHI 協議不僅適用于同一供應商的芯粒,還能確保來自不同供應商的不同芯粒通過一個統一的接口協議來確保芯粒之間的互操作性。作為在 AMBA CHI C2C 領域的重要合作伙伴,NVIDIA 高度認可該標準的重要性。

?

?關鍵 AMBA 規范,圖源:Arm

除了推動芯粒技術的標準化,Arm 公司也在通過持續的研發投入來促進芯粒技術創新。Arm 為芯片設計廠商提供了豐富的設計工具和成熟的計算平臺,幫助他們更高效地進行芯粒的設計和集成。這些工具和解決方案經過了大量的測試和驗證,具有較高的可靠性和性能,能夠大大縮短芯片設計的周期,降低研發門檻。Arm 公司還致力于推動芯粒底層技術的發展,在芯粒技術的底層硬件設計、互聯技術等方面持續投入研發。

Arm 在芯粒領域的成果

持續的研發投入和標準化推動,讓 Arm 公司的芯粒技術生態逐漸強大。Arm 積極與芯片設計公司、芯片制造商、軟件開發商等產業鏈上下游企業開展廣泛合作。與芯片設計公司合作,Arm 提供豐富的設計工具和成熟的計算平臺,以及標準化的芯粒架構和接口,幫助他們實現性能領先的芯粒方案或芯片方案;與芯片制造商合作,將芯粒技術應用于實際的芯片生產中,推動產品的商業化落地;與軟件開發商合作,開發適配芯粒架構的操作系統、編譯器等軟件,完善芯粒技術的生態體系。我們來看兩個具體的案例。其中一個案例是 Arm、三星晶圓代工廠 (Samsung Foundry) 、ADTechnology 和 Rebellions 合作開發基于 Neoverse CSS V3 的 AI CPU 芯粒 (chiplet) 平臺,應用于云、高性能計算 (HPC) 以及人工智能 / 機器學習 (AI/ML) 訓練和推理。在這個案例中,Arm 提供 Neoverse CSS V3 架構,為平臺奠定了先進的計算基礎架構;ADTechnology 提供基于 Neoverse CSS V3 的計算芯粒,為平臺的計算能力提供了核心支持;三星提供 2nm 全環繞柵極(GAA)先進工藝技術來制造芯粒平臺,這種先進工藝能夠提供更高的晶體管密度、更低的功耗和更高的性能;Rebellions 將其 REBEL AI 加速器融入平臺,為平臺提供了專門的 AI 加速能力。

另一個案例是 Arm 和新思科技圍繞 AMBA 協議展開的合作,以確保雙方的共同客戶能夠從使用 AMBA CHI C2C 協議中獲益,同時確保小芯片和 Multi-Die 設計符合協議標準。新思科技針對基于 CHI 主機的 SMP 拓撲結構和 CHI 主機到 CXL 高速緩存 / 內存器件的拓撲結構開發了多款 AMBA 驗證 IP 及多芯片驗證解決方案,幫助多位 HPC 和數據中心客戶順利完成了流片。

這樣的案例不勝枚舉,隨著芯粒技術的潛能逐步釋放,相信 Arm 公司在這個領域的布局藍圖也會越來越大。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ARM

+關注

關注

134文章

9346瀏覽量

376858 -

chiplet

+關注

關注

6文章

457瀏覽量

12966

發布評論請先 登錄

相關推薦

熱點推薦

全球芯片大廠加碼“中國制造”

電子發燒友網報道(文/黃山明)近日,據外媒報道,包括英飛凌、恩智浦、意法半導體等多家全球性芯片大廠都公開表示,期望能夠與中國買家建立更密切的聯系,因此不少企業開始將生產環節放到中國本土,來更好地服務

2.5D集成電路的Chiplet布局設計

隨著摩爾定律接近物理極限,半導體產業正在向2.5D和3D集成電路等新型技術方向發展。在2.5D集成技術中,多個Chiplet通過微凸點、硅通孔和重布線層放置在中介層上。這種架構在異構集成方面具有優勢,但同時在Chiplet布局優

Arm平臺引領AI云計算革新

我們正處于一個由人工智能 (AI) 定義的計算時代,其轉型速度空前迅速。Arm 一直致力于通過工程創新和技術發展,以可持續且可擴展的方式加速

依托Chiplet&高性能RDMA,奇異摩爾斬獲全國顛覆性技術創新大賽(未來制造領域賽)優勝獎

? ? 近日,第十三屆中國創新創業大賽顛覆性技術創新大賽(未來制造領域賽)獲獎結果出爐,奇異摩爾參賽項目【基于Chiplet+RDMA技術的下一

一文詳解Arm架構Armv9.6-A中的最新功能

計算的需求,包括 AI 的興起、機器學習 (ML) 和芯粒 (chiplet) 技術的使用,以及應對高級安全威脅。持續創新確保了 Arm 架構的普及性、普適性能、出色能效、安全性和開發

Primemas選擇Achronix eFPGA技術用于Chiplet平臺

高性能 FPGA 和嵌入式FPGA (eFPGA) IP 的領導者 Achronix Semiconductor Corporation 和使用Chiplet 技術開發創新 SoC Hub

創新型Chiplet異構集成模式,為不同場景提供低成本、高靈活解決方案

電子發燒友網報道(文/李彎彎)近日,北極雄芯官方宣布,歷經近2年的設計開發,自主研發的啟明935系列芯粒已經成功交付流片,而且一次性投出兩顆,一顆是通用型HUB Chiplet“啟明9

剖析 Chiplet 時代的布局規劃演進

來源:芝能芯芯 半導體行業的不斷進步和技術的發展,3D-IC(三維集成電路)和異構芯片設計已成為提高性能的關鍵途徑。然而,這種技術進步伴隨著一系列新的挑戰,尤其是在熱管理和布局規劃方面。 我們探討

Chiplet 顛覆芯片創新,一文看懂計算平臺大廠 Arm 的布局藍圖

Chiplet 顛覆芯片創新,一文看懂計算平臺大廠 Arm 的布局藍圖

評論