電子發燒友網報道(文/梁浩斌)去年年底,多家大廠爆出開發數據中心ASIC芯片的消息,包括傳聞蘋果與博通合作開發面向AI推理的ASIC,亞馬遜也在年底公布了其AIASIC的應用實例,展示出ASIC的應用性價比遠超GPU,加上博通財報AI業務同比大增220%,掀起了AI推理端的ASIC熱潮。

那么ASIC跟傳統的GPU有哪些區別,開發上又有哪些流程上的不同?

ASIC和GPU

通用GPU在設計之初就為了適配更多使用場景,在AI應用上,GPU支持訓練、推理、通用計算等全流程,以英偉達GPU為例,通過CUDA生態,英偉達GPU能夠快速適配新的算法,比如從Transformer到CNN的遷移,只需要修改30%左右的代碼。

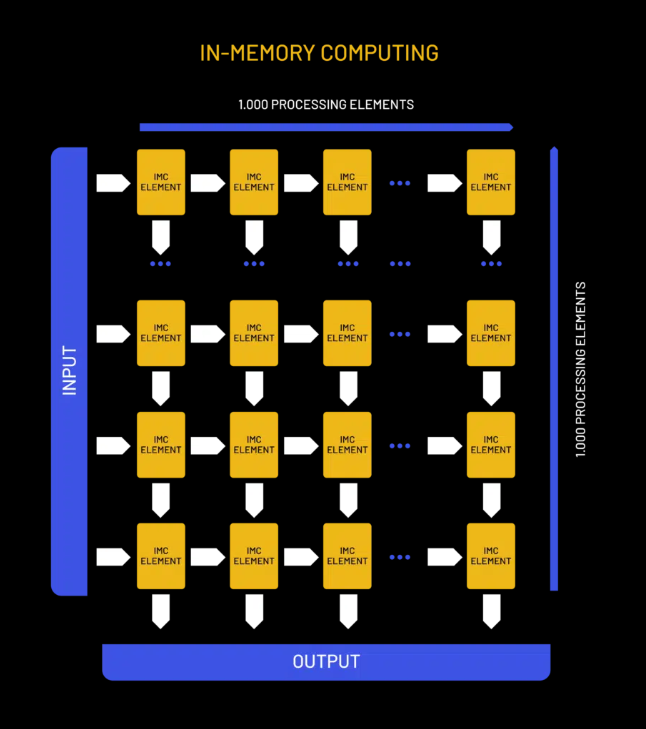

相比通用GPU,ASIC是專為滿足特定應用而設計的芯片,針對特定應用的特定算法進行硬件級別的優化,尤其在AI應用中,比如運行矩陣乘法、張量計算等任務,能夠相比GPU效率更高。

比如谷歌TPU就是一款ASIC,采用脈動陣列設計,通過固化數據流水線減少內存訪問次數,能效比達GPU的3.2倍。

相比之下GPU使用通用計算單元處理多種任務,為了滿足不同類型的計算需求,必然需要存在計算冗余。

GPU由于架構的特性,一般會在AI計算中保留圖形渲染、視頻編解碼等功能模塊,但在AI計算中這些模塊大部分處于閑置狀態。有研究指出,英偉達H100GPU上有大約15%的晶體管是未在AI計算過程中被使用的。

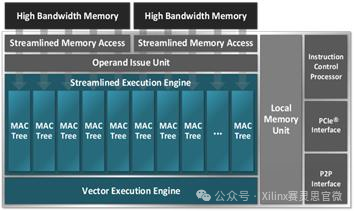

同時,在計算流程上,GPU在處理AI計算任務時是需要通過CUDA軟件棧進行任務調度,比如矩陣乘法的運行時需要經過內存加載、指令分發、TensorCore計算、結果回寫等多個步驟。

而在ASIC上,可以通過硬件級的流水線固化數據流,能夠減少計算流程步驟,提高運算效率。在減少計算流程的同時,ASIC對內存訪問模式的優化,還能有助于降低內存控制器的功耗。

AI計算中,低精度是以損失部分準確率為代價,通過量化壓縮數據來提高推理速度。目前AI推理中INT8/FP16的精度,GPU一般支持FP32/FP64等高精度計算,在混合精度訓練中,GPU還需要額外的顯存來轉換成低精度結果,同樣的芯片,在運行高精度和低精度的算力也不同。

盡管精度的選擇本質上是準確性和效率的取舍,但AI推理等應用中,對精度的需求并不需要極致的接近100%,但仍能保持較高的水準。ASIC一般直接支持低精度計算,在AI計算時的效率能夠相比GPU大幅提高,但保持一定的準確率。比如有數據顯示,TikTok的推薦算法系統采用INT8精度,但依然保持了接近99%的推薦準確率。

所以,ASIC相比GPU,在硬件架構上可以針對專有應用進行特定優化,提高計算效率和降低功耗。在成本方面,ASIC在規模量產的情況下可以降至GPU的三分之一,但前期開發成本仍不能忽視。

可能大家也發現,目前定制開發高算力ASIC的廠商,無一例外是云計算大廠,本身公司業務就有極大規模的算力需求。ASIC定制費用,主要是開發過程中的一次性工程費用,也被業內稱為NRE(Non-RecurringEngineering)。顧名思義,NRE費用只需要支出一次,后續規模生產中不需要再增加這部分費用。

NRE費用中,包含芯片設計的成本,比如研發人員薪酬、EDA工具授權費等,這與芯片使用的制程工藝、芯片本身的復雜程度相關;然后是版圖設計成本,其實這里的概念跟芯片設計的成本類似,主要是涉及芯片的物理布局設計,需要特定的研發人員和軟件支持;再是IP授權費用,一般是一些通用的IP,比如CPUIP、內存控制器、接口IP等。

以定制一款采用5nm制程的ASIC為例,NRE費用可以高達1億至2億美元。然而一旦能夠大規模出貨,NRE費用就可以很大程度上被攤薄。

此前有業內人士分析,中等復雜程度的ASIC盈虧平衡點在10萬片左右,這對于很多廠商來說已經是遙不可及。

ASIC開發流程

在開發ASIC時,最關鍵的是以算法架構為主導,圍繞這一方面去進行其他工作。

首先是進行需求定義,要明確ASIC的目標場景是什么,比如推理還是訓練?端側還是云端?用到CNN還是Transformer?在AI領域,定制ASIC的往往是云計算大廠,這些廠商一般會有頂尖的架構師去進行充分考慮,未來可能的應用、效率、成本、技術可行性等都會包含在內,同時平衡性能、成本、功耗等關鍵指標。當然也有一些芯片廠商推出針對某些應用場景的ASIC產品。那么在前期產品定義就十分關鍵,有時候還需要開發針對應用場景的算法配合自己的芯片產品使用。

接下來是最關鍵的算法和架構優化,需要對行業發展趨勢有足夠認知,選擇適合的算法進行優化,保證算法與硬件架構適配,通過仿真測試驗證。

然后設計ASIC的整體架構,比如功能模塊的劃分和模塊之間的互連,以及接口等IP的使用。

在前端設計中,使用VHDL或Verilog等硬件描述語言對設計進行編碼,然后將編碼轉換為門級網表,對其進行優化滿足芯片面積和性能要求。

進入后端設計后,需要將門級網表映射到具體的芯片物理結構上,進行布局和布線。

完成模塊布局和布線后,就可以開始進行FPGA驗證,測試ASIC設計的功能是否滿足需求。隨后完成流片、測試后就可以投入大規模生產。

總的來說,ASIC的開發中,硬件和軟件的協同是其成功的關鍵,在擁有強大的芯片性能同時,還要筑建完整的軟件生態,吸引更多用戶使用。

當然,在ASIC量產進入市場后,軟件棧開發也是相當重要的,需要編譯器將TensorFlow和PyTorch等機器學習模型映射到硬件指令上,在生態上也需要支持更多主流的框架,以盡可能滿足更多使用需求。

-

asic

+關注

關注

34文章

1243瀏覽量

122051 -

AI

+關注

關注

88文章

34405瀏覽量

275678 -

芯片開發

+關注

關注

0文章

12瀏覽量

2574

發布評論請先 登錄

AI端側部署開發(SC171開發套件V3)

首創開源架構,天璣AI開發套件讓端側AI模型接入得心應手

NVIDIA 推出開放推理 AI 模型系列,助力開發者和企業構建代理式 AI 平臺

AI推理帶火的ASIC,開發成敗在此一舉!

AI推理帶火的ASIC,開發成敗在此一舉!

評論