概述

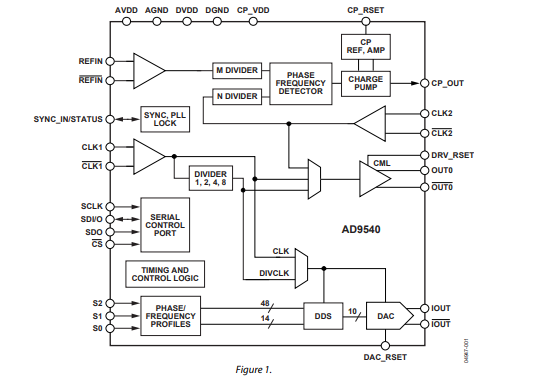

AD9540支持多種功能,包括信號合成和低抖動時鐘發生,適合各種應用。該器件內置高性能PLL電路,包括靈活的200 MHz鑒頻鑒相器和數字控制電荷泵電流。它還可以使低抖動、655 MHz CML模式(PECL兼容)輸出驅動器具有可編程壓擺率。器件支持最高2.7 GHz的外部VCO速率。片上400 MSPS DDS提供及精密的調諧分辨率和相位編程能力。信息通過一個串行I/O端口載入AD9540中,該端口的器件寫入速度為25Mb/s。還可以對AD9540分頻器模塊進行編程,支持擴頻時鐘模式。

AD9540的額定工作溫度范圍為-40℃至+85℃擴展汽車應用溫度范圍。

數據表:*附件:AD9540低抖動、基于DDS的時鐘發生器和頻率合成器技術手冊.pdf

應用

特性

- 出色的內在抖動性能

- 200 MHz鑒頻鑒相器輸入

- 655 MHz可編程輸入分頻器用于鑒頻鑒相器(÷M,N) {M,N =1..16}(可旁路)

- 可編程RF分頻器(÷R) {R = 1、2、4、8}(可旁路)

- 8個可編程相位/頻率配置文件

- 400 MSPS內部DDS時鐘速度

- 48位頻率調諧字分辨率

- 14位可編程相位偏移

- 器件采用1.8 V電源供電

- I/O、CML驅動器和電荷泵輸出采用3.3 V電源供電

- 軟件控制關斷功能

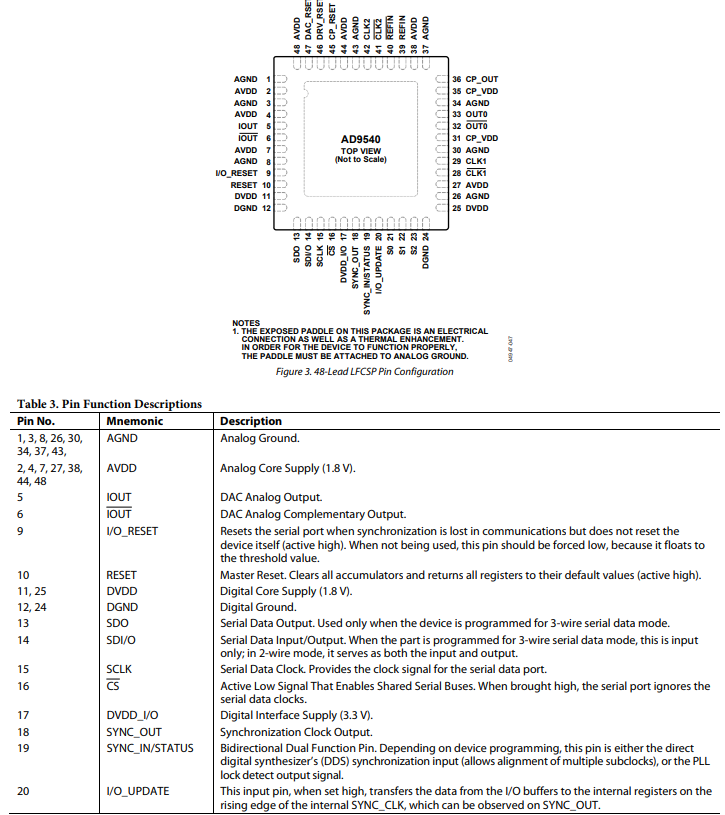

- 48引腳LFCSP封裝

- 可編程電荷泵電流(最高達4 mA)

- 檢測到雙模式PLL鎖定

- 符合PECL標準的655 MHz CML模式輸出驅動器

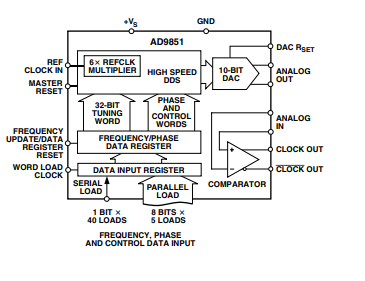

框圖

引腳配置描述

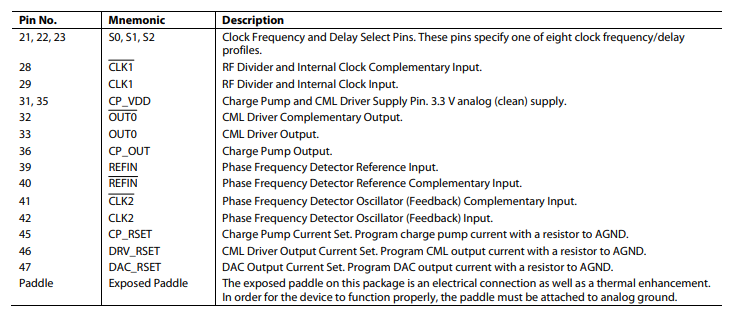

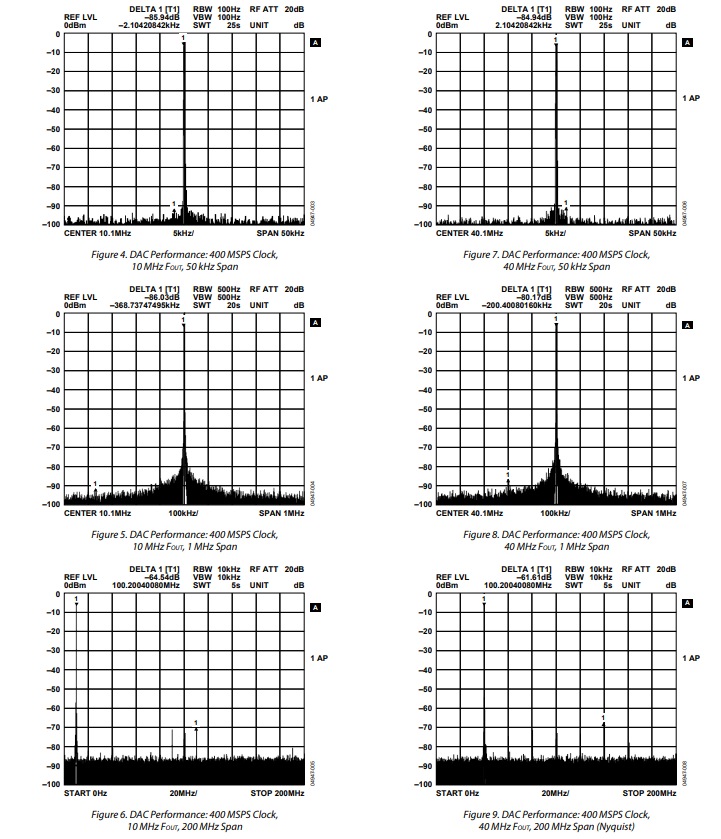

典型性能特征

應用電路說明

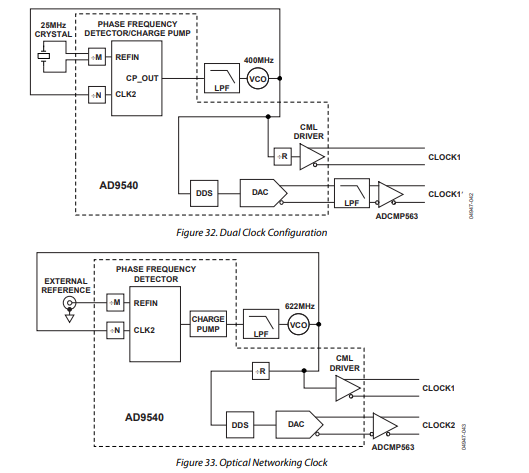

雙時鐘配置

在此電路中,M = 1,N = 16,R = 4。直接數字合成器(DDS)的調諧字也為1/4,這樣CLOCK1'的頻率就等于CLOCK1的頻率。DDS中的相位調整功能為CLOCK1'相對于CLOCK1提供14位可編程上升沿延遲能力(見圖32)。

光網絡時鐘

這是將AD9540配置為光網絡時鐘的情況。該環路可用于為OC12生成622 MHz時鐘。DDS可編程輸出8 kHz信號,作為子系統中其他電路的基準(見圖33)。

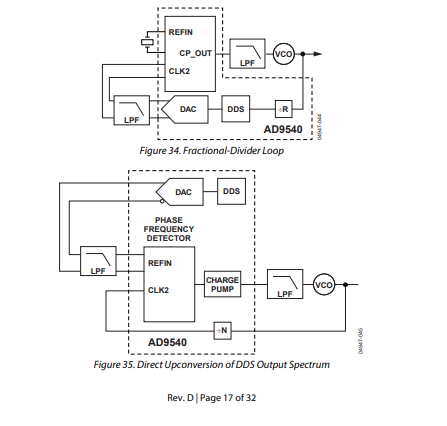

分數分頻器環路

該環路在反饋路徑中提供DDS的精確(48位)分數頻率除法功能以及DDS的頻率掃描功能。對DDS進行編程,可實現從24 MHz到25 MHz的掃描,壓控振蕩器(VCO)的輸出從2.7 GHz掃描到2.6 GHz。此情況下的參考源是一個簡單的晶體(見圖34)。

直接上變頻

AD9540被配置為使用DDS作為鎖相環(PLL)的精確參考源。由于VCO頻率小于655 MHz,它可以直接輸入到鑒頻鑒相器的反饋端。

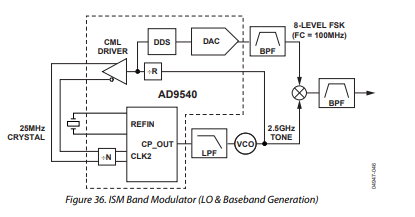

本振和基帶調制生成

利用AD9540的PLL部分生成本振(LO),DDS部分生成調制后的基帶,此電路使用外部混頻器在射頻工業、科學和醫學(ISM)頻段實現一些簡單的調制(見圖36)。

-

頻率合成器

+關注

關注

5文章

295瀏覽量

32740 -

pll

+關注

關注

6文章

887瀏覽量

136145 -

時鐘發生器

+關注

關注

1文章

223瀏覽量

68959 -

AD9540

+關注

關注

0文章

3瀏覽量

8414

發布評論請先 登錄

AD9914BCPZ直接數字頻率合成器

基于DDS的頻率合成器設計介紹

什么是頻率合成器

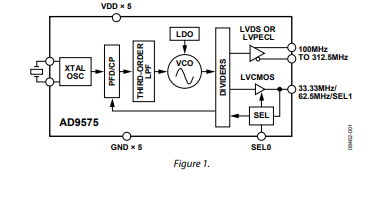

時鐘發生器AD9577資料分享

DDS頻率合成器和信號發生器是同一個概念吧?

AD9850 DDS 頻率合成器的原理及應用

AD9540 低抖動、基于DDS的時鐘發生器和頻率合成器

AD9540低抖動、基于DDS的時鐘發生器和頻率合成器技術手冊

AD9540低抖動、基于DDS的時鐘發生器和頻率合成器技術手冊

評論