概述

ADMV8052是一款射頻濾波器,具有數字可選的工作頻率。該器件集成了三個帶通濾波器,跨越從30到520 MHz的三個指定頻段。

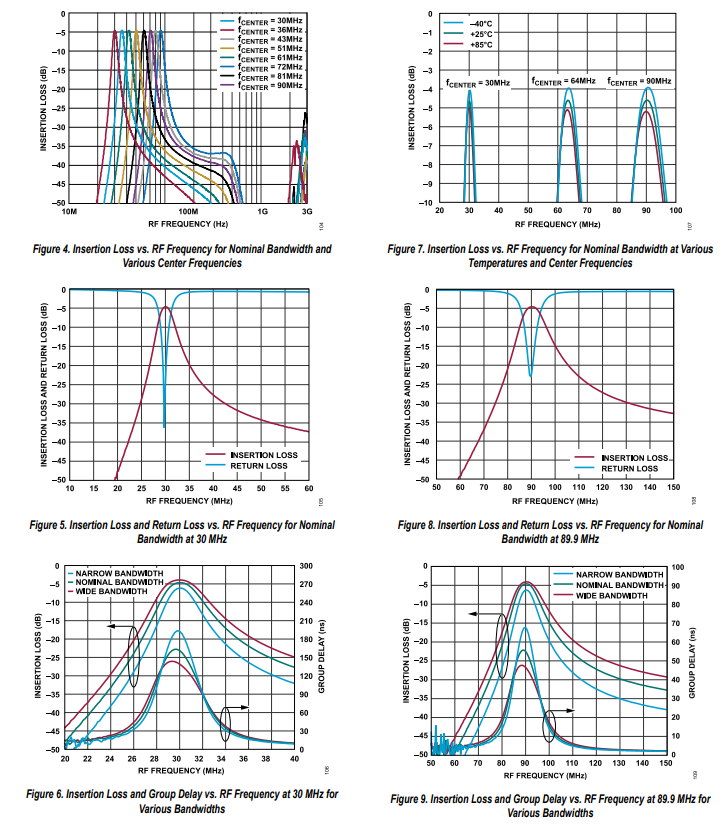

可使用融入了正在申請專利的插值法的8位值(256種狀態(tài))調整中心工作頻率(f C )。典型3 dB帶寬(BW)為9%,可調性為± 2%。插入損耗通常為4 dB,2 x BW時的抑制為20 dB,非常適合用于較大限度地降低系統(tǒng)諧波。此外,靈活的架構采用旁路模式,具有1 dB的低插入損耗。

這款可調諧濾波器可用作大型開關濾波器組和腔體調諧濾波器的小型替代方案,可以在先進的通信應用中提供動態(tài)可調的解決方案。

數據表:*附件:ADMV8052 30MHz至520MHz數字可調帶通濾波器技術手冊.pdf

應用

- 陸地移動無線電

- 測試與測量設備

- 軍用雷達和電子戰(zhàn)/電子對抗

- 衛(wèi)星通信

- 工業(yè)和醫(yī)療設備

特性

- 數字可調諧、多倍頻程、帶通調諧

- 3dB帶寬(BW):7至11%

- 低插入損耗:4dB (9% BW)

- 出色的抑制:20 dB (2 x BW)

- 出色的線性度

- 以單芯片替代分立式解決方案

- 緊湊型22 × 22 x 5.73 mm LGA封裝

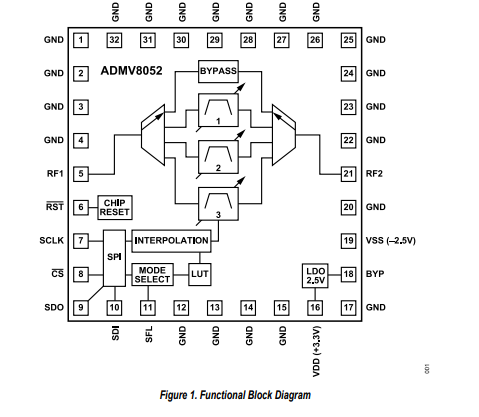

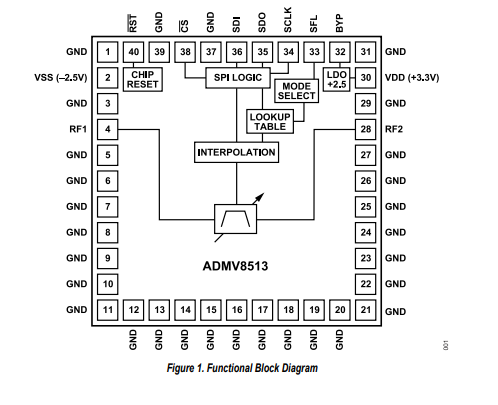

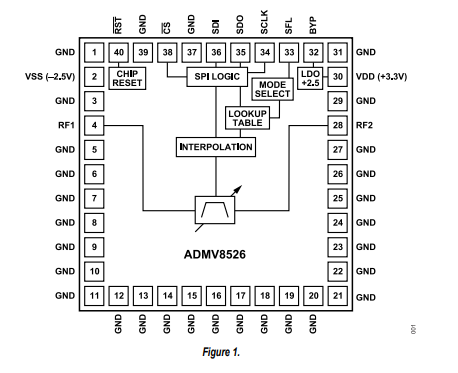

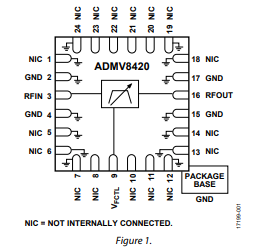

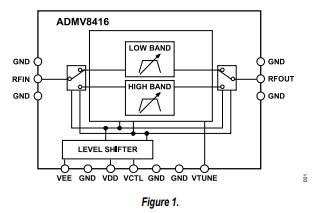

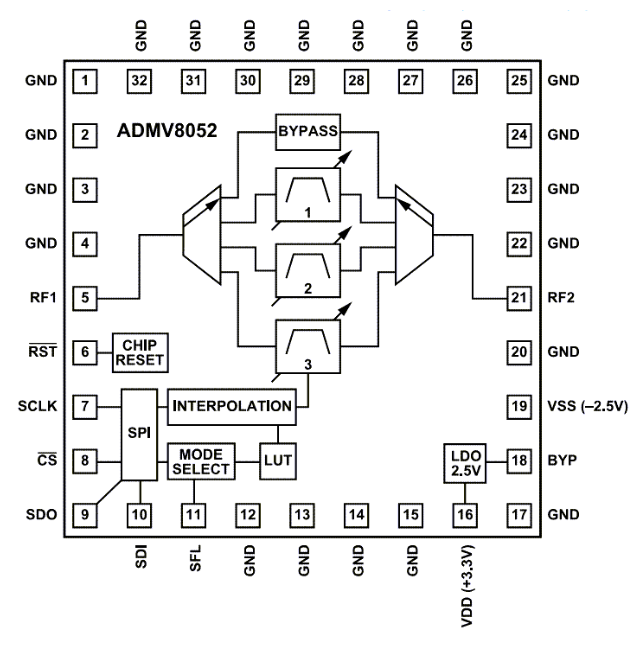

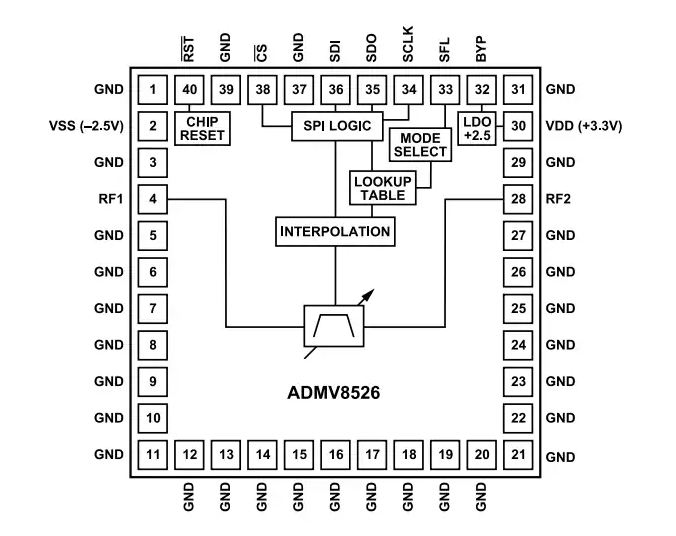

框圖

時序圖

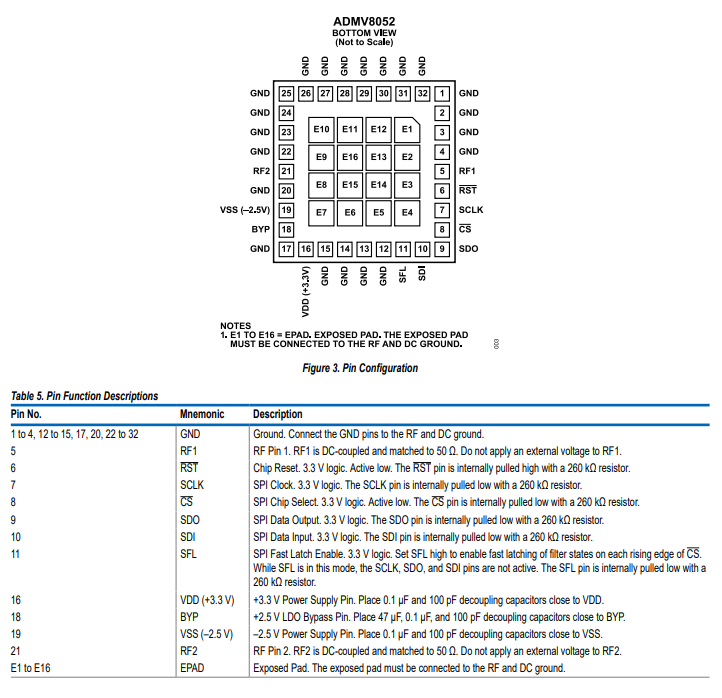

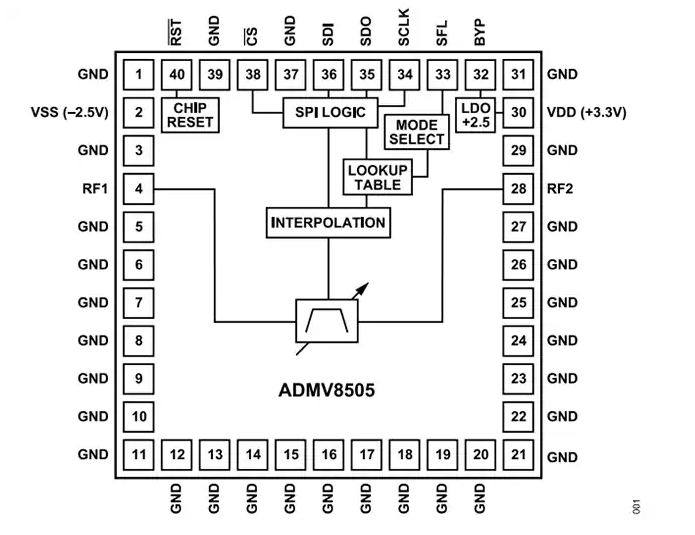

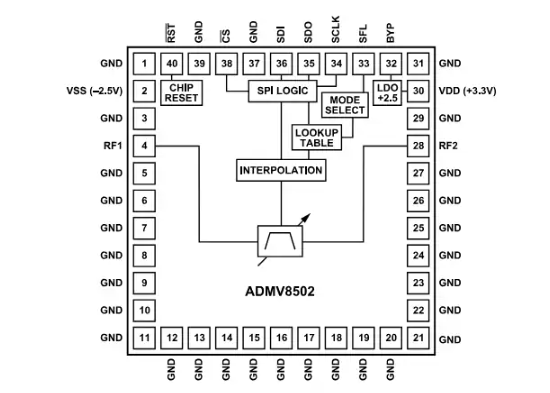

引腳配置描述

典型性能特征

芯片架構

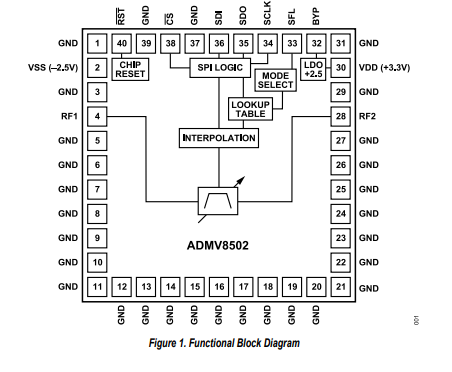

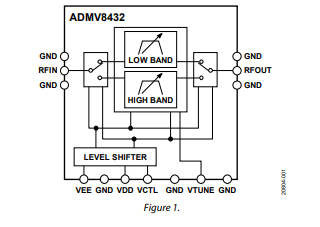

ADMV8052包含三個帶通濾波器(BPF)以及一個可選的旁路配置,可通過兩個四選一(SP4T)開關進行選擇。該器件可在30 MHz至620 MHz的頻率帶寬內實現全覆蓋,且無任何死區(qū)。圖1是ADMV8052的概念框圖。

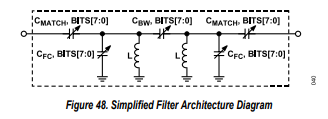

ADMV8052內的每個帶寬包含多個開關電容,這些電容可改變射頻性能。圖48詳細展示了濾波器架構的簡化示意圖。

兩個中心頻率電容((C_{FC}))由(f_{CENTER})負載值配置,該值可調節(jié)濾波器的(f_{CENTER}) 。同樣,帶寬電容((C_{BW}))由帶寬負載值配置,該值可調節(jié)濾波器的帶寬響應。此外,兩個匹配電容((C_{MATCH}))根據濾波器的匹配負載值進行設置,可調節(jié)匹配阻抗。

(f_{CENTER})、帶寬和匹配負載值各有256種狀態(tài)(8位)。理論上,ADMV8052內每個頻段的(f_{CENTER})、帶寬和匹配負載值組合有超過1600萬種可能狀態(tài)。為簡化這些值的選擇,亞德諾半導體開發(fā)了三種正在申請專利的插值功能,以方便實施。

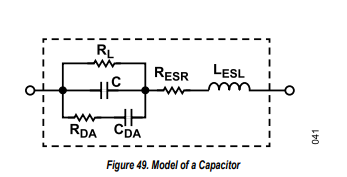

射頻連接

ADMV8052的RF1和RF2引腳與片內射頻開關直流耦合。如果系統(tǒng)中存在直流電壓,則RF1和RF2引腳需與其他組件進行交流耦合,建議在這些引腳串聯(lián)隔直電容。隔直電容的選擇必須基于濾波器的頻率。通常,值大于10 nF的電容足以在較低工作頻率下將插入損耗降至最低。在較高工作頻率下,可能需要考慮所選電容的寄生元件。圖49展示了電容的一般模型。電容的寄生串聯(lián)電感((L_{ESL}))通常在給定的其他寄生元件中占主導地位,其阻抗可能會很顯著。其他寄生元件,包括泄漏電阻((R_{L}))、介電吸收電阻((R_{DA}))、介電吸收電容((C_{DA}))和電氣串聯(lián)電阻((R_{ESR}))對整體性能的影響較小。

電容模型

圖49展示了電容的模型。

SPI配置

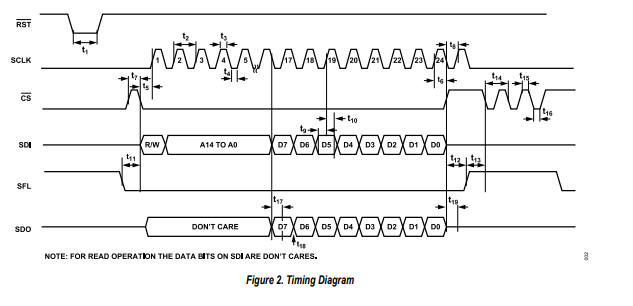

ADMV8052的SPI接口允許通過5引腳SPI端口對器件進行特定功能或操作的配置。該接口為用戶提供了更高的靈活性和定制性。ADMV8052的SPI接口由五條控制線組成:SFL、SCLK、SDI、SDO和(overline{CS}) 。對于正常的SPI操作,需將SFL引腳保持為低電平。

SPI協(xié)議由一個地址字節(jié)和15個寄存器地址位及8個數據位組成。地址字段和數據字段均為大端序(MSB在前,LSB在后)。

將MSB設置為0進行寫操作,設置為1進行讀操作。寫周期中,SDI上的數據必須在SCLK的上升沿采樣。24位的串行寫地址和數據在SDI控制線上從MSB到LSB逐位移入。ADMV8052的輸入邏輯電平支持3.3V接口。

對于讀周期,(overline{R/W})位和15個寄存器地址位移入,在SCLK的上升沿對SDI進行采樣。然后,8位串行數據在SDO邏輯電平上移出,第一個字節(jié)在SCLK的下降沿移出。輸出驅動邏輯電平為3.3V。在指令周期的最后一個SCLK上升沿之后,SDO的輸出驅動器啟用,并在讀取周期內保持激活狀態(tài)。在讀操作中,當(overline{CS})無效時,SDO返回高阻態(tài),直到下一次讀取事務。(overline{CS})必須在寫或讀序列的開頭和結尾置為有效。

(overline{CS})上的低電平有效輸入啟動并允許通信周期。(overline{CS})引腳允許多個器件在同一串行通信線上使用。SDO引腳在通信周期內為高阻抗狀態(tài)。在通信周期內,芯片選擇必須保持低電平。SPI通信協(xié)議遵循亞德諾半導體的SPI標準。

-

射頻

+關注

關注

106文章

5745瀏覽量

170067 -

濾波器

+關注

關注

162文章

8120瀏覽量

181581 -

帶通濾波器

+關注

關注

18文章

252瀏覽量

43849

發(fā)布評論請先 登錄

ADMV8052: 30 MHz to 520 MHz Digitally Tunable Band-Pass Filter Preliminary Data Sheet

ADMV8513:520 MHz至1300 MHz、數字金槍魚、帶-包過濾器數據表 ADI

ADMV8502 90MHz至225 MHz、數字可調諧帶通濾波器技術手冊

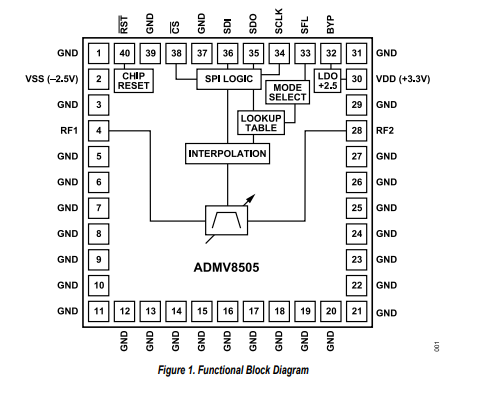

ADMV8505 225MHz至520MHz、數字可調諧帶通濾波器技術手冊

ADMV8513 520MHz至1300MHz、數字可調諧帶通濾波器技術手冊

ADMV8526 1.25 GHz至2.60 GHz數字可調帶通濾波器技術手冊

ADMV8420 10GHz至21.7GHz可調諧帶通濾波器技術手冊

ADMV8416 6.3GHz至18GHz、可調帶通濾波器技術手冊

ADMV8432 15.1GHz至32GHz,可調帶通濾波器技術手冊

Analog Devices Inc. ADMV8505數字可調諧帶通濾波器數據手冊

ADMV8052 30MHz至520MHz數字可調帶通濾波器技術手冊

ADMV8052 30MHz至520MHz數字可調帶通濾波器技術手冊

評論