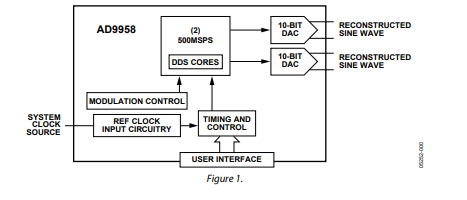

概述

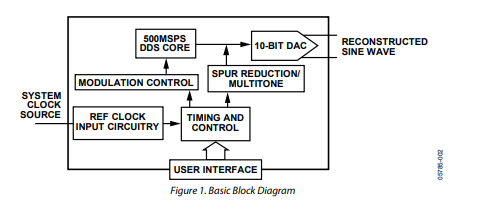

AD9958由兩個直接數字頻率合成器(DDS)內核構成,每個通道均可提供獨立的頻率、相位和幅度控制。這種靈活性可用于校正信號之間由濾波、放大等模擬處理或PCB布局失配而引起的不平衡問題。由于兩個通道共享一個公共系統時鐘,因此它們具有固有的同步性,支持多個設備的同步。

數據表:*附件:AD9958內置雙通道10 bit DAC的500 MSPS直接數字頻率合成器技術手冊.pdf

AD9958可以執行高達16階的頻率、相位或幅度調制(FSK、PSK、ASK)。通過將數據施加到模式引腳,可執行調制。此外,AD9958還支持線性頻率、幅度或相位掃描,適合雷達、儀器儀表等應用。

AD9958的串行I/O端口可支持多種配置,提供了極大的靈活性。與ADI公司以往DDS產品中提供的SPI工作模式類似,串行I/O端口提供SPI兼容工作模式,。四個數據引腳(SDIO_0/ SDIO_1/SDIO_2/SDIO_3)對應串行I/O的四種可編程模式,從而提供了靈活性。

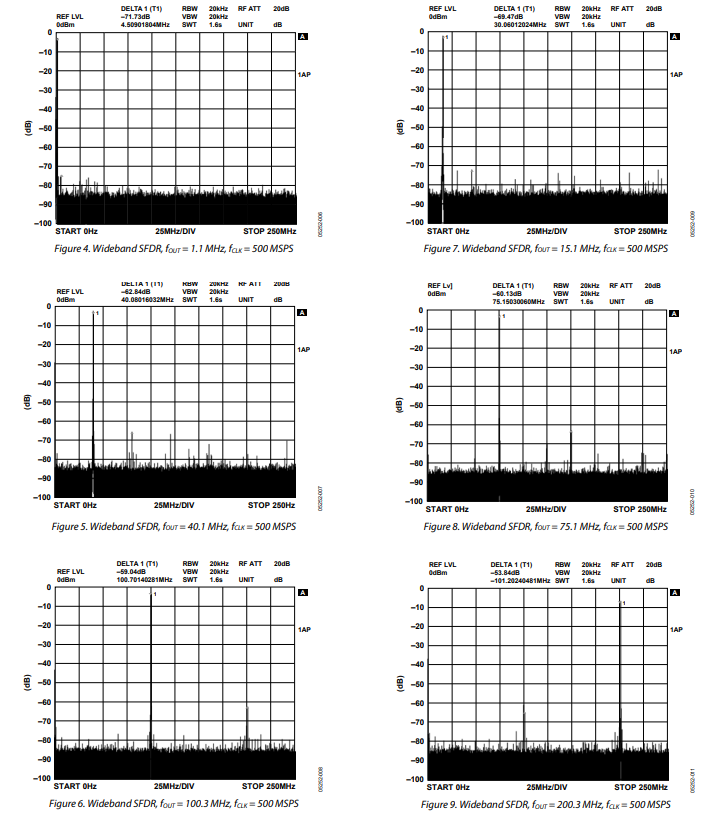

AD9958采用高級DDS技術,可在低功耗下提供高性能。這款器件集成了兩個具有卓越寬帶和窄帶SFDR性能的高速10 bit DAC。每個通道均具有專用的32 bit頻率調諧字、14 bit相位偏移和10 bit輸出比例乘法器。

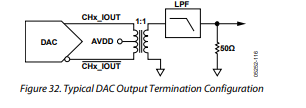

DAC輸出以電源電壓為參考源,必須經由電阻或AVDD中心抽頭變壓器連接到AVDD。每個DAC均具有各自的可編程基準源,用于實現每個通道不同的滿量程電流。

當使用REFCLK作為輸入,并由DAC提供輸出時,這款DDS可用作高分辨率分頻器。兩個通道共用REFCLK輸入源,REFCLK輸入源可被直接驅動,或與高達最大值500 MSPS的內置REFCLK乘法器(PLL)配合使用。PLL倍增因數的可編程范圍為4~20,步進為整數。REFCLK輸入還具有振蕩電路,可將外部晶振用作REFCLK源,晶振的頻率必須在20 MHz與30 MHz之間,晶振可與REFCLK乘法器配合使用。

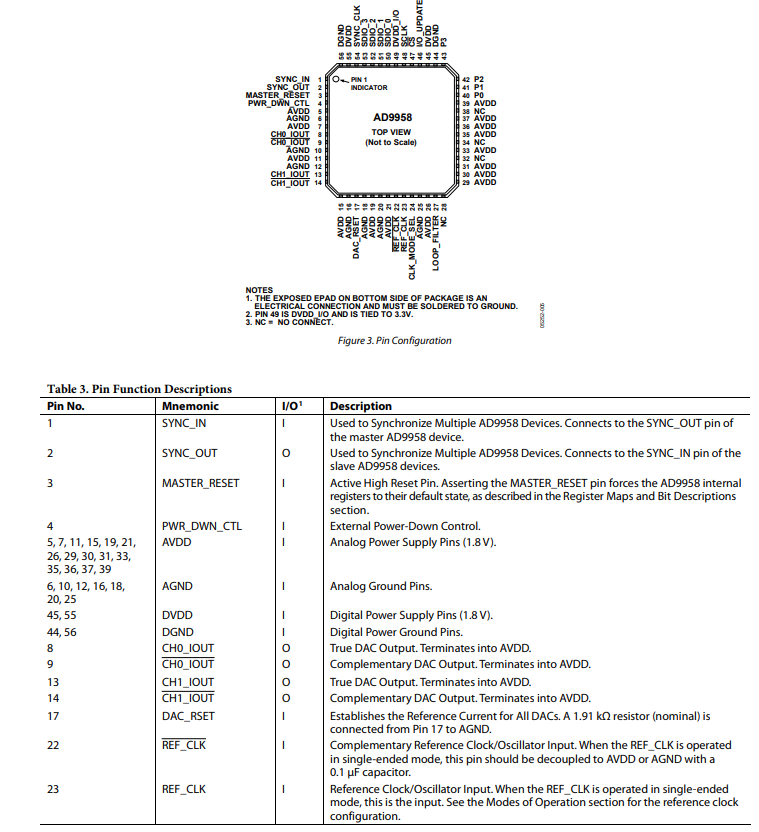

AD9958采用節省空間的56引腳LFCSP封裝。DDS內核(AVDD和DVDD引腳)采用1.8 V電源供電。數字I/O接口(SPI)在3.3 V電壓下工作,并需要將DVDD_I/O引腳(引腳49)連接至3.3 V電壓。

AD9958可在-40°C~+85°C的工業溫度范圍內工作。

應用

特性

- 2個同步DDS通道(500 MSPS)

- 通道間獨立的頻率/相位/幅度控制

- 頻率/相位/幅度變化的延遲匹配

- 出色的通道間隔離性能(>72 dB)

- 線性頻率/相位/幅度掃描功能

- 最多16級頻率/相位/幅度調制(引腳可選0

- 2個集成式10位數模轉換器(DAC)

- 單獨編程DAC滿量程電流

- 頻率調諧分辨率:0.12 Hz或以上

- 14位相位偏移分辨率

- 10位輸出幅度調整分辨率

- 串行I/O端口接口(SPI)具有800 Mbps數據吞吐量

- 軟件/硬件控制省電功能

- 雙電源供電(1.8 V DDS內核/3.3 V串行I/O)

- 多器件同步

- 可選4×至20× REFCLK乘法器(PLL)

- 可選REFCLK晶體振蕩器

- 56引腳LFCSP

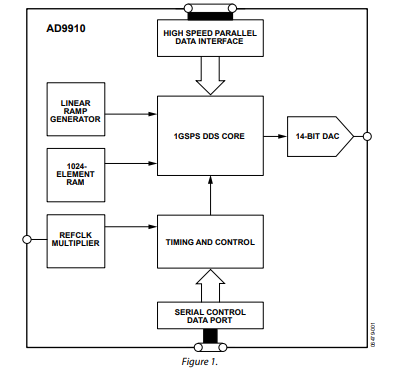

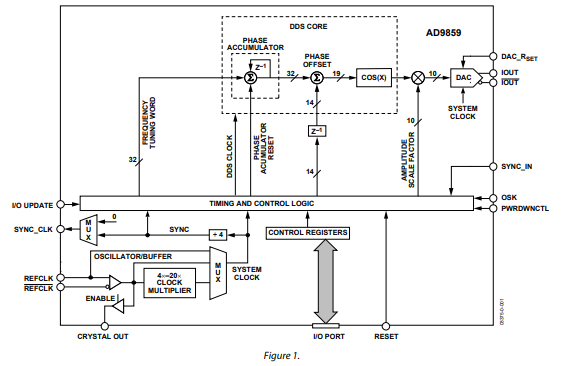

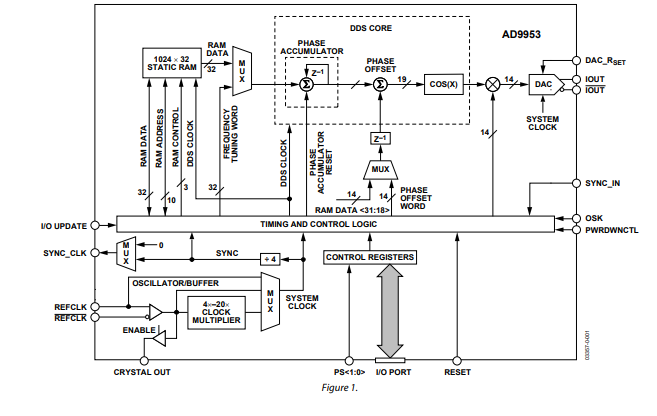

框圖

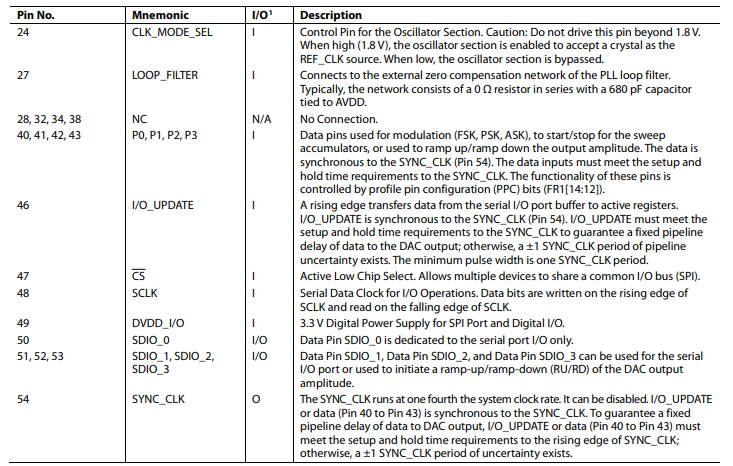

引腳配置描述

典型性能特征

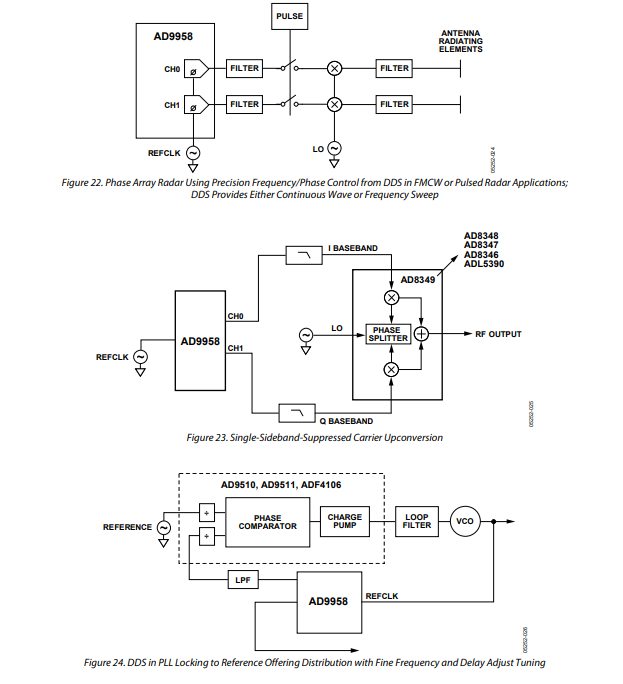

應用電路

直接數字頻率合成器(DDS)內核

AD9958有兩個DDS內核,每個內核由一個32位相位累加器和相位 - 幅度轉換器組成。當相位累加器的相位增量值(頻率調諧字)大于0時,這些數字模塊共同生成數字正弦波。相位 - 幅度轉換器同時將相位信息轉換為幅度信息,通過cos(θ)運算實現。

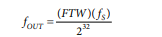

每個DDS通道的輸出頻率(fOUT)是每個累加器回滾速率的函數。確切關系由以下公式給出:

其中:

- ( f_S )是系統時鐘速率。

- FTW是頻率調諧字,且( 0 ≤ FTW ≤ 2^{31} )。

- ( 2^{32} )表示相位累加器容量。

由于兩個通道共用一個系統時鐘,它們本質上是同步的。

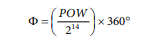

DDS內核架構還支持相位偏移輸出信號的功能,這通過通道相位偏移字(CPOW)實現。CPOW是一個14位寄存器,存儲一個相位偏移值。該值會加到相位累加器的輸出上,以偏移輸出信號的當前相位。每個通道都有自己的通道相位偏移字寄存器。此功能可用于將所有通道置于已知相位關系中。相位偏移的確切值由以下公式給出:

數模轉換器(DAC)

AD9958集成了四個10位電流輸出DAC。DAC將數字碼(幅度)轉換為離散模擬量。DAC電流輸出作為具有高輸出阻抗(通常為100 kΩ )的電流源運行。與許多DAC不同,這些電流輸出無需端接電阻或中心抽頭變壓器即可實現預期的電流流動。

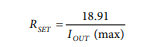

每個DAC具有互補輸出,可提供組合的滿量程輸出電流(( I_{OUT} + I_{overline{OUT}} ))。輸出始終吸收電流,并且它們的總和在任何時間點都等于滿量程電流。滿量程電流通過外部電阻(( R_{SET} ))和可縮放的DAC電流控制位(在工作模式部分討論)進行控制。電阻( R_{SET} )連接在DAC_RSET引腳與模擬地(AGND)之間。滿量程電流與( R_{SET} )的阻值成反比,如下所示:

組合DAC輸出的最大滿量程輸出電流為15 mA,但將輸出限制為10 mA可提供最佳的無雜散動態范圍(SFDR)性能。

DAC輸出電壓擺幅額定值為AVDD + 0.5 V至AVDD - 0.5 V。超出此范圍的電壓可能會導致過度諧波失真。應注意負載端接,使輸出電壓保持在合規范圍內。超出此范圍可能會潛在損壞DAC輸出電路。

-

DDS

+關注

關注

22文章

672瀏覽量

154372 -

AD9958

+關注

關注

0文章

10瀏覽量

14830 -

數字頻率合成器

+關注

關注

0文章

31瀏覽量

6547

發布評論請先 登錄

GM4920:雙通道800MSPS 14位直接數字頻率合成器(DDS)

具有10位DAC的AD9958直接數字頻率合成器的評估板AD9958/PCBZ

采用AD9914 3.5 GSPS直接數字頻率合成器的AD9914/PCBZ評估板

AD9914BCPZ直接數字頻率合成器

高性能雙通道DDS芯片AD9958及其應用_陳昶

AD9958 內置雙通道10 bit DAC的 500 MSPS直接數字頻率合成器

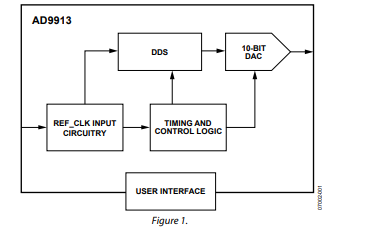

AD9913低功耗、250 MSPS、10位DAC、1.8V CMOS直接數字頻率合成器技術手冊

AD9911 500 MSPS直接數字頻率合成器,內置10位DAC技術手冊

AD9958內置雙通道10 bit DAC的500 MSPS直接數字頻率合成器技術手冊

AD9958內置雙通道10 bit DAC的500 MSPS直接數字頻率合成器技術手冊

評論