概述

DS28E10在單一芯片內把一次性編程224位用戶EPROM與符合FIPS 180-3安全散列算法(SHA-1)的質詢-響應安全認證功能結合在一起。一旦寫入數據,存儲器將自動開啟寫保護。此外,每一個器件帶有唯一的64位ROM注冊碼(ROM ID),由工廠刻入芯片。每次可向存儲器寫入4個字節,安全的低成本工廠編程服務可對器件數據進行預編程,這也包括SHA-1安全數據部分。器件通過單觸點1-Wire?總線進行通信,遵循標準的1-Wire協議,ROM ID在多器件1-Wire網絡中充當節點地址。

數據表:*附件:DS28E10 1-Wire SHA-1認證器技術手冊.pdf

應用

- 授權管理的參考設計

- 傳感器/配件識別和校準

- 系統知識產權保護

特性

- 專用的硬件加速SHA-1引擎產生SHA-1 MAC

- 一頁28字節用戶OTP EPROM

- 不可逆寫保護

- 唯一的工廠編程64位識別碼

- 1-Wire接口支持標準速率和高速驅動

- 以15.4kbps標準速率或高達125kbps的高速模式與主機通信

- 工作在2.8V至3.6V供電范圍和-40°C至+85°C溫度范圍

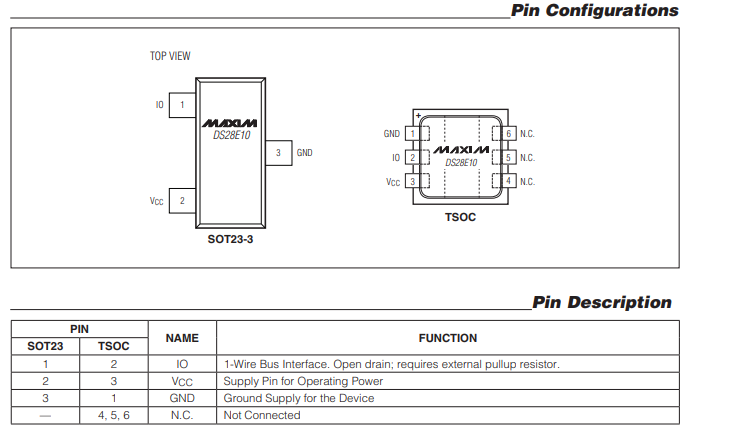

- 3引腳SOT23和6引腳TSOC封裝

- 1-Wire和V

CC引腳具有±6kV (典型值)人體模式(HBM) ESD保護

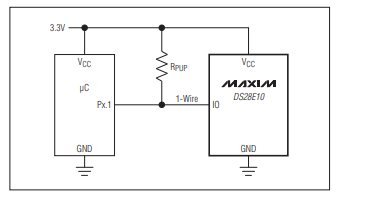

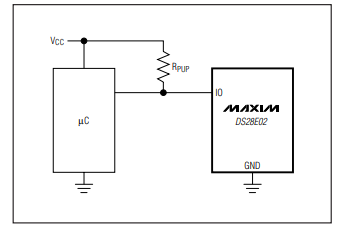

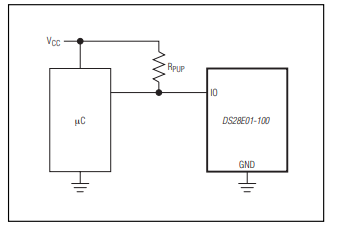

典型操作電路

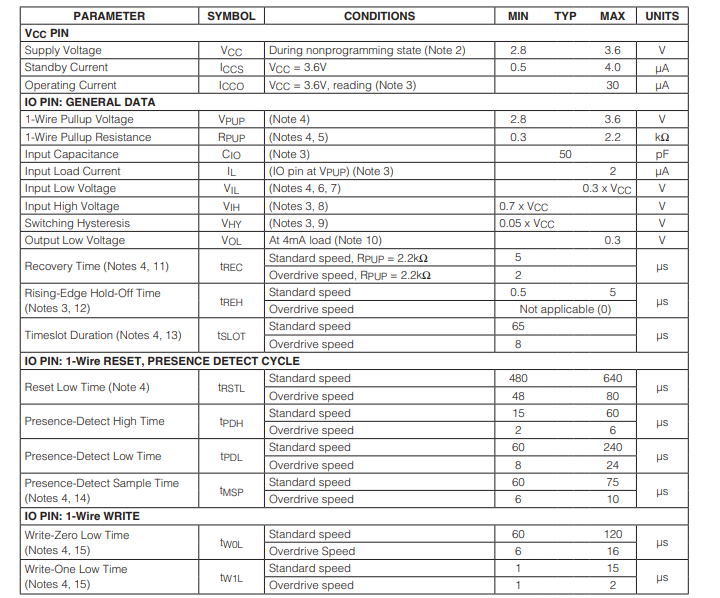

電特性

引腳配置描述

詳細說明

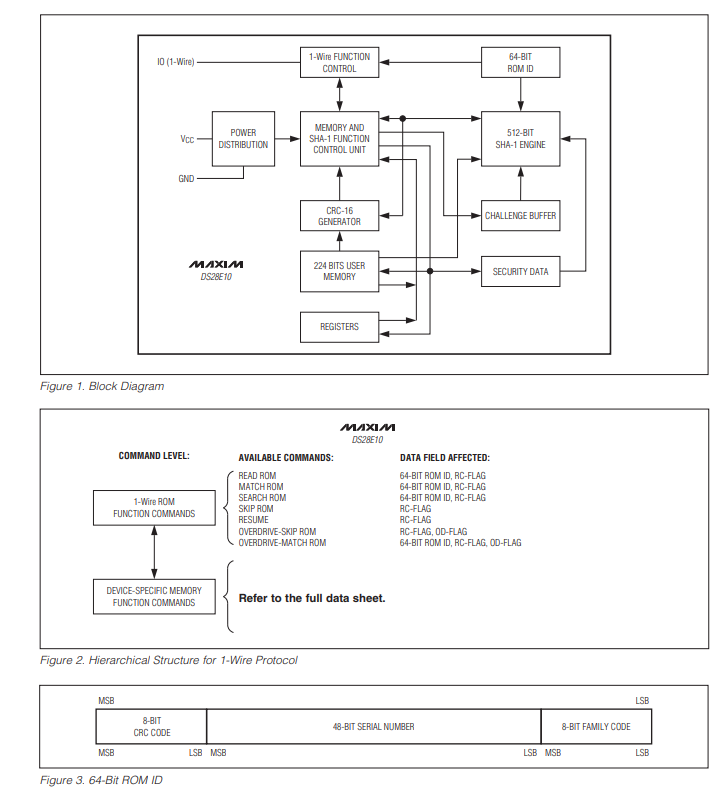

DS28E10將一個512位SHA - 1引擎、安全數據、224位一次性可編程(OTP)電可擦可編程只讀存儲器(EPROM)以及一個64位ROM ID集成在單個芯片中。數據通過一線協議進行串行傳輸,僅需一條數據線和地線即可返回。除了在加密SHA - 1計算中作為唯一數據值的重要作用外,設備的64位ROM ID可用于電子識別使用DS28E10的設備。ROM ID還可作為多設備一線網絡環境中的節點地址,多個設備在同一一線總線上,并可獨立運行。

概述

圖1中的框圖展示了DS28E10主要控制和存儲部分之間的關系。該設備有六個主要數據組件:64位ROM ID、安全數據、主存儲緩沖區、264字節用戶EPROM存儲器、特殊功能寄存器以及一個512位SHA - 1引擎。圖2展示了一線協議的層次結構。總線主設備必須首先提供七個ROM功能命令之一:1)讀ROM,2)匹配ROM,3)搜索ROM,4)跳過ROM,5)恢復(通信),6)超速跳過ROM或7)超速匹配ROM。在完成標準速度下執行的超速跳過ROM或超速匹配ROM命令后,設備將進入超速模式,此時所有后續通信都將以更高速度進行。這些ROM功能命令所需的協議在圖8中說明。在成功執行ROM功能命令后,存儲器和SHA - 1功能將變得可訪問,主設備可以使用六個可用的功能命令中的任何一個。這些功能命令的協議在圖6中說明。所有數據讀寫均先從最低有效位開始。

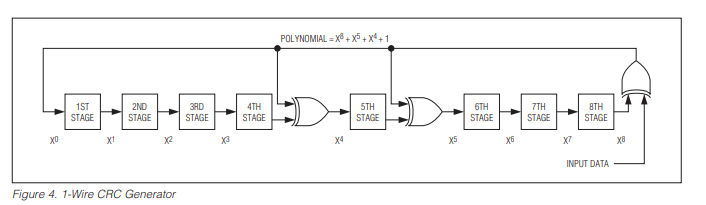

64位ROM ID

每個設備都包含一個唯一的64位ROM ID。前8位是一線家族碼。接下來的48位是唯一的序列號。最后8位是對前56位的循環冗余校驗(CRC)。詳情見圖3。一線CRC使用多項式生成器生成,該生成器由移位寄存器和異或門組成,如圖4所示。多項式為(X^8 + X^5 + X^4 + 1) 。有關一線CRC的更多信息,請參閱美信應用筆記27:《使用循環冗余校驗實現美信1 - 線和iButton產品中的數據驗證》。

移位寄存器位初始化為0。然后,從家族碼的最低有效位開始,逐位移入。在第8位家族碼輸入后,輸入序列號。在輸入序列號的最后一位后,移位寄存器包含CRC值。移位8位后,CRC將移位寄存器重置為全0。

存儲器

該設備有三個存儲區域:用戶存儲器、安全數據和特殊功能寄存器。用戶存儲器和特殊功能寄存器位于線性地址空間中,如圖5所示。用戶存儲器從地址0000h開始,到地址0017h結束。有關詳細信息和附加信息,請參閱完整的數據手冊。

用戶可寫存儲器采用EPROM技術實現。存儲器的出廠默認狀態為00h。在編程過程中,目標4字節塊中的位可以更改為1或0。一旦一個塊被寫入,整個4字節塊將自動被寫保護。這意味著無法多次對一個塊進行編程,例如一次更改幾位。

一線信號

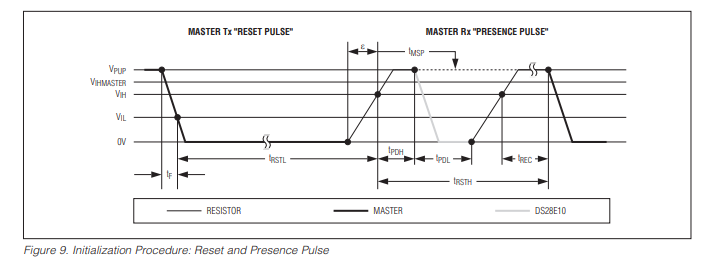

DS28E10需要嚴格的協議來確保數據完整性。該協議包含一線上的四種信號類型:復位脈沖與存在脈沖、寫0、寫1和讀數據。除存在脈沖外,總線主設備可在所有下降沿發起信號。DS28E10可在兩種速度下通信:標準速度和超速。如果未明確切換到超速模式,DS28E10將以標準速度通信。在超速模式下,快速定時適用于所有信號。

從空閑狀態轉為活動狀態時,一線上的電壓需從(V_{PU})降至閾值(V_{IL})以下。從活動狀態轉為空閑狀態時,電壓需從0V升至閾值(V_{IH})以上。達到此上升所需的時間取決于上拉電阻((R_{PUP}))和一線總線電容((C_{TOT})),其時間如圖7所示,持續時間為(tau) 。

圖9展示了與DS28E10開始任何通信所需的初始化序列。一個復位脈沖后接一個存在脈沖,表示DS28E10已準備好接收數據、給定的總線主設備ROM和功能命令。如果總線主設備使用慢速率控制(即下降沿),則必須將(t_{RSTL})下拉至(t_{RSTL} + t_{F}) ,以補償邊緣緩慢的情況。持續480μs或更長時間的(t_{RSTL}) ,可在標準速度下擴展超速模式,或返回設備的默認速度。如果DS28E10處于超速模式且(t_{RSTL}) 小于80μs ,則設備將保持在超速模式。如果設備處于超速模式,且(t_{RSTL}) 在80μs至480μs之間,設備將復位,但通信速度不受影響。

總線主設備釋放線路后,線路進入接收模式。此時,一線總線通過上拉電阻(對于DS2482 - x00驅動器,則通過有源電路)上拉至(V_{PU}) 。當超過閾值(V_{IH})時,DS28E10將(t_{PDH}) 置為1 ,然后傳輸存在脈沖以拉低線路電平。為檢測存在脈沖,總線主設備必須在(t_{MSP}) 測試一線的邏輯狀態。

(t_{RSTH}) 窗口必須至少為(t_{PDHMAX}) 、(t_{IDLEMAX}) 和(t_{RECEMIN}) 之和。在(t_{RSTH}) 過期后,DS28E10準備好進行數據通信。在混合網絡中,標準速度下(t_{RSTH}) 應延長至至少480μs ,超速速度下應延長至48μs ,以適應其他一線設備。

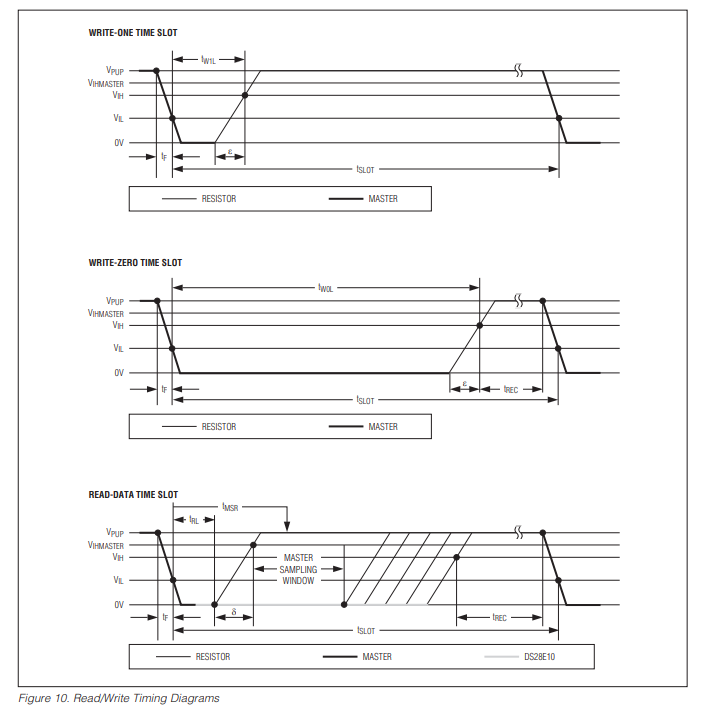

讀/寫字時隙

與DS28E10的數據通信在時隙中進行,每個時隙傳輸一位數據。寫字時隙將數據從總線主設備傳輸到從設備。讀時隙將數據從從設備傳輸到總線主設備。圖10說明了寫和讀時隙的定義。

所有通信均由總線主設備拉低數據線開始。當一線總線電平降至閾值(V_{IL})以下時,DS28E10啟動內部定時發生器,該發生器決定何時對數據線進行采樣。

-

SHA-1

+關注

關注

0文章

8瀏覽量

9803 -

EPROM

+關注

關注

3文章

136瀏覽量

55142 -

1-Wire

+關注

關注

0文章

70瀏覽量

21599

發布評論請先 登錄

DS2465 SHA-256協處理器與1-Wire主機功能

為什么1-Wire SHA-1器件是安全的?

DS28E10 1 - Wire協議

DS28E04-100 4096位,1-Wire EEPROM芯片

ADI推出DS28E30 1-Wire ECDSA安全認證器

DS28E25: DeepCover Secure Authenticator with 1-Wire SHA-256 and 4Kb User EEPROM Data Sheet DS28E25: DeepCover Secure Authenticator with 1-Wi

DS28EL22: DeepCover Secure Authenticator with 1-Wire SHA-256 and 2Kb User EEPROM Data Sheet DS28EL22: DeepCover Secure Authenticator with 1-

DS28E40: Deep Cover Automotive 1-Wire Authenticator Data Sheet DS28E40: Deep Cover Automotive 1-Wire Authenticator Data Sheet

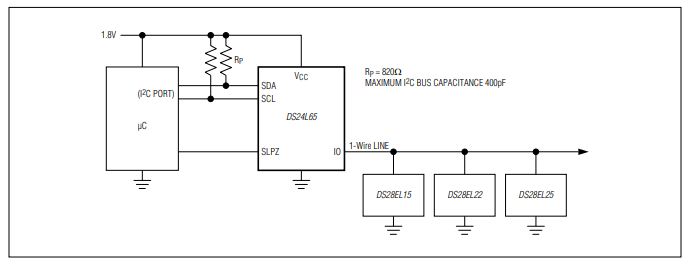

DS24L65 DeepCover安全認證器,具有SHA-256協處理器和1-Wire主機功能技術手冊

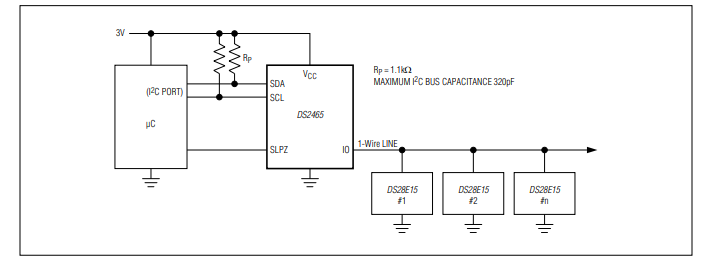

DS28E25內置1-Wire SHA-256和4Kb用戶EEPROM的DeepCover安全認證方案

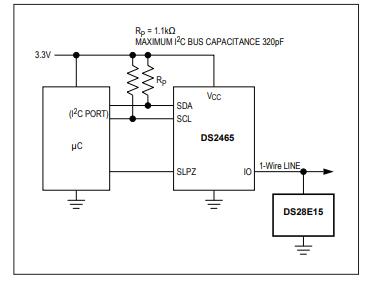

DS28E15內置1-Wire SHA-256和512位用戶EEPROM的DeepCover安全認證方案

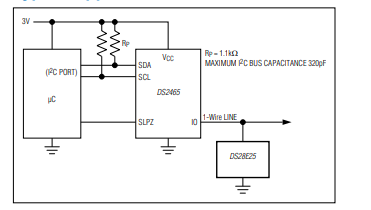

DS2465 DeepCover安全認證器具有SHA-256協處理器和1-Wire主機功能技術手冊

DS28E02 1-Wire SHA-1認證器,具有1Kb EEPROM,工作在1.8V技術手冊

DS28E01-100 1Kb、保護型1-Wire EEPROM,帶有SHA-1引擎技術手冊

DS28E10 1-Wire SHA-1認證器技術手冊

DS28E10 1-Wire SHA-1認證器技術手冊

評論