概述

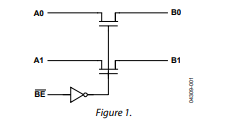

ADG3241是一款2.5 V或3.3 V、單通道數字開關,采用低壓CMOS工藝制造,具有低功耗、高開關速度和極低導通電阻特性。輸入可以與輸出相連,而且不會引起額外的傳播延遲或產生額外的接地反彈噪聲。

數據表:*附件:ADG3241 2.5 V或3.3 V、1位、2端口電平轉換器總線開關技術手冊.pdf

特性

- 開關傳播延遲:225 ps

- 端口之間采用4.5 Ω開關連接

- 數據速率:1.5 Gbps

- 2.5 V/3.3 V 電源供電

- 可選電平轉換

- 電平轉換

- 3.3 V 轉 2.5 V

- 3.3 V t轉 1.8 V

- 2.5 V轉1.8 V

- 小信號帶寬:770 MHz

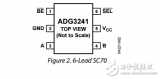

- 6引腳SC70封裝

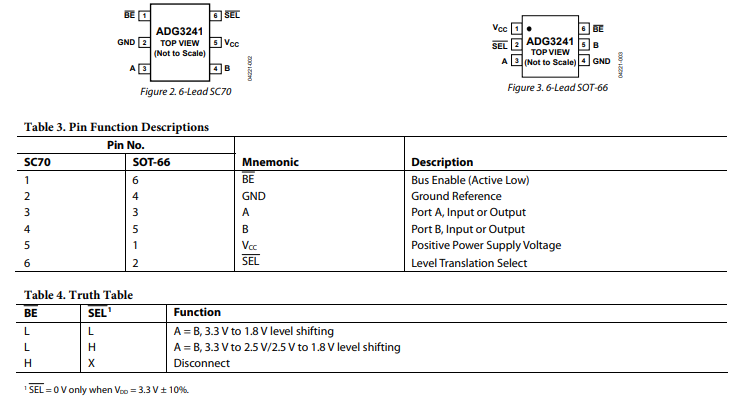

引腳配置描述

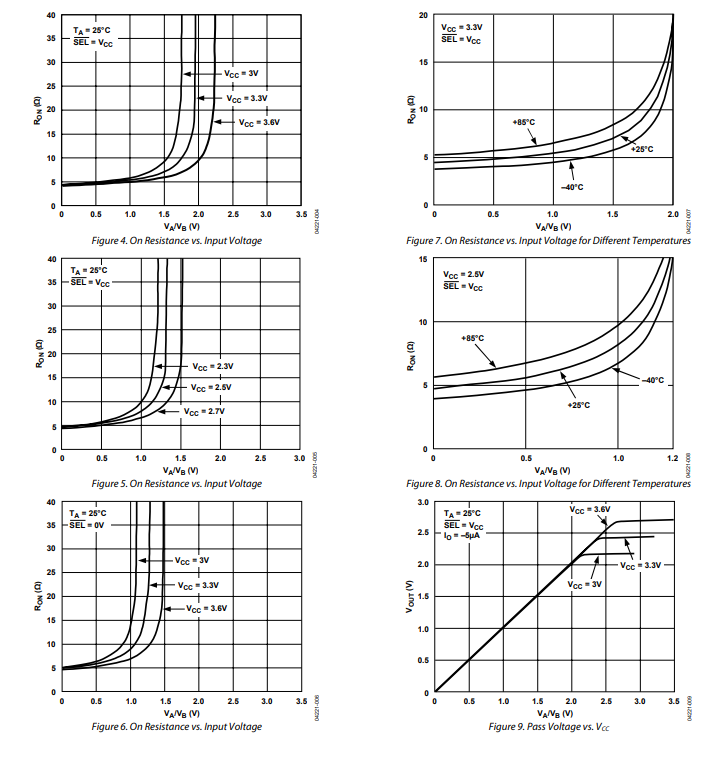

典型性能特征

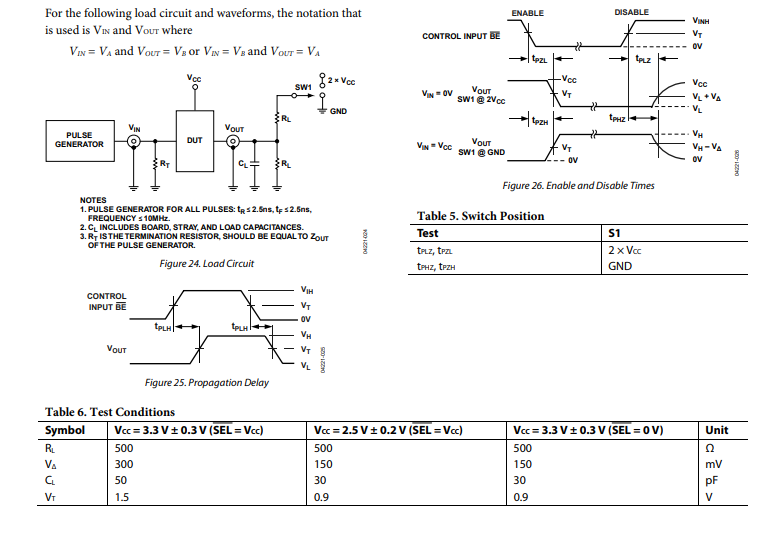

定時測量信息

總線開關應用:混合電壓操作、電平轉換

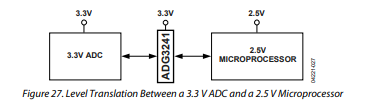

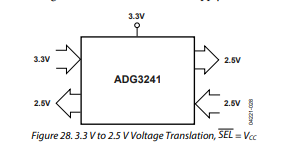

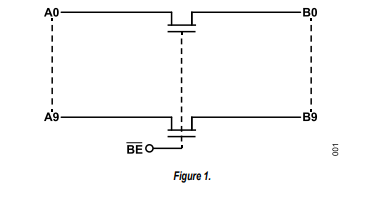

總線開關能夠為混合電壓系統之間的接口提供理想解決方案。ADG3241適用于需要從3.3V技術轉換為較低電壓技術的應用場景。該器件可實現從3.3V到1.8V、從2.5V到1.8V,或者從3.3V直接到2.5V的電壓轉換。

圖27展示了一個典型應用的框圖,在該應用中,用戶需要實現3.3V ADC與2.5V微處理器之間的接口。微處理器可能不具備3.3V耐壓輸入,因此,在這兩個器件之間放置ADG3241可使它們輕松通信。總線開關直接連接這兩個模塊,因此幾乎不會引入傳播延遲、定時偏差或噪聲。

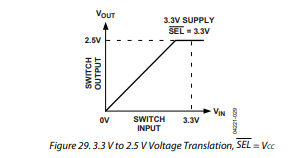

3.3V至2.5V轉換

當 V_{CC} 為3.3V(overline{SEL} = 3.3V)且輸入信號范圍為0V到 V_{CC} 時,最大輸出信號將被鉗位在 V_{CC} 電源以下的一個電壓閾值內。在這種情況下,輸出將限制為2.5V,如圖29所示。該器件可用于2.5V到3.3V器件之間的雙向轉換,也可用于兩個3.3V器件之間。

-

CMOS

+關注

關注

58文章

6021瀏覽量

238838 -

開關

+關注

關注

19文章

3282瀏覽量

95359 -

電平轉換器

+關注

關注

1文章

220瀏覽量

20145

發布評論請先 登錄

ADG3241,pdf datasheet (Level T

1/2端口電平轉換器母線開關sot-66的ADG3241數據表

ADG3241 2.5 V/3.3 V、1位、2端口電平轉換器總線開關

ADG3241 2.5 V/3.3 V、1位、2端口電平轉換器總線開關技術手冊

ADG3241 2.5 V/3.3 V、1位、2端口電平轉換器總線開關技術手冊

評論