電子發(fā)燒友網(wǎng)報(bào)道(文/李彎彎)近日消息,英特爾與軟銀集團(tuán)宣布達(dá)成戰(zhàn)略合作,共同開(kāi)發(fā)具有劃時(shí)代意義的AI專用內(nèi)存芯片。這項(xiàng)合作將致力于突破當(dāng)前AI計(jì)算中的能耗瓶頸,有望將芯片功耗降低50%,為全球AI基礎(chǔ)設(shè)施建設(shè)帶來(lái)革命性變化。

隨著AI技術(shù)的快速發(fā)展,高性能、低功耗的計(jì)算硬件需求日益增長(zhǎng)。然而,現(xiàn)有的AI內(nèi)存技術(shù)存在高成本、高功耗及發(fā)熱問(wèn)題,限制了AI數(shù)據(jù)中心的進(jìn)一步擴(kuò)展和效率提升。據(jù)悉,軟銀與英特爾將研發(fā)一種創(chuàng)新的堆疊式DRAM芯片,采用全新的布線架構(gòu),完全不同于現(xiàn)有高帶寬內(nèi)存(HBM)技術(shù)方案。

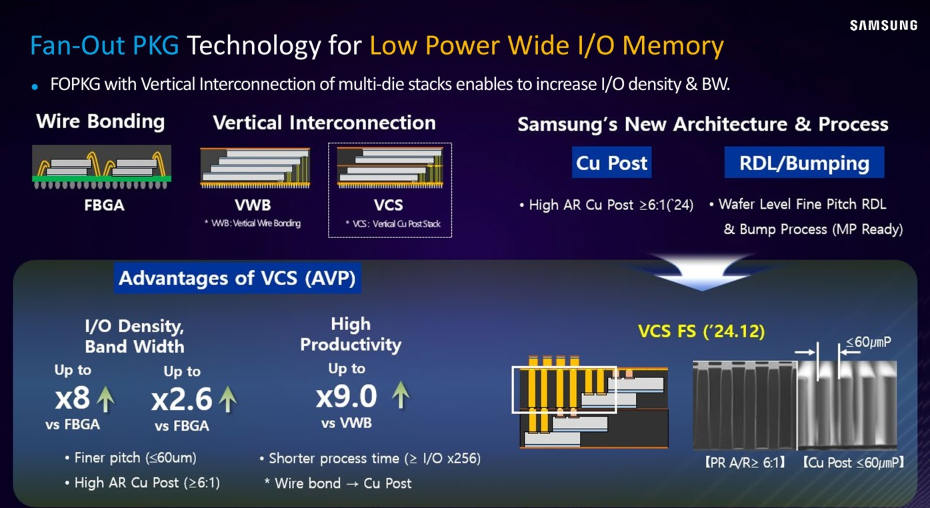

這種新型AI內(nèi)存芯片可能在哪些方面進(jìn)行創(chuàng)新呢?首先,在架構(gòu)層面,現(xiàn)有HBM技術(shù)主要采用TSV(硅通孔)垂直互連技術(shù)實(shí)現(xiàn)芯片堆疊,而創(chuàng)新方案采用全新布線架構(gòu),可能突破傳統(tǒng)TSV的布局限制,通過(guò)更優(yōu)化的布線設(shè)計(jì)減少信號(hào)傳輸路徑的曲折和干擾,從而降低信號(hào)延遲和功耗。例如,可能采用新的層間互連方式,使數(shù)據(jù)在芯片堆疊層之間的傳輸更加直接高效。

HBM通過(guò)寬接口和并行傳輸實(shí)現(xiàn)高帶寬,創(chuàng)新方案可能進(jìn)一步優(yōu)化通道數(shù)量和數(shù)據(jù)接口設(shè)計(jì)。比如增加通道數(shù)量,或者改進(jìn)數(shù)據(jù)接口的信號(hào)傳輸機(jī)制,提高數(shù)據(jù)傳輸?shù)男屎头€(wěn)定性,在相同甚至更低的功耗下實(shí)現(xiàn)更高的帶寬。

在芯片堆疊與封裝層面,不同于HBM的堆疊方式,創(chuàng)新方案可能采用全新的芯片堆疊結(jié)構(gòu),提高堆疊密度和穩(wěn)定性。例如,采用更緊密的堆疊方式,減少芯片之間的間隙,從而降低整體封裝尺寸和信號(hào)傳輸距離。

還可以通過(guò)改進(jìn)封裝技術(shù),提高芯片的散熱性能和電氣連接可靠性。例如,采用更高效的散熱材料和封裝結(jié)構(gòu),及時(shí)將芯片產(chǎn)生的熱量散發(fā)出去,避免因過(guò)熱導(dǎo)致的性能下降和功耗增加;同時(shí),優(yōu)化芯片與封裝基板之間的電氣連接,降低連接電阻,減少功耗。

據(jù)稱,英特爾與軟銀這種突破性設(shè)計(jì)不僅大幅提升能效比,更將為AI數(shù)據(jù)中心的綠色轉(zhuǎn)型提供關(guān)鍵技術(shù)支持。業(yè)內(nèi)專家指出,該技術(shù)若能成功商業(yè)化,將顯著降低AI計(jì)算的運(yùn)營(yíng)成本,對(duì)推動(dòng)可持續(xù)發(fā)展具有重要意義。

為推進(jìn)這一重大項(xiàng)目,雙方聯(lián)合成立了專門公司Saimemory,負(fù)責(zé)芯片的設(shè)計(jì)和專利管理。制造環(huán)節(jié)則委托專業(yè)代工廠完成,這種分工協(xié)作模式有望最大化研發(fā)效率。研發(fā)團(tuán)隊(duì)將采用不同于現(xiàn)有HBM技術(shù)的布線方式,通過(guò)垂直堆疊多顆DRAM芯片,并改進(jìn)芯片間的互連技術(shù),實(shí)現(xiàn)至少大一倍的存儲(chǔ)容量,同時(shí)將耗電量減少40%以上。

根據(jù)項(xiàng)目規(guī)劃,研發(fā)團(tuán)隊(duì)將在兩年內(nèi)完成芯片原型設(shè)計(jì),之后啟動(dòng)量產(chǎn)評(píng)估程序,目標(biāo)是在本世紀(jì)二十年代末實(shí)現(xiàn)商業(yè)化應(yīng)用。項(xiàng)目總投資額預(yù)計(jì)達(dá)100億日元(約合5億元人民幣),其中軟銀作為領(lǐng)投方已承諾注資30億日元(約1.5億元人民幣)。

不過(guò),盡管軟銀與英特爾在芯片設(shè)計(jì)和制造方面擁有豐富的經(jīng)驗(yàn)和技術(shù)積累,但新型AI內(nèi)存芯片的研發(fā)仍面臨諸多技術(shù)挑戰(zhàn),如這種創(chuàng)新的式DRAM芯片的良率控制、量產(chǎn)成本能否真正低于HBM等。

當(dāng)然,隨著AI技術(shù)的廣泛應(yīng)用和數(shù)據(jù)中心規(guī)模的不斷擴(kuò)大,高性能、低功耗的內(nèi)存技術(shù)需求將持續(xù)增長(zhǎng)。如果新型AI內(nèi)存芯片能夠成功商業(yè)化并滿足市場(chǎng)需求,將具有廣闊的市場(chǎng)前景和商業(yè)價(jià)值。

-

DRAM

+關(guān)注

關(guān)注

40文章

2343瀏覽量

185288 -

HBM

+關(guān)注

關(guān)注

1文章

409瀏覽量

15152

發(fā)布評(píng)論請(qǐng)先 登錄

風(fēng)景獨(dú)好?12層HBM3E量產(chǎn),16層HBM3E在研,產(chǎn)業(yè)鏈涌動(dòng)

芯片晶圓堆疊過(guò)程中的邊緣缺陷修整

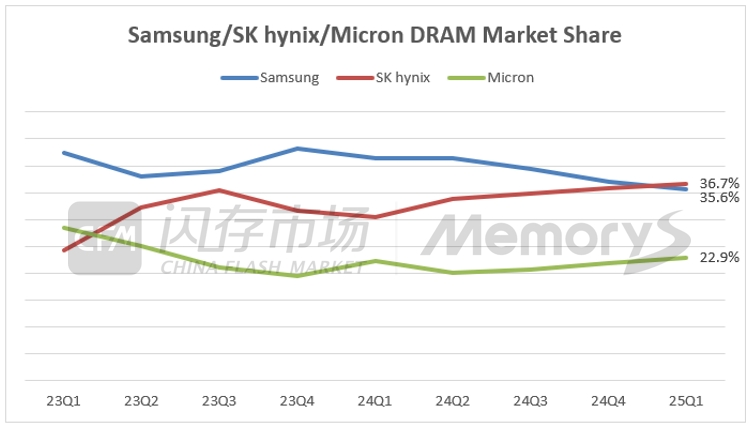

HBM重構(gòu)DRAM市場(chǎng)格局,2025年首季DRAM市占排名

三星調(diào)整1cnm DRAM設(shè)計(jì),力保HBM4量產(chǎn)

Kioxia開(kāi)源發(fā)布AiSAQ?技術(shù),降低生成式AI的DRAM需求

AI興起推動(dòng)HBM需求激增,DRAM市場(chǎng)面臨重塑

AI時(shí)代核心存力HBM(上)

三星電子HBM3E商業(yè)化遇阻,或重新設(shè)計(jì)1a DRAM電路

節(jié)能回饋式負(fù)載技術(shù)創(chuàng)新與發(fā)展

預(yù)計(jì)第四季度DRAM市場(chǎng)僅HBM價(jià)格上漲

SK海力士12層堆疊HBM3E率先量產(chǎn)

堆疊REF50xx實(shí)現(xiàn)高電壓基準(zhǔn)

繼HBM上車之后,移動(dòng)HBM有望用在手機(jī)上

不同于HBM,這種創(chuàng)新的堆疊式DRAM,功耗有望降低50%

不同于HBM,這種創(chuàng)新的堆疊式DRAM,功耗有望降低50%

評(píng)論