三星周二舉行晶圓代工技術(shù)論壇(Samsung Foundry Forum),同時(shí)揭露發(fā)展3納米制程的技術(shù)路圖,以及7納米投產(chǎn)進(jìn)度,將搶攻高端運(yùn)算與聯(lián)網(wǎng)裝置市場(chǎng)。

三星晶圓代工部門總裁鄭恩昇(E.S. Jung)表示,3納米制程將首度導(dǎo)入閘極全環(huán)(GAA)電晶體,這是下一世代電晶體架構(gòu),并將配合極紫外光(EUV)微影設(shè)備,來(lái)克服物理限制。(cdrinfo.com)

三星7納米是第一個(gè)采用EUV技術(shù)的半導(dǎo)體制程,按計(jì)劃將在2018下半年投產(chǎn)。據(jù)三星表示,關(guān)鍵知識(shí)產(chǎn)權(quán)(IP)已在開(kāi)發(fā),將于2019年上半年完成。

有趣的是,三星表示7納米將應(yīng)用在網(wǎng)絡(luò)、汽車領(lǐng)域,而非效能要求較高的繪圖處理器(GPU),意謂著三星7納米技術(shù)似乎未能獲得Nvidia與超微青睞。

超微日前已宣布下一世代Zen 2中央處理器與Navi繪圖處理器,都將交予臺(tái)積電以7納米制程代工。

-

三星電子

+關(guān)注

關(guān)注

34文章

15885瀏覽量

182237 -

晶圓

+關(guān)注

關(guān)注

53文章

5136瀏覽量

129541 -

EUV

+關(guān)注

關(guān)注

8文章

609瀏覽量

87075

發(fā)布評(píng)論請(qǐng)先 登錄

三星在4nm邏輯芯片上實(shí)現(xiàn)40%以上的測(cè)試良率

全球芯片產(chǎn)業(yè)進(jìn)入2納米競(jìng)爭(zhēng)階段:臺(tái)積電率先實(shí)現(xiàn)量產(chǎn)!

英偉達(dá)、高通或轉(zhuǎn)單三星2納米工藝

臺(tái)積電2納米制程技術(shù)細(xì)節(jié)公布:性能功耗雙提升

臺(tái)積電2納米制程技術(shù)細(xì)節(jié)公布

三星芯片代工新掌門:先進(jìn)與成熟制程并重

關(guān)于RISC-V學(xué)習(xí)路線圖推薦

三星加速2nm及1.4nm制程投資

晶合集成28納米邏輯工藝通過(guò)驗(yàn)證

三星電子計(jì)劃在2026年推出最后一代10nm級(jí)工藝1d nm

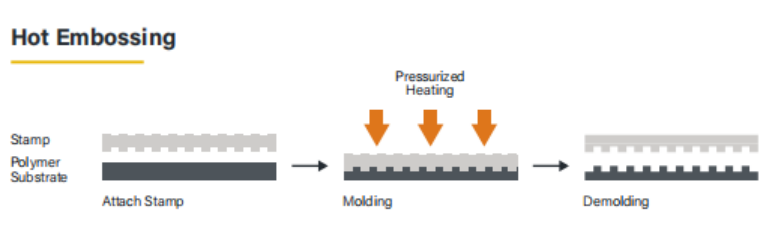

納米壓印技術(shù)的分類和優(yōu)勢(shì)

臺(tái)積電2025年繼續(xù)漲價(jià),5/3納米制程產(chǎn)品預(yù)計(jì)漲幅3~8%

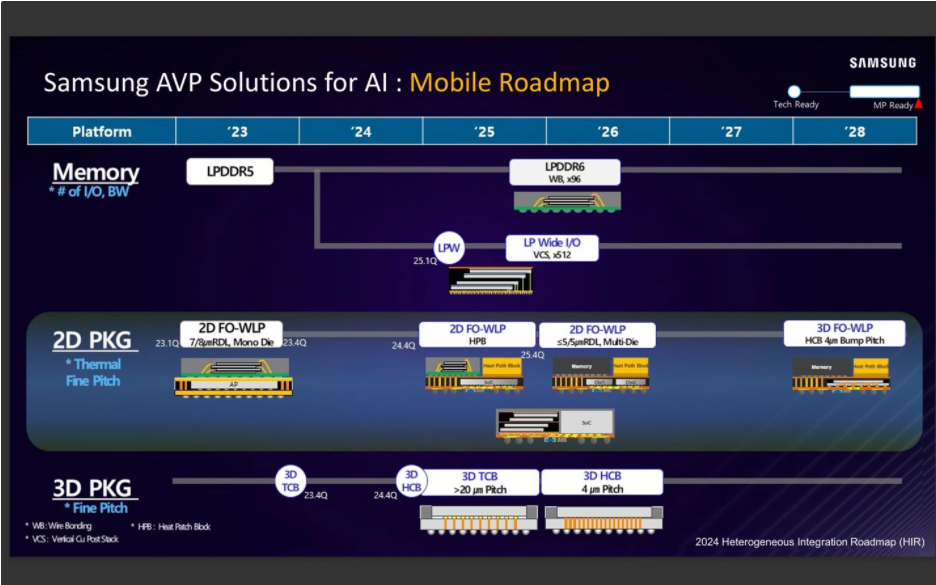

三星電子公布2024年異構(gòu)集成路線圖,LP Wide I/O移動(dòng)內(nèi)存即將面世

三星揭露3納米制程技術(shù)路線圖以及7納米投產(chǎn)進(jìn)度

三星揭露3納米制程技術(shù)路線圖以及7納米投產(chǎn)進(jìn)度

評(píng)論