濾波器是通信系統中的重要部件。數字濾波器的實現一般有3 條途徑: (1) 由通用DSP 芯片編程實現; (2) 選用已有的專用濾波器芯片實現; (3) 根據系統要求自行設計濾波器, 并用FPGA 實現。隨著數字通信速率的快速提高, 對濾波器的運算速度的要求也愈來愈高。在數據傳輸率為54M b it?s, 符合HyperL an2 的寬帶無線WLAN 收發器的研究實驗中, 數據的基帶速率為20MByte?s, 經4 倍升采樣為80MByte?s, 在此升采樣(在接收鏈路中為降采樣) 過程中必須實現數字上下變頻和抗混疊濾波器。如此高速的濾波器如用通用DSP 實現, 則將占用該DSP 的絕大部分運算資源, 使DSP 幾乎不能承擔其他編解碼等任務。

這種情況下, 最好的選擇是用FPGA 硬件實現上下變頻和濾波。雖然目前市場上有一些用于FPGA 實現上下變頻和F IR濾波器的IP 軟核, 但這些軟核由于追求通用性和可配置性, 在代碼效率、運行速度、系統集成緊湊性和FPGA 資源用量最小化等方面很難滿足要求或達到最優化。

因此, 根據具體系統的運行要求, 暫不強求通用性和可重新配置性, 而著重研究實現上下變頻濾波的高速度和FPGA 資源用量最小化。資源用量最小化可以在一片FPGA 上集成更多的功能電路, 例如增益自動控制功能等, 即可能實現片上系統(SoC)。為了在實現高速的同時, 減少FP2GA 的資源占用量, 一方面可以研究具體FPGA 的底層結構特點, 人工干預底層電路綜合來組建系統, 另一方面要研究被設計電路的實現結構、算法和編碼方式等, 從中選擇快速有效和硬件復雜度最低的實現方法。

本文根據寬帶WLAN 的收發器要求, 在系統總體結構安排、濾波器結構設計、乘加運算算法, 以及流水線實現等方面進行研究, 在實現高速度的同時, 使得系統資源的占用量達到最小。

達到這一目標的主要技術要點有: (1) 充分利用上下變頻器結構特點, 只用一套濾波器運算單元實現上變頻濾波和下變頻濾波; (2) 充分利用收發器的數據流特點和F IR 濾波器系數特點, 用該濾波器運算單元同時實現對I,Q 兩個數據流的變頻和濾波; (3) 分別用傳統濾波器的轉置結構和獨特的位平面結構設計實現高速上下變頻和濾波(80MHz 運算速度的40 階上下變頻F IR 濾波器)。并對二者的實現結構和綜合結果進行比較, 說明在達到同樣速度的前提下, 位平面結構僅占用轉置結構所用邏輯資源的一半。在下一步對位平面結構的通用性設計有所改進后, 位平面結構應成為高速濾波器的主要設計方法; (4) 合理劃分和優化各級流水線的性能是實現上下變頻濾波高速運行的關鍵。

寬帶無線通信的數字上下變頻

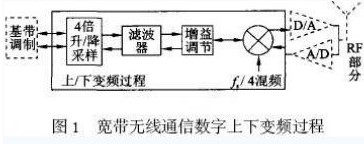

數字上下變頻過程是數字通信系統中必不可少的實現環節。上變頻就是用數字信號處理的手段將基帶已調制信號的頻帶搬移到中頻( IF) 的過程。上變頻得到的數字IF 信號經DAC 變換為模擬信號后, 再在模擬域變換為RF 信號, 通過天線發送出去, 實現數字信號的發送(圖1 的右箭頭方向表示信號的發送步驟)。無線信號的接收過程(圖1 的左箭頭方向) 和發送過程完全相反, 即在A?D 變換得到數字IF 后, 經數字下變頻變換為基帶調制信號, 再經數字解調最后得到接收的信息。在符合HyperLan2 傳輸協議的WLAN 的收發器實驗中,數據傳輸率高達54M b it?s, 其基帶O FDM 調制輸出的I,Q 信號采樣頻率高達20MBytes。

圖1 實線框內是本文設計實現的上下變頻過程, 它們被集成在一片FPGA 上。基帶輸出的I,Q 信號, 經4 倍增采樣、去混疊濾波、增益補償后和20MHz (f s?4混頻, f s 為采樣頻率) 的數字載波信號復混頻。數字IF 信號的采樣率升為80M SPS, 基帶信號的中心頻率被移至20MHz。這一過程中濾波器起著至關重要的作用, 它保證基帶信號的頻譜在升降采樣過程和混頻過程中不發生混疊和展寬。濾波器的主要指標為: Remez 40 階低通F IR 濾波器; 通帶帶寬10MHz; 阻帶抑制比- 50 dB; 輸入信號采樣頻率80MHz; 濾波器系數量化為12bit 有符號數表示。

上下變頻濾波器的實現

濾波器的輸入數據流特點

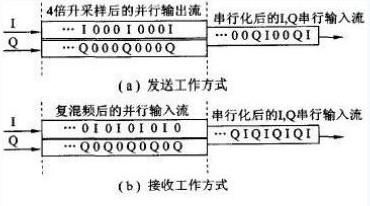

基帶調制的信號輸出形式是I (8bit) 和Q (8bit ) 的并行輸出。 在數據發送方式時, I,Q 信號直接饋入上變頻器。4 倍升采樣過程是分別在I 和Q序列中每相鄰點之間插入3 個0, 從而數據率升為80MHz。利用升采樣后的這一特點, 可以將并行的I,Q 數據串行化, 如圖2 (a) 所示。在接收數據方式下, RF 信號經80MSPS 的AD 采樣后輸出饋入下變頻器。在下變頻器中的第一步處理是中心頻率下移的復混頻。輸入信號分別和相位相差90°的正弦波數字相乘, 從而分解出I,Q 兩路信號。用于復混頻的正弦波和余弦波的中心頻率為20MHz, 每周期取4 個點, 其中有2 個點為0, 另2 個點分別為+ 1 和- 1。這樣得到的I,Q 信號相鄰兩點之間必為零值, 如圖2 (b) 所示。和發送工作方式一樣, 可以將并行的I,Q 信號串行化。這樣在兩種工作方式下, 濾波器的輸入并行數據流均先變換成8bit寬的串行輸入流。

濾波器的轉置結構實現

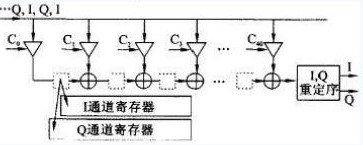

FIR 濾波器的輸出是輸入信號與濾波器系數的卷積求和。根據卷積表達式的計算形式, 傳統上很自然地會得到濾波器的直接形式的實現結構。由于用直接形式實現的濾波器的輸出延遲較大且與濾波器階數成正比, 在硬件實現上, 一般都使用直接形式的轉置結構, 如圖3 所示。串行化后的I,Q 數據流, 以80MHz 速率同時饋入40 個乘法器和濾波器系數分別相乘, 所得結果作為加法器的一個輸入量。加法器的另一輸入量是前一個加法器在上一個時鐘節拍的輸出結果, 它是由圖3 中小方框表示的寄存器緩存。

為了用一個濾波器硬件同時對I,Q 濾波, 設計中充分利用串行輸入流的特點, 用兩套寄存器( I,Q 通道寄存器, 16 b it 寬) 分別緩沖和延遲I 通道濾波的中間結果和Q 通道的中間結果, 即相當于濾波器被I 通道和Q 通道分時復用,在輸出端再按序將它們分開, 輸出并行的I,Q 數據流。在FPGA 的編程實現中, 乘法器采用Xilinx的N 位變量和M 位常量相乘產生M + N 位積的乘法器IP 軟核。由于該軟核充分利用了FPGA 查表(Look-up ) 的硬件單元結構來實現乘法, 速度較快, 一次相乘運算用時小于12 n s。

濾波器的位平面結構實現

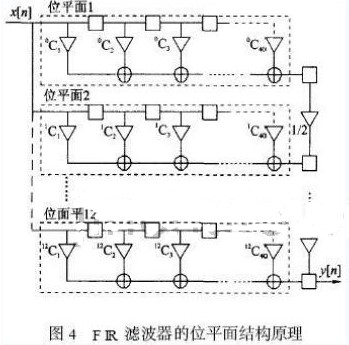

上述濾波器的轉置結構是濾波器設計的傳統方法。而用位平面結構快速有效地實現乘2加運算的基本思想早在86 年就被提出, 由于將其應用于濾波器設計在通用性和可重新配置性方面不如轉置結構簡單, 所以一直不被廣泛應用。但位平面結構的高速度和高代碼效率卻是不容忽視的, 特別是在當今SoC 的設計實現方面。位平面結構的本質就是重新安排濾波器乘積求和運算過程的順序。

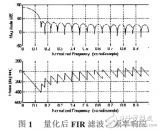

圖4 是直接形式的位平面結構原理說明, 其中每一個方框部分代表一個位平面, 分別標記為位平面1、位平面2 等。在每一個位平面內, 和輸入數據相乘的僅是濾波器系數的一個b it, 位平面1 為各系數的最低位L SB, 位平面2 是各系數的最低第二位, 依此類推, 位平面12 是各系數的M SB。因為濾波器系數為12 b it 寬, 所以共有12 個位平面。輸入數據同時輸入到各個位平面, 所有位平面并行計算對應位的部分積及其累加結果。最后, 在每個時鐘節拍下, 位平面1 輸出結果右移一位(除以2) 和位平面2 輸出相加, 所得結果除以2, 再和位平面3的輸出相加, 這樣繼續相加直至最后一個位平面。由于在位平面內的乘數僅為單個b it (0 或者1) , 實質上濾波器的乘2加運算已轉化為純相加運算。

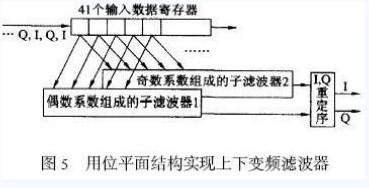

為了能夠用一套濾波器同時對I,Q 數據流進行濾波, 采用圖5 所示的上下變頻濾波器的總體結構, 其中將整個濾波器拆分為兩個子濾波器, 它們均由位平面結構實現。子濾波器1 的奇數系數設定為0, 而偶數系數不變; 子濾波器2 的偶數系數改變為0, 而奇數系數不變。輸入的串行化的I,Q 數據流被40 個數據寄存器移位緩存, 兩個子濾波器分別交替計算純I 和Q 的輸出值, 例如, 在某一時鐘, 子濾波器1 完全忽略奇數位置上的輸入數據,計算得到的是I 流的濾波結果, 與此同時, 子濾波器2 完全忽略偶數位置上的輸入數據, 而計算輸出Q 流的計算結果。在下一時鐘計算內容與此相反:子濾波器1 計算輸出Q 流結果, 而子濾波器2 計算輸出I 流結果。最后由I,Q 重定序部分將這種I,Q 交織排列轉換為平行輸出的I,Q 流。

測試結果與比較

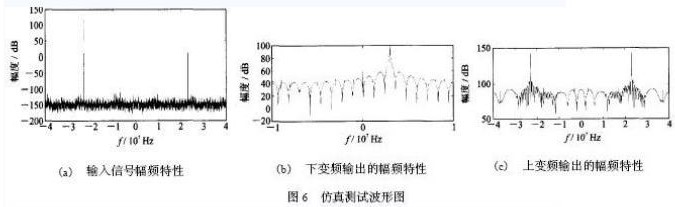

整個上下變頻器被集成在一片Xilinx FPGA XCV 600HQ 24026 上, 由VHDL 設計完成, 其中濾波器分別用上述兩種結構實現。圖6 是設計的仿真測試結果。測試過程如下: 先用M at lab 產生如圖6(a) 所示的正弦波, 作為輸入文件, 測試用VHDL設計的下變頻功能, 得到的下變頻輸出如圖6 (b)所示。其中23MHz 的輸入信號被下移了20MHz,且輸出信號的信噪比大于50 dB; 在測試上變頻功能時, 將下變頻的輸出信號作為VHDL 設計的輸入信號, 得到上變頻的輸出結果如圖6 (c) 所示。圖中3MHz 的信號又被上移到23MHz 位置。用兩種濾波器結構設計的變頻器得到了幾乎相同的測試結果, 最大運行速度均大于80MHz, 但它們占用芯片資源的情況卻不同(見表1) , 其中邏輯資源單元(Slices) 的占用數相差一半。

結束語

用FPGA 設計實現濾波器, 采用位平面結構在芯片資源利用率方面占明顯優勢。這主要得益于位平面結構實現濾波器乘積2累加運算的獨特方式。每一位平面計算得到的部分積通過右移一位被及時丟棄而不致影響運算精度。這就省去了一般乘法運算實現時, 為避免精度變差存儲中間結果的寄存器必須留有足夠的保護位。位平面結構中的運算順序避免了大量的移位操作, 比較適合FPGA 的結構特點。如果濾波器系數中含有更多的0 bit 位, 將會減小求和操作次數, 進一步提高運算速度。相對于轉置結構, 位平面結構的最大缺點是輸入和輸出之間有較大的延遲, 這主要是由于位平面內直接形式結構的固有延遲和各個位平面在最后輸出求和過程的流水線結構所造成的, 但一般不影響實際應用。

-

FPGA

+關注

關注

1632文章

21816瀏覽量

607053 -

濾波器

+關注

關注

161文章

7900瀏覽量

179254 -

變頻器

+關注

關注

252文章

6603瀏覽量

146184

發布評論請先 登錄

相關推薦

實現FPGA數字下變頻的多類濾波器分組級聯技術分析

基于FPGA的FIR濾波器設計與實現

基于FPGA的FIR濾波器IP仿真實例

基于IP核的FIR低通濾波器該怎么設計?

數字下變頻中抽取濾波器的設計及FPGA實現

FIR濾波器的FPGA設計與實現

利用FPGA硬件實現高速上下變頻和FIR濾波器的IP軟核的設計

利用FPGA硬件實現高速上下變頻和FIR濾波器的IP軟核的設計

評論