華為每年至少拿出10億美元的研發(fā)預算,用于與數(shù)據(jù)中心相關的投入。

2017年9月,華為發(fā)布了面向企業(yè)、政府的人工智能服務平臺華為云EI。今年4月,華為又發(fā)布了面向智能終端的人工智能引擎HiAI。

AI再次進入了“收獲”的季節(jié)。這是60年來全球ICT學術界和工業(yè)界長期耕耘,相互合作的成果。如同公元前的輪子和鐵,19世紀的鐵路和電力,以及20世紀的汽車、電腦、互聯(lián)網(wǎng)一樣,華為認同:人工智能是一組技術集合,是一種新的通用目的技術(GPT)。

華為在AI上的全新戰(zhàn)略,包括人工智能芯片、基于芯片賦予技術框架的CANN和訓練框架MindSpore、以及ModelArts,華為將其稱之為“全棧全場景AI解決方案”。

“之前一直傳華為要做AI芯片,這確實是真的。”華為輪值董事長徐直軍在今天上海舉行的第三屆HUAWEI CONNECT 2018(華為全聯(lián)接大會)上如是說。

徐直軍提出了10個人工智能的重要改變方向:模型訓練、算力、AI部署、算法、AI自動化、實際應用、模型更新、多技術協(xié)同、平臺支持、人才獲得。這十個改變不是人工智能的全部,但是基礎。

基于這十個改變,華為制定了人工智能發(fā)展戰(zhàn)略:投資基礎研究、打造全棧方案、投資開放生態(tài)和人才培養(yǎng)、解決方案增強、內部效率提升。

今天發(fā)布的華為昇騰910(Ascend 910),是目前全球已發(fā)布的單芯片計算密度最大的AI芯片,還有Ascend 310,是目前面向計算場景最強算力的AI SoC。”

具體來看,華為所說的“全棧”包含四個部分:

一是Ascend (昇騰) ,AI IP和芯片,皆是基于達芬奇架構。芯片分為5個系列,Max、Lite、Mini、Tiny、Nano。

二是CANN,全稱為Compute Architecture for Neural Networks (為神經網(wǎng)絡定制的計算架構) ,是高度自動化的算子開發(fā)工具。根據(jù)官方數(shù)據(jù),CANN可以3倍提升開發(fā)效率。除了效率之外,也兼顧算子性能,以適應學術和行業(yè)應用的迅猛發(fā)展。

三是MindSpore架構,友好地將訓練和推理統(tǒng)一起來,集成了各類主流框架 (獨立的和協(xié)同的) :包括TensorFlow、PyTorch、PaddlePaddle、Keras、ONNX、Caffe、Caffe 2、MXNet等等。這一架構全面適應了端、邊、云場景。

四是ModelArts,這是一個機器學習PaaS (平臺即服務) ,提供全流程服務、分層分級API,以及預集成方案。用于滿足不同開發(fā)者的不同需求,促進AI的應用。

此外,徐直軍在現(xiàn)場透露,華為昇騰910將在2019年2季度上市。

根據(jù)現(xiàn)場的介紹,這款屬于Max系列的昇騰910,采用7nm工藝制程,最大功耗為350W。在現(xiàn)場的PPT中,華為將其和谷歌TPU v2、谷歌TPU v3、英偉達 V100進行了對比。“可以達到256個T,比英偉達 V100還要高出1倍!”徐直軍說。

華為昇騰芯片910和310都是基于“達芬奇架構”,是一個全新的AI架構。

之前有媒體寫到華為有個“達芬奇計劃”,是近十年來最重要的一個計劃,也是徐直軍負責的項目。此次,徐直軍做了澄清,他說確實有“達芬奇項目”但沒有“達芬奇計劃”,除此之外,其他信息外界傳遞的信息都不是真的。

徐直軍表示,自己會關心每個項目,而達芬奇項目是其中之一。

“為什么要構建新架構來支持人工智能芯片,是因為這是基于華為對人工智能的理解,基于端管云對對人工智能的需求自然產生的。”徐直軍表示,“寒武紀也很好,但無法支持我們的全場景。”

其表示,華為需要覆蓋從云、到邊緣、到端到物聯(lián)網(wǎng)端,需要全新的架構,創(chuàng)造力的架構。

“現(xiàn)在,我們找到了這個架構。我們開創(chuàng)性的達芬奇架構,滿足了極致的算力需求和極致的功耗需求,目前我們還沒看到市場上有何架構可以實現(xiàn)全覆蓋。”徐直軍表示。

臺積電7nm EUV芯片首次流片成功

全球一號代工廠臺積電宣布了有關極紫外光刻(EUV)技術的兩項重磅突破,一是首次使用7nm EUV工藝完成了客戶芯片的流片工作,二是5nm工藝將在2019年4月開始試產。

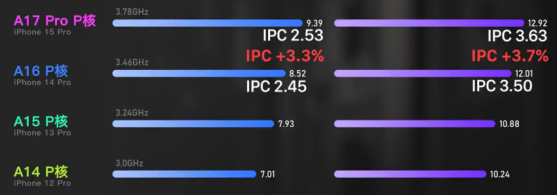

今年4月開始,臺積電第一代7nm工藝(CLN7FF/N7)投入量產,蘋果A12、華為麒麟980、高通“驍龍855”、AMD下代銳龍/霄龍等處理器都正在或將會使用它制造,但仍在使用傳統(tǒng)的深紫外光刻(DUV)技術。

而接下來的第二代7nm工藝(CLNFF+/N7+),臺積電將首次應用EUV,不過僅限四個非關鍵層,以降低風險、加速投產,也借此熟練掌握ASML的新式光刻機Twinscan NXE。

7nm EVU相比于7nm DUV的具體改進公布得還不多,臺積電只說能將晶體管密度提升20%,同等頻率下功耗可降低6-12%。

如今在7nm EUV工藝上成功完成流片,證明了新工藝新技術的可靠和成熟,為后續(xù)量產打下了堅實基礎。

臺積電沒有透露這次流片成功的芯片來自哪家客戶,但是想想各家和臺積電的合作關系,其實不難猜測。

7nm之后,臺積電下一站將是5nm(CLN5FF/N5),將在多達14個層上應用EUV,首次全面普及,號稱可比初代7nm工藝晶體管密度提升80%從而將芯片面積縮小45%,還可以同功耗頻率提升15%,同頻功耗降低20%。

2019年4月,臺積電的5nm EUV工藝將開始風險性試產,量產則有望在2020年第二季度開始,正好滿足后年底各家旗艦新平臺。

臺積電5nm工藝的EDA設計工具將在今年11月提供,因此部分客戶應該已經開始基于新工藝開發(fā)芯片了。

隨著半導體工藝的急劇復雜化,不僅開發(fā)量產新工藝的成本大幅增加,開發(fā)相應芯片也越來越費錢,目前估計平均得花費1.5億美元,5nm時代可能要2-2.5億美元。

PS:Intel剛發(fā)布的秋季桌面平臺仍然都是14nm,而拖延已久的10nm要到明年才能量產,7nm則是遙遙無期,5nm就更別提了。

-

臺積電

+關注

關注

44文章

5711瀏覽量

167158 -

華為

+關注

關注

216文章

34576瀏覽量

253377 -

AI芯片

+關注

關注

17文章

1918瀏覽量

35295

發(fā)布評論請先 登錄

相關推薦

性能殺手锏!臺積電3nm工藝迭代,新一代手機芯片交戰(zhàn)

總營收超萬億,AI仍是臺積電最強底牌!

臺積電4nm芯片量產

今日看點丨 傳蘋果2025年采用自研Wi-Fi芯片 臺積電7nm制造;富士膠片開始銷售用于半導體EUV光刻的材料

谷歌Tensor G5芯片轉投臺積電3nm與InFO封裝

臺積電產能分化:6/7nm降價應對低利用率,3/5nm漲價因供不應求

今日看點丨消息稱蔚來、小鵬等自研智駕芯片將流片;中國移動超級SIM芯片和MCU芯片采用PUF技術

InspireSemi Thunderbird I 芯片流片,包含 1536 個 RISC-V 核心

華為AI芯片計算密度全球最大 臺積電7nm EUV芯片流片成功

華為AI芯片計算密度全球最大 臺積電7nm EUV芯片流片成功

評論