IC設(shè)計中同步復(fù)位與異步復(fù)位有什么區(qū)別?

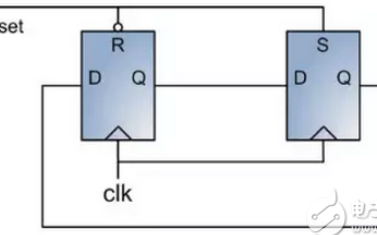

異步復(fù)位是不受時鐘影響的,在一個芯片系統(tǒng)初始化(或者說上電)的時候需要這么一個全局的信號來對整個芯片進(jìn)行整體的復(fù)位,到一個初始的確定狀態(tài)。而同步復(fù)位需要在時鐘沿來臨的時候才會對整個系統(tǒng)進(jìn)行復(fù)位。

-

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1352瀏覽量

105363 -

同步復(fù)位

+關(guān)注

關(guān)注

0文章

27瀏覽量

10850 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13483

原文標(biāo)題:【M博士問答】IC設(shè)計中同步復(fù)位與異步復(fù)位有什么區(qū)別?

文章出處:【微信號:Mouser-Community,微信公眾號:貿(mào)澤電子設(shè)計圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Xilinx FPGA異步復(fù)位同步釋放—同步后的復(fù)位該當(dāng)作同步復(fù)位還是異步復(fù)位?

如何區(qū)分同步復(fù)位和異步復(fù)位?

同步復(fù)位和異步復(fù)位有什么聯(lián)系與區(qū)別,優(yōu)缺點!

如何區(qū)分同步復(fù)位和異步復(fù)位?

Xilinx FPGA的同步復(fù)位和異步復(fù)位

同步復(fù)位和異步復(fù)位的優(yōu)缺點和對比說明

解析IC設(shè)計中同步復(fù)位與異步復(fù)位的差異

解析IC設(shè)計中同步復(fù)位與異步復(fù)位的差異

評論