從模擬及電源出發(fā),系統(tǒng)系列地講解了電路設(shè)計上的基礎(chǔ)知識,從多方面多角度給學(xué)員提供了全面學(xué)習(xí)的機會,也是工程師快速查找相關(guān)基礎(chǔ)知識的便捷手段。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

ti

+關(guān)注

關(guān)注

113文章

8027瀏覽量

214624 -

運算電路

+關(guān)注

關(guān)注

8文章

117瀏覽量

27116 -

設(shè)計

+關(guān)注

關(guān)注

4文章

820瀏覽量

70459

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

電阻器的工作原理與計算方法

散發(fā)出去,從而限制電流的大小。這一過程遵循歐姆定律,即電流I、電壓V和電阻R之間的關(guān)系為:I = V/R。 電阻器的計算方法 電阻器的計算方法有多種,根據(jù)具體需求和已知條件的不同,可以選擇合適的公式進行計算。以下是一些常見的

FPGA門數(shù)的計算方法

我們在比較FPGA的芯片參數(shù)時經(jīng)常說某一款FPGA是多少萬門的,也有的說其有多少個LE,那么二者之間有何關(guān)系呢?

FPGA等效門數(shù)的計算方法有兩種,一是把FPGA基本單元(如LUT+FF

一種新的MLCC陶瓷電容用于電路靜電ESD保護的電容容值計算方法

哦!

原文標(biāo)題:一種新的MLCC陶瓷電容用于電路靜電ESD保護的電容容值計算方法

電荷放大電路的帶寬 和IV轉(zhuǎn)換電路帶寬計算方法不一樣嗎?

,帶寬會非常小,但實際中,電荷放大電路對輸入的陡峭脈沖還是可以完美響應(yīng),這與帶寬非常小矛盾。

電荷放大電路的帶寬 和IV轉(zhuǎn)換電路帶寬計算方法不一樣嗎?

發(fā)表于 09-03 07:07

使用位置傳感器輸出數(shù)據(jù)的角度計算方法

電子發(fā)燒友網(wǎng)站提供《使用位置傳感器輸出數(shù)據(jù)的角度計算方法.pdf》資料免費下載

發(fā)表于 08-30 10:37

?0次下載

包裝泄漏性檢測方法—真空衰減法

包裝容器、電器元件等試樣的無損正、負(fù)壓的微泄漏測試。G精度CCIT測試技術(shù)能夠檢測到微型小孔的泄漏。本產(chǎn)品采用先 進的設(shè)計和嚴(yán)謹(jǐn)、科學(xué)的計算方法確保了其快速測試和高準(zhǔn)確

生物膜的電路中time常數(shù)的計算方法

生物膜的電路中time常數(shù)的計算方法是一個復(fù)雜的問題,涉及到生物物理學(xué)、電化學(xué)和生物信息學(xué)等多個學(xué)科。 Time常數(shù)的概念 Time常數(shù)(τ)是一個描述系統(tǒng)達(dá)到穩(wěn)態(tài)所需的時間的參數(shù)。在電路中

運放減法電路的線性運算方法

領(lǐng)域有著廣泛的應(yīng)用。本文將介紹運放減法電路的線性運算方法。 1. 運放減法電路的基本原理 運放是

運放減法電路電阻怎么算

運放減法電路是一種常見的模擬電路,它利用運算放大器(Operational Amplifier,簡稱Op-Amp)的特性來實現(xiàn)兩個模擬信號的減法

cpu的運算器和控制器的作用是什么

Unit)是CPU中負(fù)責(zé)執(zhí)行算術(shù)和邏輯運算的部分。它的主要作用包括: 1.1 算術(shù)運算:運算器可以執(zhí)行各種算術(shù)運算,如加法、

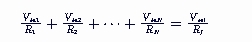

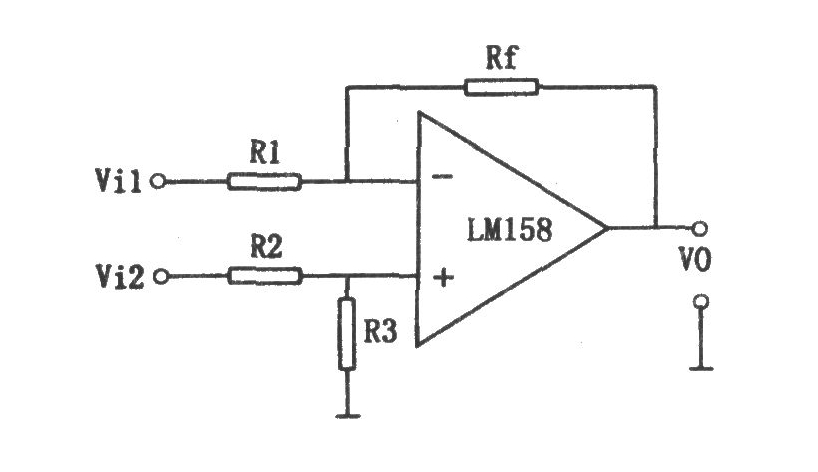

加法和減法運算電路性能特點及值計算方法

加法和減法運算電路性能特點及值計算方法

評論