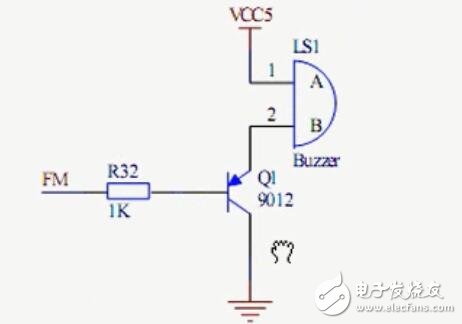

這個(gè)實(shí)驗(yàn)可以說(shuō)是verilog入門最基礎(chǔ)的實(shí)驗(yàn)了,我們不做太多的理論分析,實(shí)踐是硬道理。蜂鳴器與CPLD的接口如圖所示,當(dāng)CPLD的1/0口(FM) 為低電平時(shí),三極管截至,蜂鳴器不發(fā)聲;當(dāng)CPLD的I/0 (FM)為高電平時(shí),三極管導(dǎo)通,蜂鳴器發(fā)聲。

在verilog代碼設(shè)計(jì)中,我們把分頻輸出的信號(hào)clk div與FM管腳對(duì)應(yīng),大家就可以真真切切的感受到什么是分頻了。在代碼里,用了20bit的計(jì)數(shù)器cnt,循環(huán)的計(jì)數(shù),所以說(shuō)一個(gè)周期有2的20次冪即大約1M分頻。因?yàn)橹鲿r(shí)鐘是50MHz(周期是20ns),所以大約20ms為-一個(gè)計(jì)數(shù)周期。蜂鳴器就以大約20ms的周期發(fā)聲,如果大家希望蜂鳴器的發(fā)聲頻率改變,那么可以改變cnt的值看看效果。

更多關(guān)于BJ-EPM240學(xué)習(xí)板之分頻計(jì)數(shù)實(shí)驗(yàn)請(qǐng)看視頻。

-

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2288瀏覽量

96100 -

分頻

+關(guān)注

關(guān)注

0文章

253瀏覽量

25088

發(fā)布評(píng)論請(qǐng)先 登錄

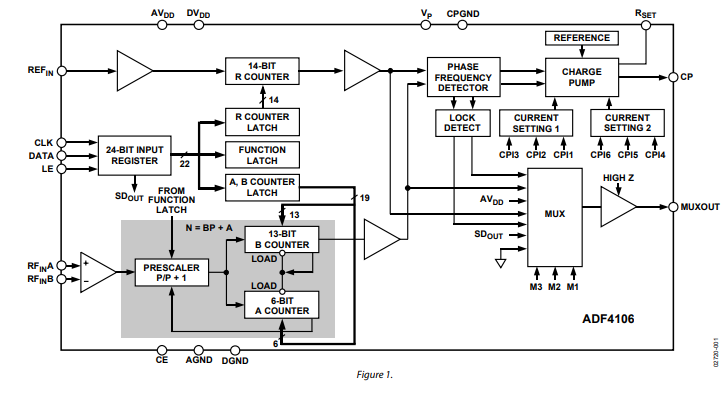

ADF4106 6GHz整數(shù)N分頻PLL技術(shù)手冊(cè)

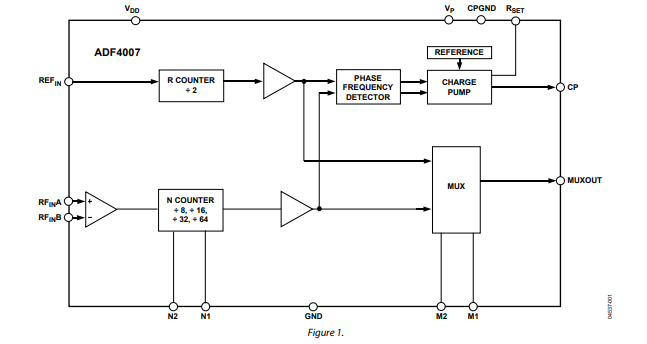

ADF4007高頻分頻器/PLL頻率合成器技術(shù)手冊(cè)

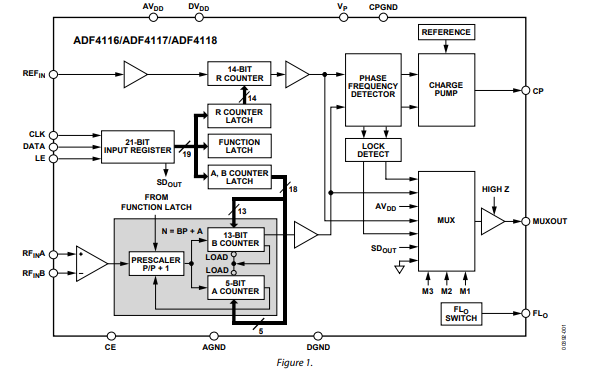

ADF4116/ADF4117/ADF4118單通道、整數(shù)N分頻550MHz PLL技術(shù)手冊(cè)

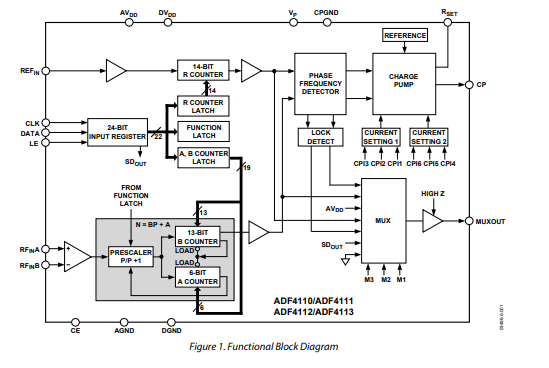

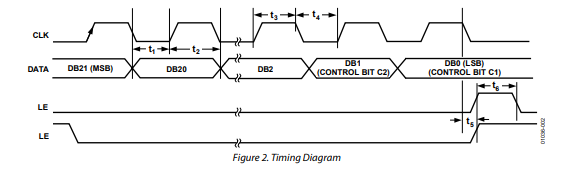

ADF4110/ADF4111/ADF4112/ADF4113單通道、整數(shù)N分頻、550 MHz PLL,內(nèi)置可編程預(yù)分頻器和電荷泵技術(shù)手冊(cè)

ADF4206/ADF4208雙通道、整數(shù)N分頻1.1GHz/2.0 GHz PLL技術(shù)手冊(cè)

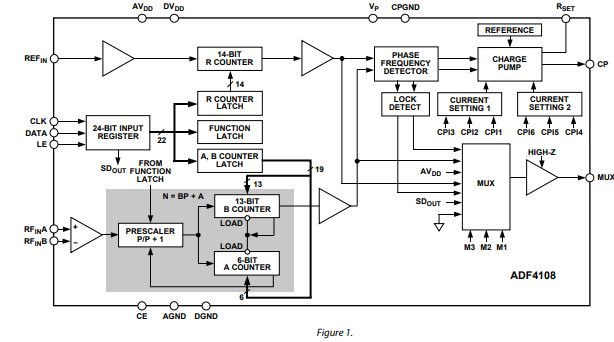

ADF4108 8GHz整數(shù)N分頻PLL技術(shù)手冊(cè)

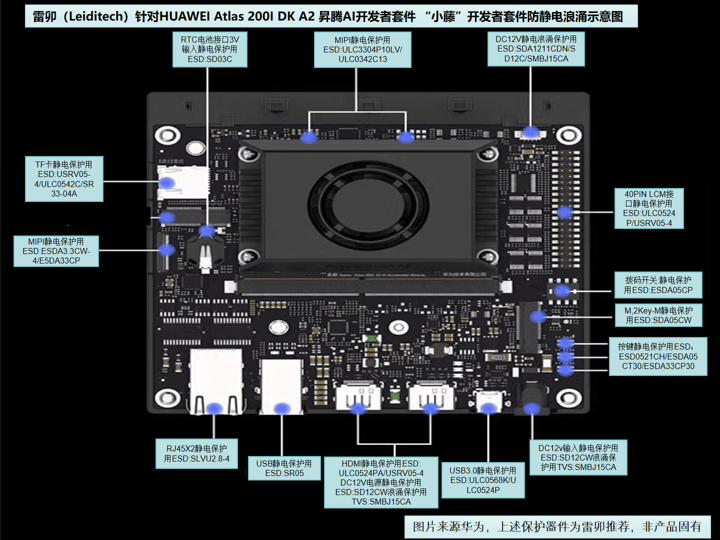

雷卯收集AI實(shí)驗(yàn)課程開(kāi)發(fā)板

深度解析——使用Luatools工具燒錄一個(gè)具體的項(xiàng)目到Air780EPM核心板中!

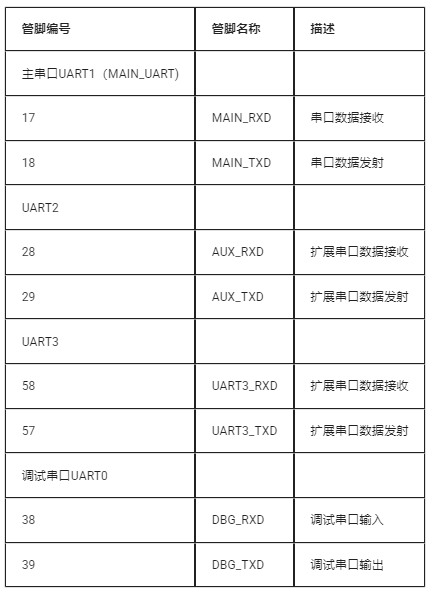

Air780EPM 模塊串口電路設(shè)計(jì)硬件指導(dǎo)

Moku實(shí)現(xiàn)單光子對(duì)符合計(jì)數(shù)實(shí)驗(yàn)指南

74HC4060-Q100;74HCT4060-Q100計(jì)數(shù)器/分頻器和振蕩器規(guī)格書

SmartAmp學(xué)習(xí)板2用戶指南

BJ-EPM240學(xué)習(xí)板之分頻計(jì)數(shù)實(shí)驗(yàn)

BJ-EPM240學(xué)習(xí)板之分頻計(jì)數(shù)實(shí)驗(yàn)

評(píng)論