概述

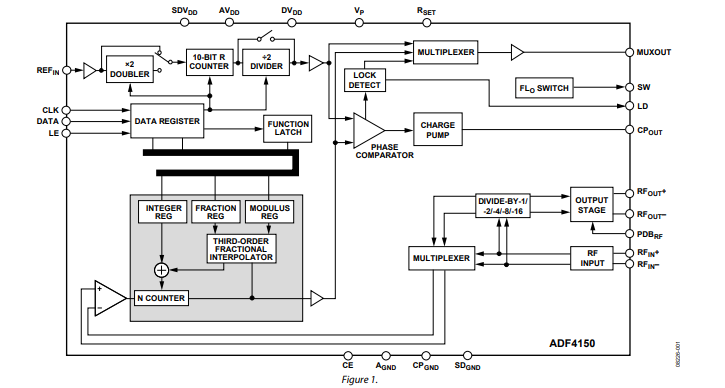

ADF4206/ADF4208均為雙通道頻率合成器,可以用來在無線接收機和發射機的上變頻和下變頻部分實現本振。上述器件由低噪聲數字鑒頻鑒相器(PFD)、精密電荷泵、可編程參考分頻器、可編程A和B計數器以及雙模預分頻器(P/P+1)組成。A(6位)、B(11位)計數器與雙模預分頻器(P/P+1)配合,可實現N分頻器(N = BP+A)。此外,14位參考分頻器(R分頻器)允許PFD輸入端的REFIN 頻率為可選值。如果頻率合成器與外部環路濾波器和電壓控制振蕩器(VCO)一起使用,則可以實現完整的鎖相環(PLL)

數據表:*附件:ADF4206 ADF4208雙通道、整數N分頻1.1GHz 2.0 GHz PLL技術手冊.pdf

特性

- ADF4206: 550 MHz/550 MHz

- ADF4208: 2.0 GHz/1.1 GHz

- 2.7 V至5.5 V電源供電

- 可選的電荷泵電源(V

P)可在3 V系統中提供擴展的調諧電壓 - 可選電荷泵電流

- 片內振蕩器電路

- 可選雙模預分頻器

RF2: 32/33 or 64/65

RF1: 32/33 or 64/65 - 三線式串行接口

- 省電模式

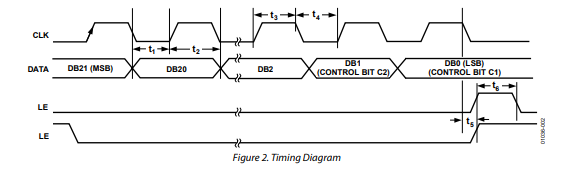

時序圖

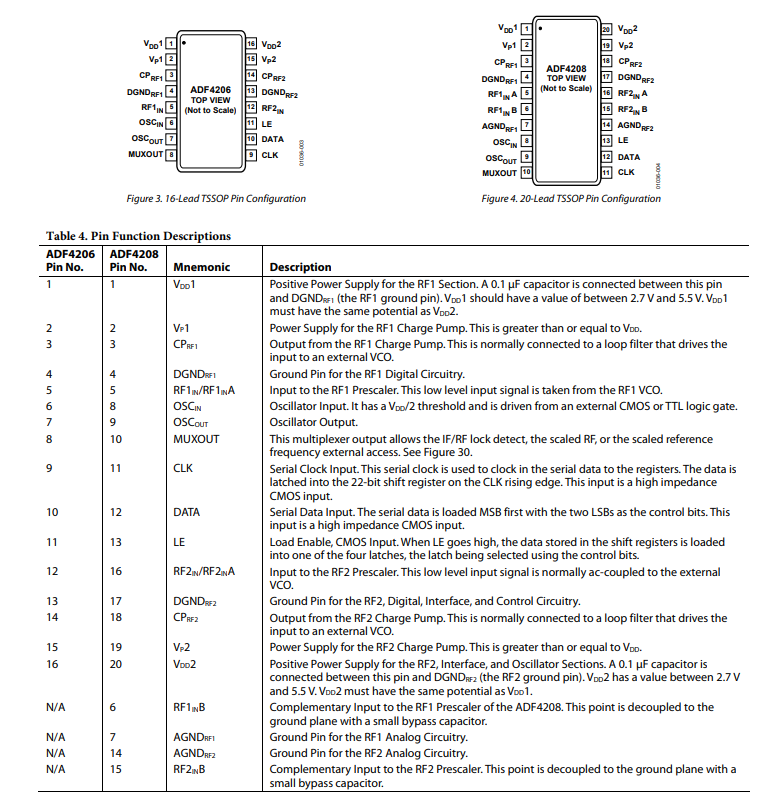

引腳配置描述

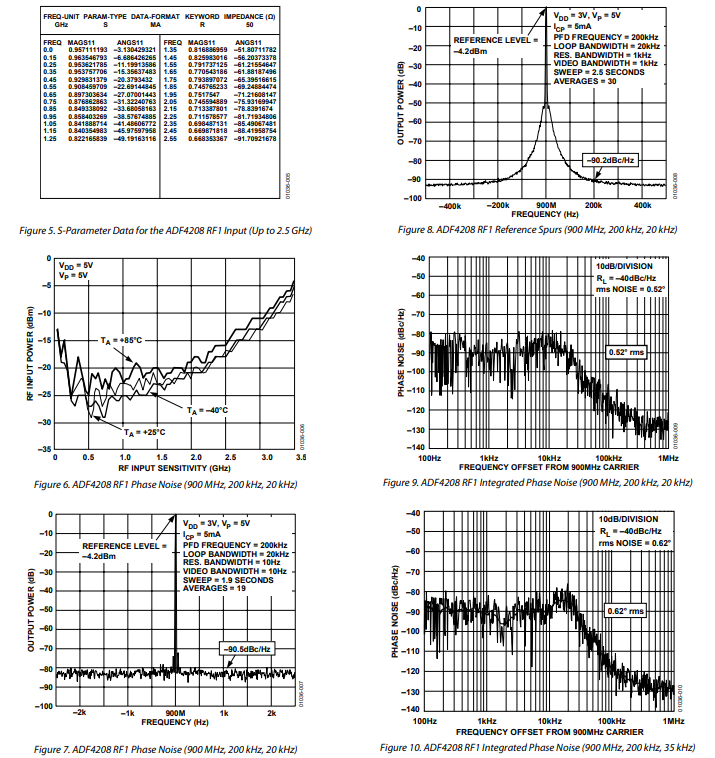

典型性能特征

電路說明

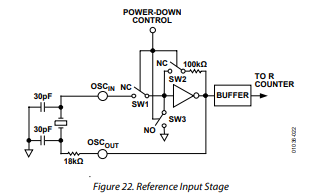

參考輸入部分

參考輸入級如圖22所示。SW1和SW2通常為閉合開關,SW3通常為斷開狀態。當啟動掉電模式時,SW3閉合,SW1和SW2斷開。圖22中顯示了典型的推薦外部組件。

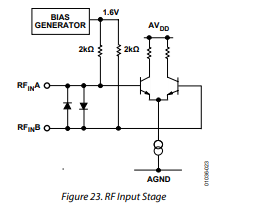

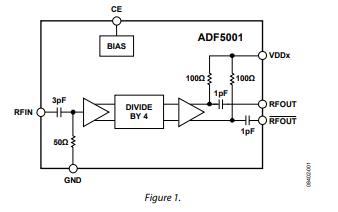

射頻輸入部分

射頻輸入級如圖23所示。其后接一個兩級限幅放大器,以生成預分頻器所需的電流模式邏輯(CML)時鐘電平。

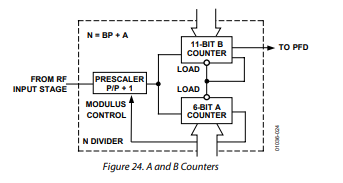

預分頻器

雙模數預分頻器(P/P + 1)與A計數器和B計數器配合,可實現較大的分頻比N((N = BP + A) )。該預分頻器以CML電平工作,從射頻輸入級獲取時鐘信號,并將其分頻到適合CMOS A計數器和B計數器處理的頻率。它基于同步4/5核心。

預分頻器是可選擇的。RF1和RF2都可以設置為32/33或64/65。AB計數器鎖存器的DB20位選擇該值。見圖29和圖31。

A計數器和B計數器

A計數器和B計數器(采用CMOS工藝)與雙模數預分頻器配合,可在鎖相環(PLL)反饋回路中實現較寬范圍的分頻比。當預分頻器的輸出為200 MHz或更低時,這些器件可正常工作。

脈沖吞咽功能

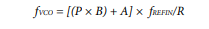

A計數器和B計數器與雙模數預分頻器配合,能夠生成間隔僅為參考頻率除以R的輸出頻率。壓控振蕩器(VCO)頻率的計算公式為:

其中:

- (f_{VCO})是外部壓控振蕩器(VCO)的輸出頻率。

- (P)是雙模數預分頻器的模數(32/33、64/65 )。

- (B)是11位二進制計數器的預設分頻比(2到2047)。

- (A)是6位A計數器的預設分頻比(0到63)。

- (f_{REFIN})是外部參考頻率振蕩器的頻率。

- (R)是14位二進制可編程參考計數器的預設分頻比(1到16,383)。

R計數器

14位R計數器可對輸入參考頻率進行分頻,以產生送往鑒頻鑒相器(PFD)的參考時鐘。允許的分頻比范圍是1到16,383 。

-

頻率合成器

+關注

關注

5文章

295瀏覽量

32730 -

pll

+關注

關注

6文章

887瀏覽量

136121 -

PFD

+關注

關注

0文章

22瀏覽量

14591

發布評論請先 登錄

ADF4208 雙通道、整數N分頻1.1 GHz /2.0 GHz PLL

ADF4106 6 GHz整數N分頻PLL

ADF4216/ADF4217/ADF4218:雙射頻PLL頻率合成器550 MHz/1.2/2.0/2.5 GHz數據表

ADF4210/ADF4211/ADF4212/ADF4213:雙RF/IF PLL頻率合成器1.0 GHz/3 GHz數據表

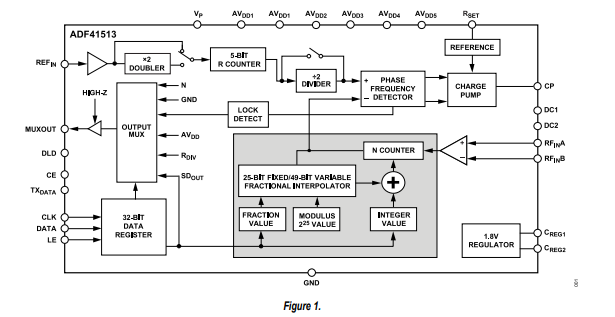

ADF41513 26.5GHz整數N/小數N PLL頻率合成器技術手冊

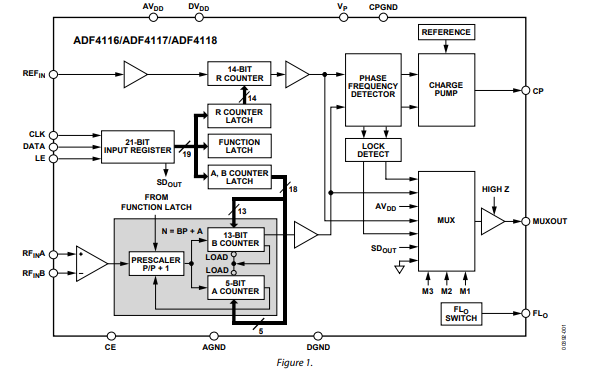

ADF4116/ADF4117/ADF4118單通道、整數N分頻550MHz PLL技術手冊

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

ADF4206/ADF4208雙通道、整數N分頻1.1GHz/2.0 GHz PLL技術手冊

ADF4206/ADF4208雙通道、整數N分頻1.1GHz/2.0 GHz PLL技術手冊

評論