模擬數字轉換器(ADC)設計和架構繼續推進使用更小的幾何工藝節點,新一代GHz ADC產品開始出現。能夠以GHz及以上速率直接進行RF采樣的ADC,沒有交錯偽像,為通信系統,儀器儀表和雷達應用的直接RF數字化系統提供了新的解決方案。以前,這些解決方案需要多級濾波,合成器和混頻器,以將輸入信號轉換為參考頻率,然后可以通過ADC以MSPS轉換速率的100s進行數字化。現在,可以使用最先進的寬帶ADC技術實現直接RF采樣。請記住,速度雖然很重要,但并不是設計中考慮的唯一性能因素。應同等考慮動態范圍和頻譜噪聲。我們將在以后的文章中探討這些性能維度。

不久前,唯一能夠以GSPS(每秒千兆采樣)速度運行的單片ADC架構是具有六位或八位的閃存轉換器決議。由于閃存架構的幾何尺寸和功率約束權衡,它們耗電并且通常不能提供超過7位的有效位數(ENOB)。能夠采樣高于1 GHz的更高動態范圍模擬輸入信號的唯一方法是將多個高速ADC內核與采樣時鐘交錯,采樣時鐘與每個內核具有交錯相位,具有精確的精度或占空比。模擬輸入需要分離并混合到每個ADC,這為新信號噪聲進入信號鏈并降低輸入功率提供了機會。雖然這種方法可以為某些應用提供足夠的結果,但設計很復雜,并且在輸出頻域中產生了令人討厭的,不需要的交錯偽像,需要進行數字濾波。

快速還是半快?

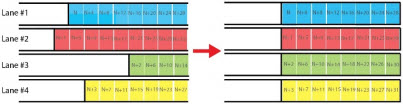

在快速傅立葉變換(FFT)的頻率響應中可以看到交錯“雜散”,其中輸入偏移,增益,帶寬和采樣定時在每個內部交錯ADC內核之間不完全匹配。這為系統工程師創建了額外的規劃復雜性,以預先確定交錯偽像在頻率中的位置,并在數字后處理中避免或消除它們。由于每個ADC內核都是離散的,因此在生產系統的生命周期中,這些性能參數之間可能存在很大的制造不匹配差異的可能性。這些不匹配會導致輸入信號的周期性不平衡,并且在交錯ADC的輸出端會出現寄生頻率。

專有ADC技術現在可以利用先進的架構和算法來防止雙交叉和四交錯ADC中出現的問題。而不是以半速使用兩個交錯的ADC,增加了偽像,現在可以在單個ADC中全速實現性能,而無需交錯雜散。工廠調整算法和片上校準可確保每個ADC均符合預期的高性能標準,而不是暴露于多個離散交錯核心的不匹配差異。

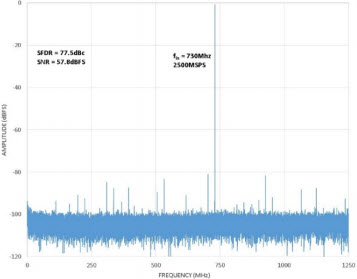

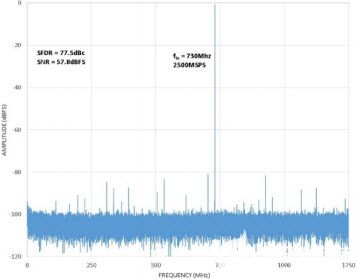

當觀察到雜散頻率時否則,光譜純FFT,這減少了載波信號相對于其他噪聲的可用無雜散動態范圍(SFDR)。為了改善GSPS ADC的SFDR,新的架構和算法現在已經超越了交錯核心的使用范圍。這消除了系統工程師負擔必須識別和刪除不需要的交錯雜散的專用ADC后處理例程的負擔。

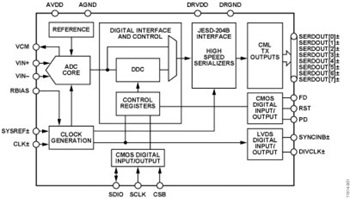

AD9625-2.5 12位,2.5 ADI公司的GSPS ADC在寬帶寬范圍內提供優于-75 dBC的SFDR性能,噪聲頻譜密度為150 dBFS / Hz。專有的ADI技術可實現此性能,而不會出現通常在采樣高于1.5 GSPS的GHz ADC時出現的交錯偽像。具有寬帶頻率調諧器的可選雙抽取下變頻濾波器路徑允許系統設計人員僅觀察1/8或1/16的全頻譜帶寬,每個帶寬均具有獨立的10位NCO放置分辨率。 AD9625使用多達8個JESD204B輸出接口通道,因此無需采用具有挑戰性的匹配走線布局布局,這是典型的LVDS對。此外,設計人員可以利用JESD204B的優勢,例如低引腳數輸出,諧波幀時鐘,每個采樣的控制位信息以及確定性延遲。

總之,GHz ADC產品和系統的發展趨勢部分是由較小的幾何工藝節點推動的,這些節點在未來十年內只會減小尺寸。這將產生對能夠進行直接RF轉換的更多ADC的需求,因此可以簡化架構并將設計時間包含在合理的限制內。正是這種速度,簡化設計以及動態范圍和低噪聲等其他性能因素的結合,將先進的寬帶ADC技術推向了新的水平,甚至超越了它。

-

adc

+關注

關注

99文章

6686瀏覽量

549026

發布評論請先 登錄

新技術需要新的測試手段

Ultra320 SCSI:新技術的SCSI

急急急!!大神進來看看,幫我設計一個振動信號文件通過快速傅里葉變換分析其頻域的后面板!!

手機的新技術盤點

通過節省時間和成本的創新技術降 低電源中的EMI

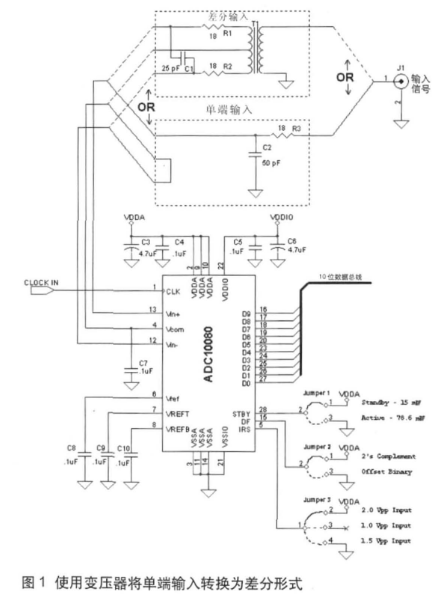

高速ADC輸入信號接口的挑戰與不同技術的需求

X射線衍射技術可以通過快速加載或卸載抑制熱驅動的晶體到晶體相變

千兆采樣ADC快速運行以解決新挑戰

adc最新技術趨勢與發展

【Simcenter STAR-CCM+】通過快速準確的CFD仿真加速空氣動力學創新

最新技術Gigasample ADC通過快速運行以解決新的挑戰

最新技術Gigasample ADC通過快速運行以解決新的挑戰

評論