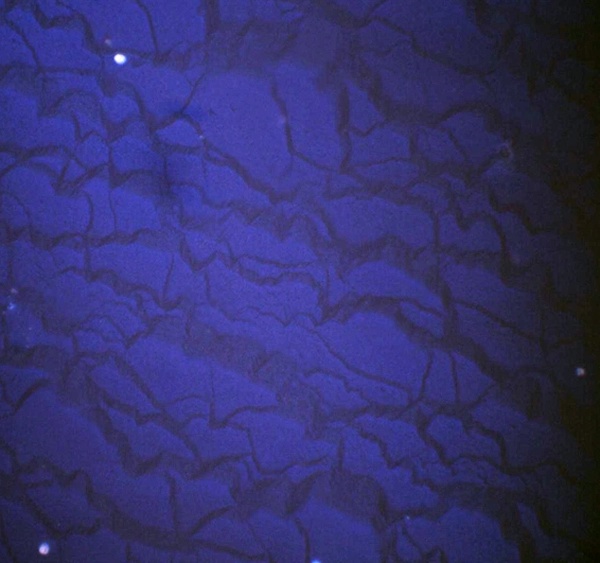

圖1.多晶硅太陽能電池的顯微鏡光學(xué)圖像。在此圖像上可以觀察到大塊的熔融和凝固的硅。 可再生能源,例如太陽能,預(yù)計將在不久的將來發(fā)揮重要作用。為了將太陽光的能量直接轉(zhuǎn)化為電能,硅太陽能電池(晶體或

![的頭像]() 發(fā)表于

發(fā)表于 05-26 08:28

?78次閱讀

本文介紹了在多晶硅鑄造工藝中碳和氮雜質(zhì)的來源、分布、存在形式以及降低雜質(zhì)的方法。

![的頭像]() 發(fā)表于

發(fā)表于 04-15 10:27

?347次閱讀

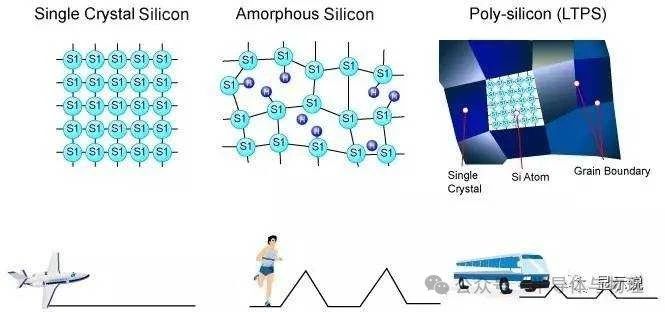

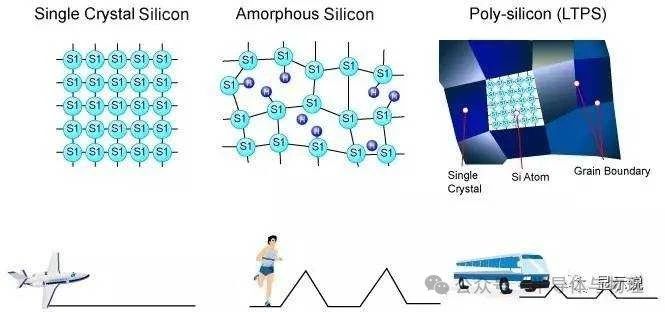

本文圍繞單晶硅、多晶硅與非晶硅三種形態(tài)的結(jié)構(gòu)特征、沉積技術(shù)及其工藝參數(shù)展開介紹,重點解析LPCVD方法在多晶硅制備中的優(yōu)勢與挑戰(zhàn),并結(jié)合不同工藝條件對材料性能的影響,幫助讀者深入理解

![的頭像]() 發(fā)表于

發(fā)表于 04-09 16:19

?604次閱讀

多晶硅(Polycrystalline Silicon,簡稱Poly)是由無數(shù)微小硅晶粒組成的非單晶硅材料。與單晶硅(如硅襯底)不同,

![的頭像]() 發(fā)表于

發(fā)表于 04-08 15:53

?822次閱讀

本文介紹了多晶硅作為晶體管的柵極摻雜的原理和必要性。

![的頭像]() 發(fā)表于

發(fā)表于 04-02 09:22

?576次閱讀

鑄錠澆注法是較早出現(xiàn)的一種技術(shù),該方法先將硅料置于熔煉坩堝中加熱熔化,隨后利用翻轉(zhuǎn)機械將其注入模具內(nèi)結(jié)晶凝固,最初主要用于生產(chǎn)等軸多晶硅。近年來,為提升多晶硅電池轉(zhuǎn)換效率,通過控制模具中熔體凝固過程的溫度,創(chuàng)造定向散熱條件,從而

![的頭像]() 發(fā)表于

發(fā)表于 03-13 14:41

?436次閱讀

本文介紹了單晶圓系統(tǒng):多晶硅與氮化硅的沉積。 在半導(dǎo)體制造領(lǐng)域,單晶圓系統(tǒng)展現(xiàn)出獨特的工藝優(yōu)勢,它具備進行多晶硅沉積的能力。這種沉積方式所帶來的顯著益處之一,便是能夠?qū)崿F(xiàn)臨場的多晶硅和鎢硅化物沉積

![的頭像]() 發(fā)表于

發(fā)表于 02-11 09:19

?451次閱讀

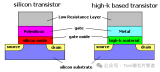

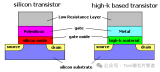

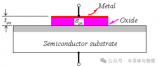

本文解釋了為什么采用多晶硅作為柵極材料 ? 柵極材料的變化 ? 如上圖,gate就是柵極,柵極由最開始的鋁柵,到多晶硅柵,再到HKMG工藝中的金屬柵極。 ? 柵極的作用 ? 柵極的主要作用是控制

![的頭像]() 發(fā)表于

發(fā)表于 02-08 11:22

?564次閱讀

在全球積極推動清潔能源轉(zhuǎn)型的大背景下,太陽能光伏產(chǎn)業(yè)蓬勃發(fā)展,而多晶硅作為光伏產(chǎn)業(yè)鏈的關(guān)鍵起始原料,其質(zhì)量和性能直接關(guān)系到整個光伏系統(tǒng)的發(fā)電效率和穩(wěn)定性。因此,了解并嚴(yán)格把控多晶硅的存儲條件顯得尤為重要。

![的頭像]() 發(fā)表于

發(fā)表于 12-27 09:22

?719次閱讀

1. 美國宣布提高中國太陽能硅片、多晶硅關(guān)稅至50% 2025 年1 月1 日生效 ? 美國拜登政府周三(12月11日)宣布,將增加對中國太陽能硅片和多晶硅、鎢產(chǎn)品的進口關(guān)稅,作為其保護本國清潔

發(fā)表于 12-12 10:09

?903次閱讀

? ? ? ?多晶硅還原爐內(nèi),硅芯起著至關(guān)重要的作用。?? 在多晶硅的生長過程中,硅芯的表面會逐漸被新沉積的硅層所覆蓋,形成

![的頭像]() 發(fā)表于

發(fā)表于 11-14 11:27

?748次閱讀

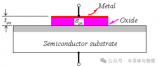

與亞微米工藝類似,多晶硅柵工藝是指形成 MOS器件的多晶硅柵極,柵極的作用是控制器件的關(guān)閉或者導(dǎo)通。淀積的多晶硅是未摻雜的,它是通過后續(xù)的源漏離子注入進行摻雜,PMOS 的柵是p型摻雜,NMOS 的柵是n型摻雜。

![的頭像]() 發(fā)表于

發(fā)表于 11-07 08:58

?1464次閱讀

光伏多晶硅是太陽能光伏產(chǎn)業(yè)中的關(guān)鍵材料,它在太陽能電池的生產(chǎn)中扮演著重要角色。多晶硅太陽能電池因其成本相對較低、制造工藝成熟、穩(wěn)定性好等特點,在光伏市場中占有重要地位。 1. 住宅和商業(yè)建筑 1.1

![的頭像]() 發(fā)表于

發(fā)表于 09-20 11:33

?1171次閱讀

光伏多晶硅是一種用于制造太陽能電池的材料,其分片過程是將整塊的多晶硅切割成適合制造太陽能電池的小塊。這個過程對于提高太陽能電池的效率和降低成本至關(guān)重要。以下是一篇關(guān)于光伏多晶硅分片方法及其優(yōu)缺點

![的頭像]() 發(fā)表于

發(fā)表于 09-20 11:26

?987次閱讀

當(dāng)柵與襯底之間存在壓差時,它們之間存在電場,靜電邊界條件使多晶硅靠近氧化層界面附近的能帶發(fā)生彎曲,并且電荷耗盡,從而形成多晶硅柵耗盡區(qū)。該耗盡區(qū)會在多晶硅柵與柵氧化層之間產(chǎn)生一個額外的串聯(lián)電容。當(dāng)柵氧化層厚度減小到 2nm 以下

![的頭像]() 發(fā)表于

發(fā)表于 08-02 09:14

?5092次閱讀

多晶硅原料是什么

多晶硅原料是什么

評論