隨著SystemVerilog成為IEEE的P1800規(guī)范,越來越多的項目開始采用基于SystemVerilog的驗證方法學(xué)來獲得更多的重用擴展性、更全面的功能覆蓋率,以及更合理的層次化驗證結(jié)構(gòu)

2014-03-24 14:07:47 2929

2929 SystemVerilog中多態(tài)能夠工作的前提是父類中的方法被聲明為virtual的。

2022-11-28 11:12:42 466

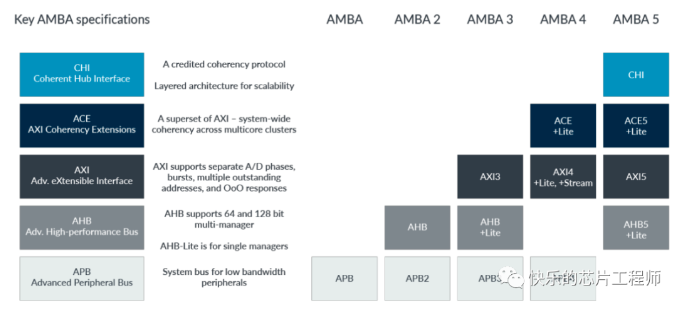

466 作為一名新時代的ICer,一定必定肯定聽說過AMBA協(xié)議,但是卻少有人知道AMBA協(xié)議的evolution過程,本文將大致聊聊Evolution of the ARM AMBA Specifications!

2024-01-19 09:50:02 460

460

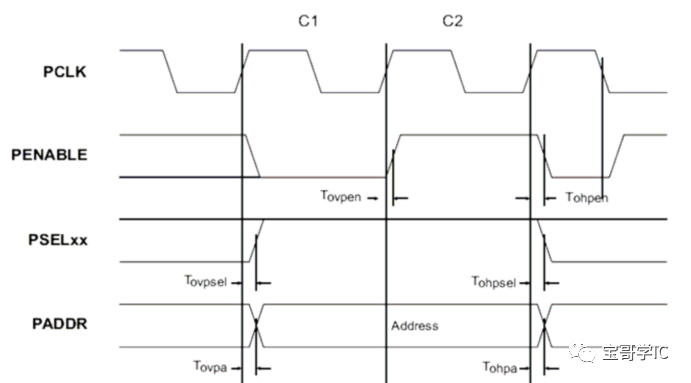

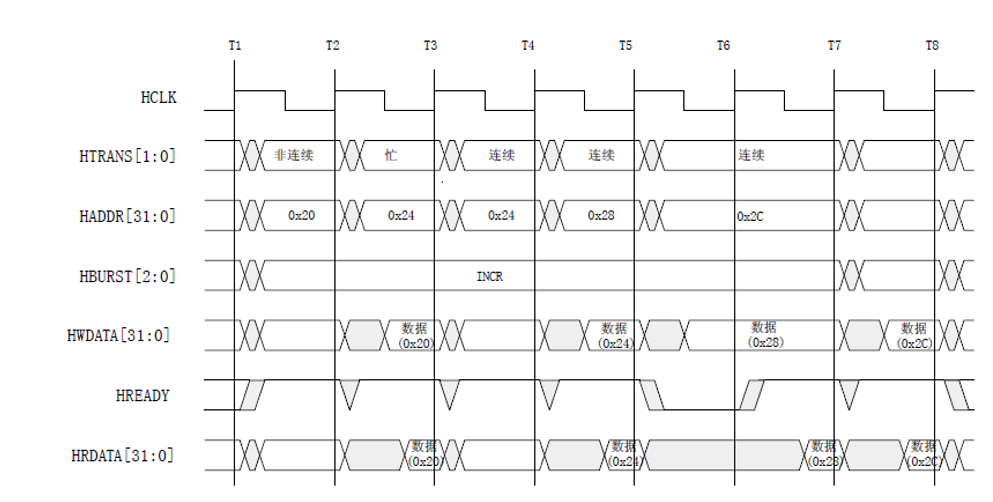

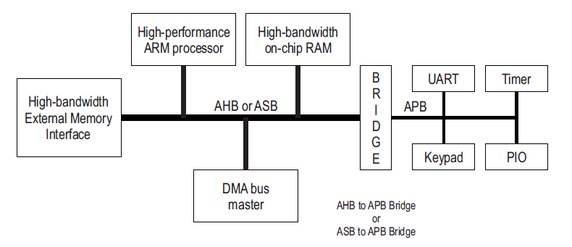

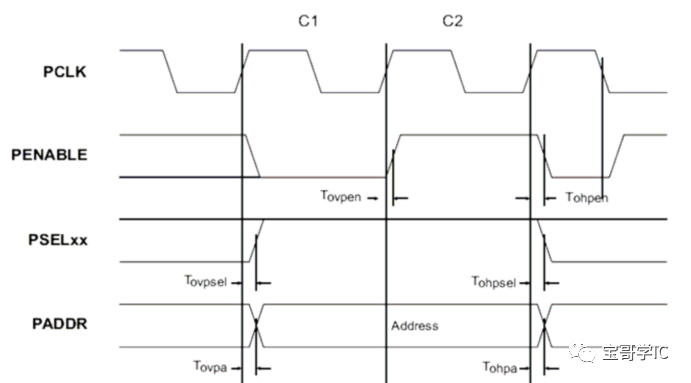

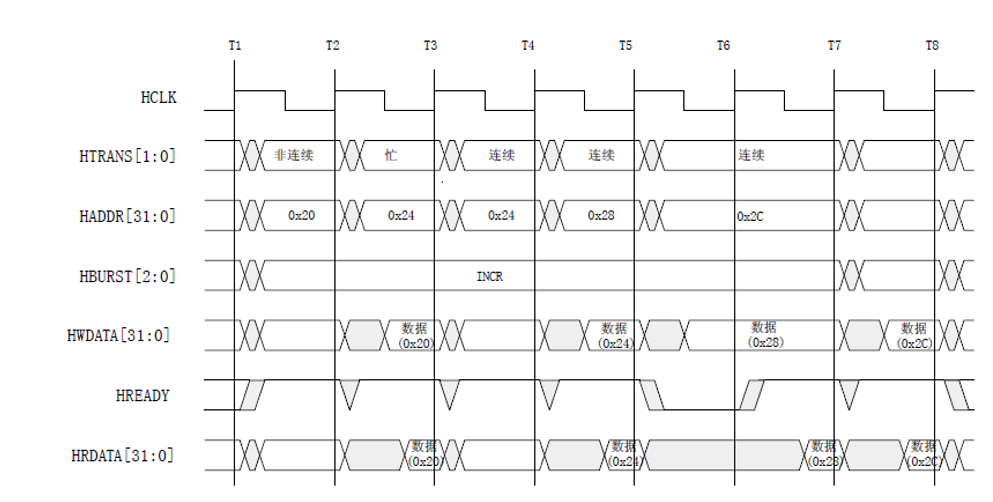

使用的是 SystemVerilog 描述。2、AMBA APB總線信號接口介紹前面分析了AHB總線協(xié)議。接下來分析APB總線協(xié)議。 PCLK APB總線時鐘。 PRESETn APB總線復(fù)位。低

2022-04-07 10:03:19

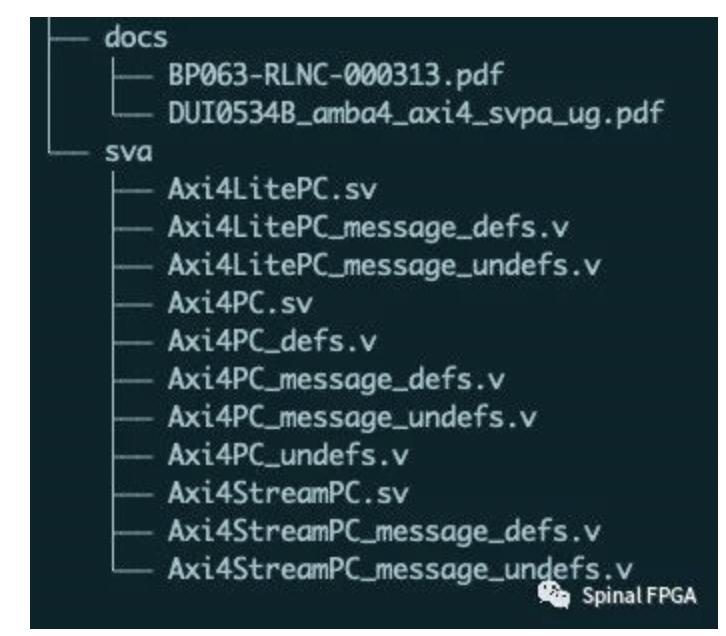

本書是為系統(tǒng)設(shè)計者、系統(tǒng)集成商和驗證工程師編寫的,他們希望確認設(shè)計符合相關(guān)AMBA4協(xié)議。這可以是ACE或ACE Lite

2023-08-10 07:01:12

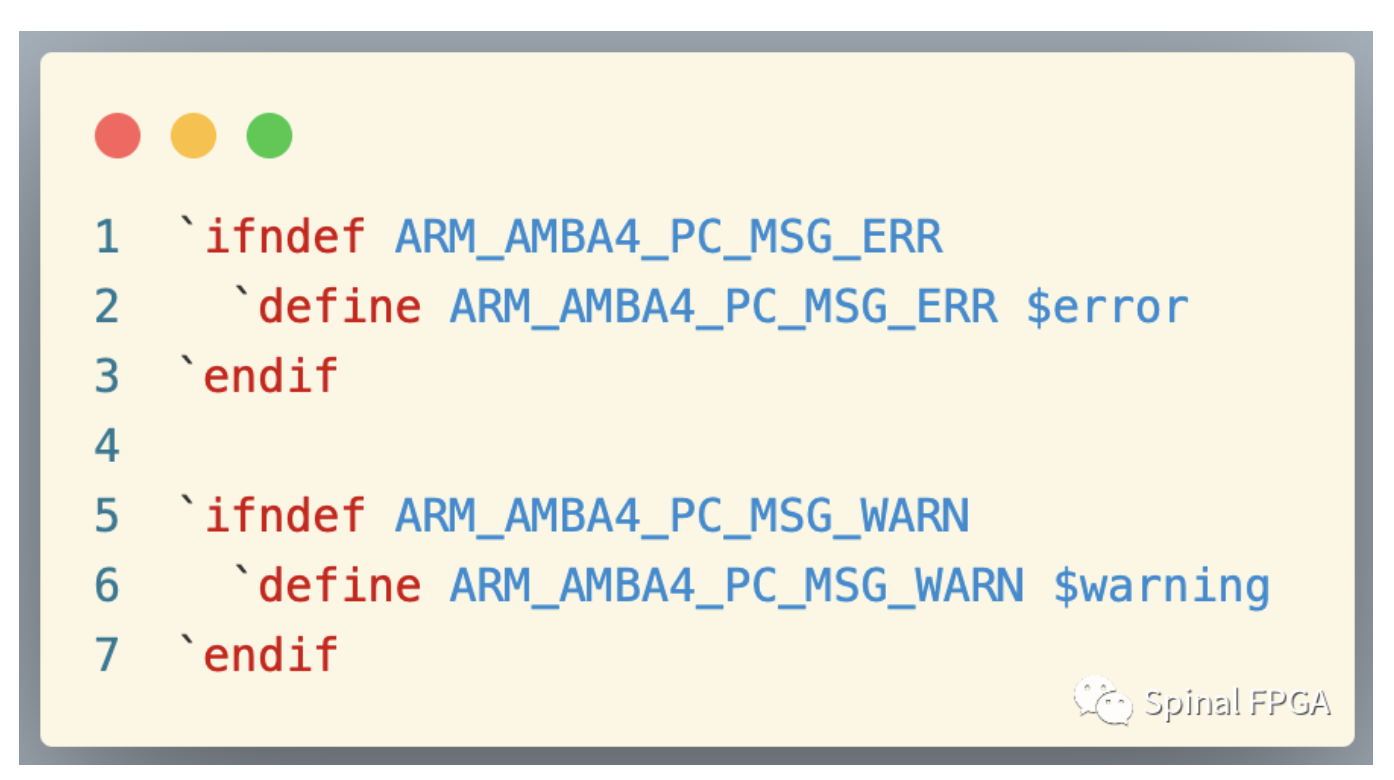

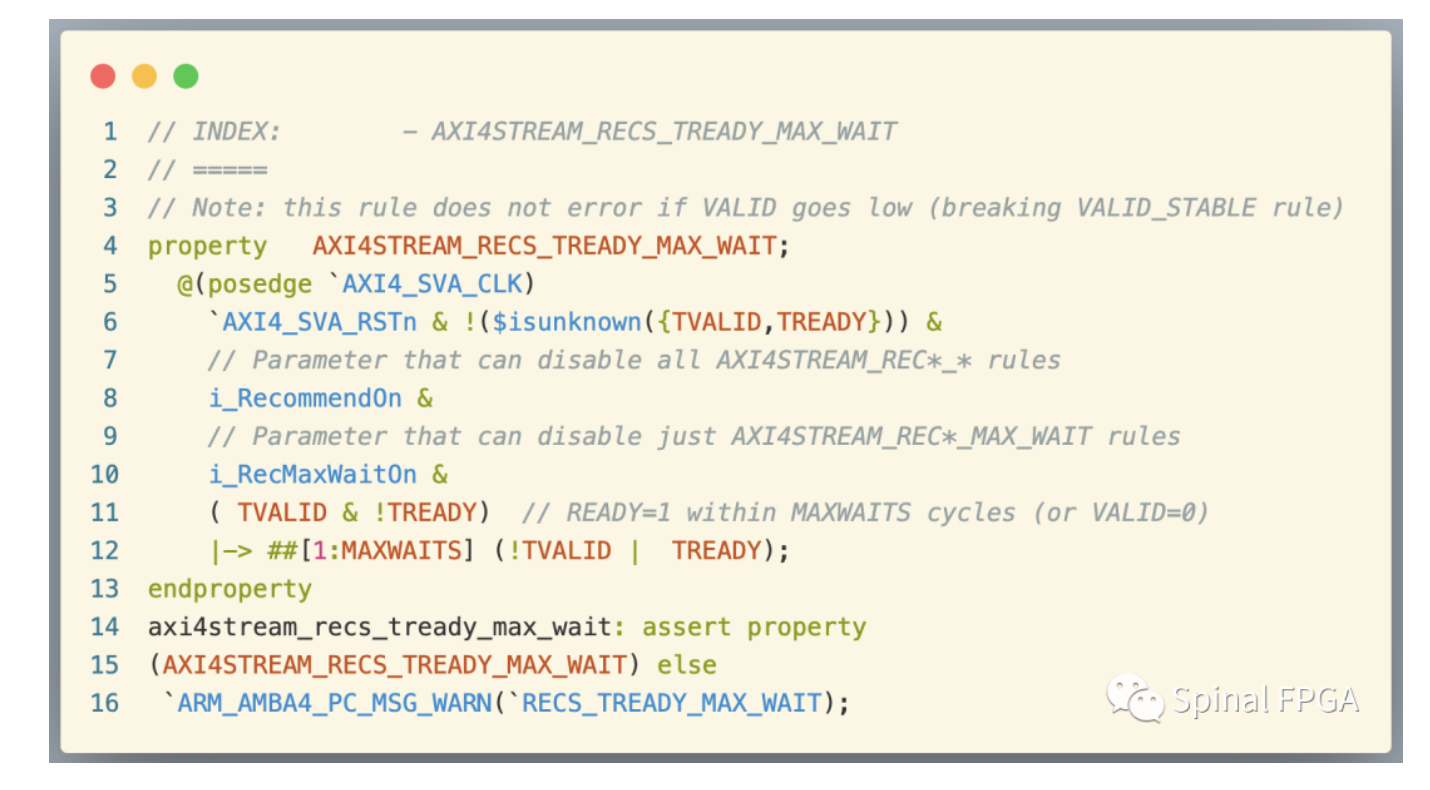

您可以將協(xié)議斷言與任何旨在實現(xiàn)AMBA?4 AXI4的接口一起使用?, AXI4 Lite?, 或AXI4流? 協(xié)議通過一系列斷言根據(jù)協(xié)議檢查測試接口的行為。

本指南介紹SystemVerilog

2023-08-10 06:39:57

本規(guī)范描述了AMBA ATB協(xié)議。本規(guī)范中對ATB的所有引用均指AMBA ATB。本文件中的信息取代CoreSight體系結(jié)構(gòu)規(guī)范中的ATB信息

2023-08-11 07:39:54

STM32 CubeIDE(五)AMBA與時鐘樹AMBAAMBA(Advanced Microprocessor Bus Architecture)是ARM公司提出的一種開放性的SoC總線標準,廣泛

2021-08-12 06:19:21

AMBAAMBA(Advanced Microprocessor Bus Architecture)是ARM公司提出的一種開放性的SoC總線標準,現(xiàn)在已經(jīng)廣泛的應(yīng)用于RISC的內(nèi)核上了。 AMBA

2021-08-05 08:16:29

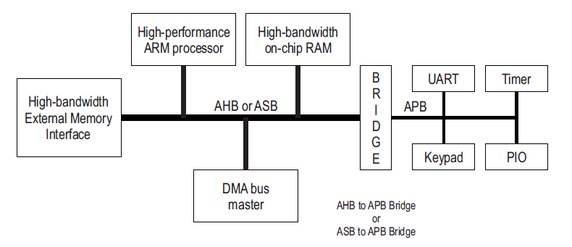

AMBA規(guī)范描述了一種用于設(shè)計高性能16和32位微控制器、信號處理器和復(fù)雜外圍設(shè)備的片上通信標準。

AMBA已在中得到驗證,并正在設(shè)計為:

?PDA微控制器,具有大量集成外圍設(shè)備,但功耗非常低?具有

2023-08-10 07:17:40

SystemVerilog 的VMM 驗證方法學(xué)教程教材包含大量經(jīng)典的VMM源代碼,可以實際操作練習(xí)的例子,更是ic從業(yè)人員的絕佳學(xué)習(xí)資料。SystemVerilog 的VMM 驗證方法學(xué)教程教材[hide][/hide]

2012-01-11 11:21:38

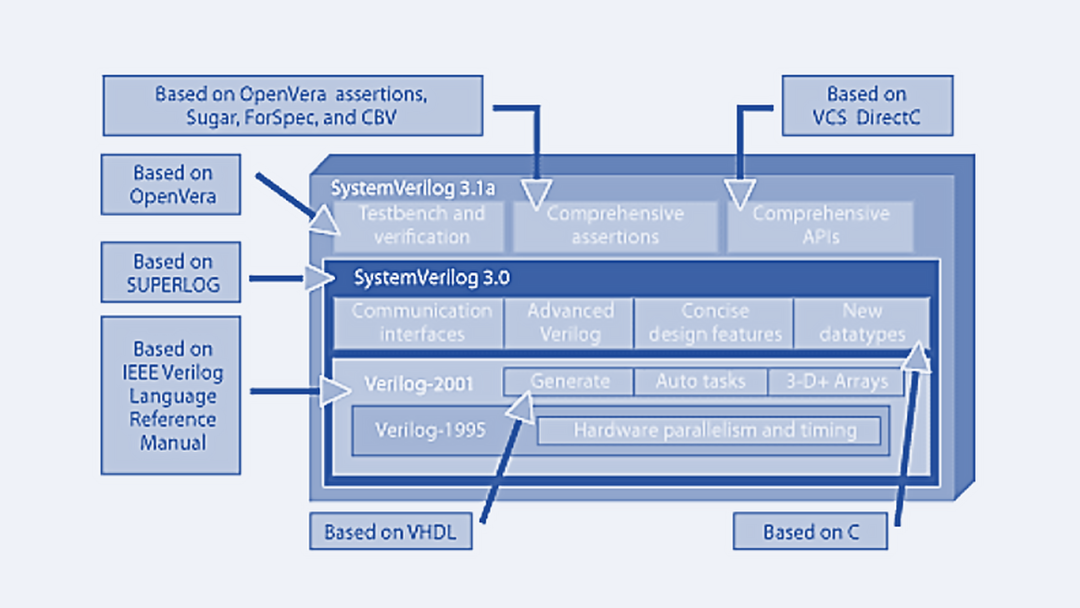

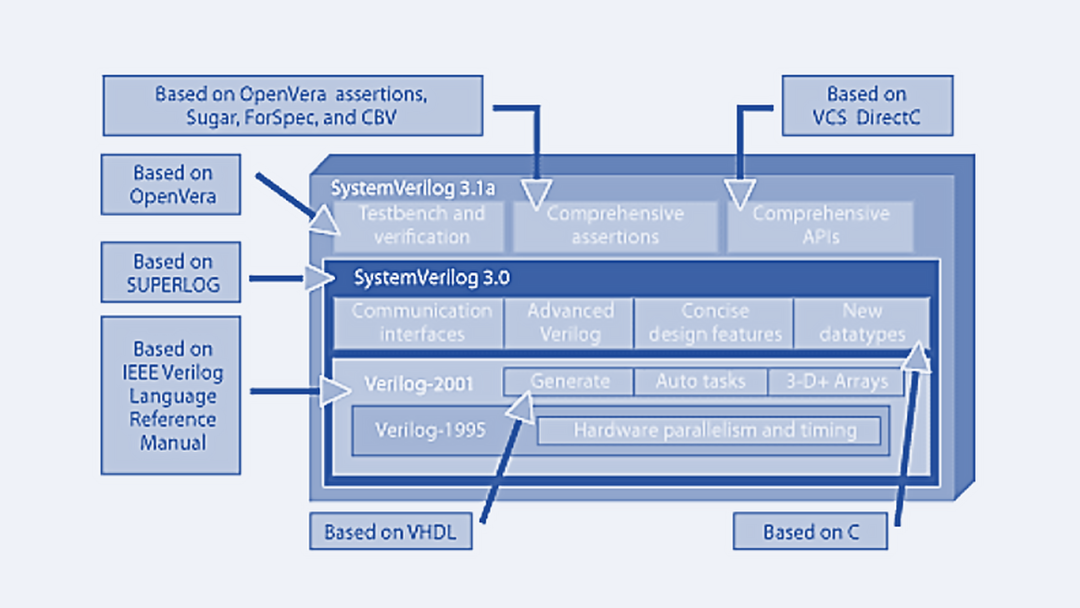

SystemVerilog有哪些標準?

2021-06-21 08:09:41

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發(fā)展的朋友。QQ群374590107歡迎有志于FPGA開發(fā),IC設(shè)計的朋友加入一起交流。一起為中國的IC加油!!!

2014-06-02 09:47:23

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發(fā)展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本語法以及和verilog語言之間的區(qū)別。

2015-04-01 14:24:14

)(SystemVerilog) 通用驗證方法 (UVM) 是一種用于驗證集成電路設(shè)計的標準化方法。 UVM 主要源自 OVM(OpenVerification Methodology),它在很大程度

2022-02-13 17:03:49

AMBA Designer生成跨平臺兼容的配置,并可以生成RTL Verilog文件和相關(guān)的開箱即用(OOB)測試臺,用于驗證RTL。

在AMBA Designer Canvas中,您可以配置IP

2023-08-10 06:49:48

ARM AMBA協(xié)議集中,GIC的版本和amba版本有對應(yīng)要求嗎?

2022-10-31 15:28:30

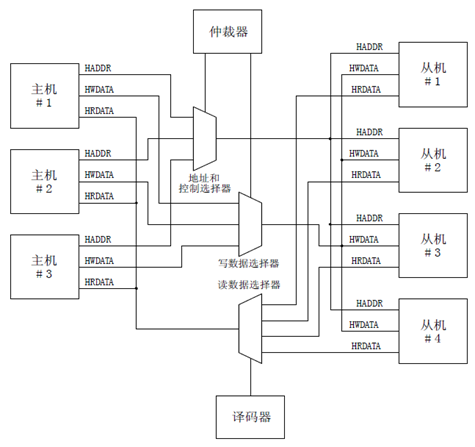

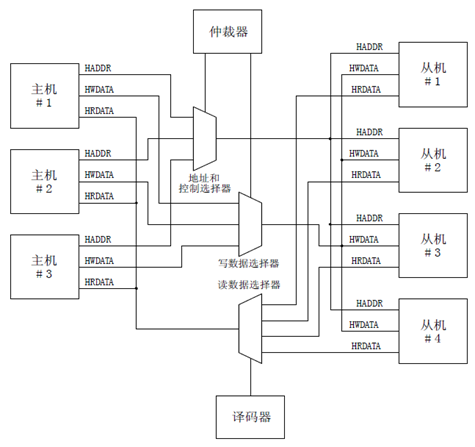

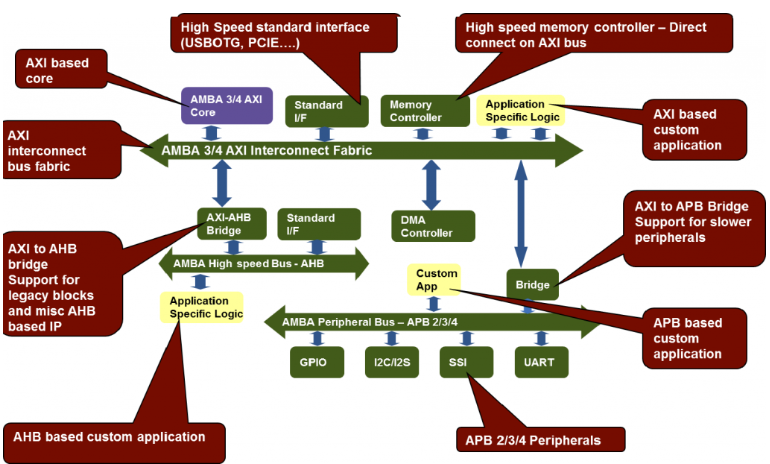

, ASB, APB);Qchannel文章目錄1 AMBA總線2 AHB2.1 一個典型的基于AHB的微控制器2.2 AHB總線互聯(lián)結(jié)構(gòu):中心選擇器連接master與slave2.3 AHB的特性3 APB4 AHB和APB的區(qū)別與聯(lián)系4 Q-channel1 AMBA總線內(nèi)容來源:維基百科詞條-Ad.

2022-02-09 07:46:07

Arm AMBA協(xié)議集中,GIC的版本和amba版本有對應(yīng)要求嗎?

2022-09-30 10:52:27

本文檔旨在提供關(guān)于將PCIe接口集成到基于AMBA的片上系統(tǒng)(SoC)的指導(dǎo)。

假設(shè)PCIe接口通過基于AXI或ACE協(xié)議的互連連接到SoC的其余部分。

讀者應(yīng)熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

這是SoC Designer AXI4協(xié)議包的用戶指南。該協(xié)議包包含SoC Designer組件、探針和ARM AXI4協(xié)議的事務(wù)端口接口(包括對AMBA4 AXI的支持)。

2023-08-10 06:30:18

學(xué)快速發(fā)展,這些趨勢你了解嗎?SystemVerilog + VM是目前的主流,在未來也將被大量采用,這些語言和方法學(xué),你熟練掌握了嗎?對SoC芯片設(shè)計驗證感興趣的朋友,可以關(guān)注啟芯工作室推出的SoC芯片

2013-06-10 09:25:55

大家好,我對一個 round robin 的 systemverilog 代碼有疑惑。https://www.edaplayground.com/x/2TzD代碼第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

,本科5年數(shù)字芯片驗證工程師崗位要求:1、熟悉systemverilog 語言,熟練掌握UVM/VMM/OVM驗證方法學(xué),獨立完成過中等規(guī)模以上模塊的驗證開發(fā)2、熟悉數(shù)字芯片驗證流程,三年以上相關(guān)工作經(jīng)驗3、碩士3年,本科5年聯(lián)系方式:ucollide@163.com一八五八3907八零五

2018-03-13 09:27:17

本文我們簡單對AMBA4中的APBv2.0(也稱為APB4),以及AMBA3AHB-Litev1.0進行簡單的了解。

2021-04-02 06:30:03

FPGA工程師們應(yīng)該都會吐槽Verilog的語法,相當?shù)牟挥押茫绕涫菍τ谟泻芏嘟涌诘哪K,像AXI4/AXI-Lite這種常用的總線接口,動不動就好幾十根線,寫起來是相當費勁。 ??當然現(xiàn)在

2021-01-08 17:23:22

在某大型科技公司的招聘網(wǎng)站上看到招聘邏輯硬件工程師需要掌握SystemVerilog語言,感覺SystemVerilog語言是用于ASIC驗證的,那么做FPGA工程師有沒有必要掌握SystemVerilog語言呢?

2017-08-02 20:30:21

Arm AMBA協(xié)議集中,LPI 在AMBA4 出現(xiàn),協(xié)議和鏈路層 與 AXI/AHB 無關(guān) 獨立的嗎? AHB-lite 可否使用?

2022-09-08 11:35:56

Systemverilog [1]和 UVM [2]為驗證團隊提供結(jié)構(gòu)和規(guī)則。它使得在許多測試中能獲得一致的結(jié)果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規(guī)UVM測試平臺的各種方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]為驗證團隊提供結(jié)構(gòu)和規(guī)則。它使得在許多測試中能獲得一致的結(jié)果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規(guī)UVM測試平臺的各種方法。

2020-12-15 07:38:34

,設(shè)計不斷地重用,而驗證也希望能夠重用一樣的驗證模塊,這就催生了層次化的驗證方法。Synopsys的VMM驗證方法學(xué)提供了基于SystemVerilog的驗證方法,包括了有約束的隨機數(shù)生成,層次化

2019-07-03 07:40:26

,設(shè)計不斷地重用,而驗證也希望能夠重用一樣的驗證模塊,這就催生了層次化的驗證方法。Synopsys的 VMM驗證方法學(xué)提供了基于SystemVerilog的驗證方法,包括了有約束的隨機數(shù)生成,層次化

2019-07-01 08:15:47

SystemC和SystemVerilog在設(shè)計中的地位問題,我認為在驗證方面,SystemC有明顯的優(yōu)勢。如果你設(shè)計純粹的ASIC,那么用SystemVerilog可能就足夠了。但是在很多場合,軟硬件同時存在

2012-03-01 11:30:19

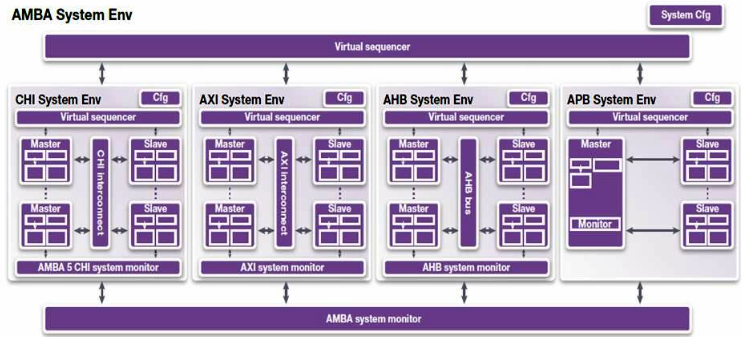

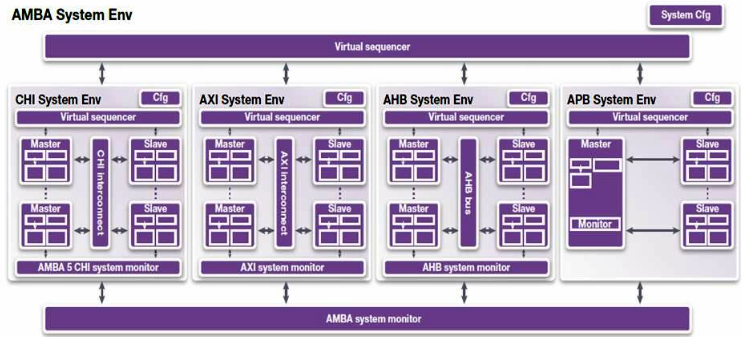

如何用配置類svt_amba_system_configuration來控制AMBA System Env?

2022-02-11 06:41:48

本文通過對ISO/IEC 7816-3傳輸協(xié)議的分析,基于AMBA總線架構(gòu),提出一款智能卡設(shè)計方案,通過FPGA驗證并采用SMIC 0.18μm工藝流片成功。

2021-05-07 06:10:12

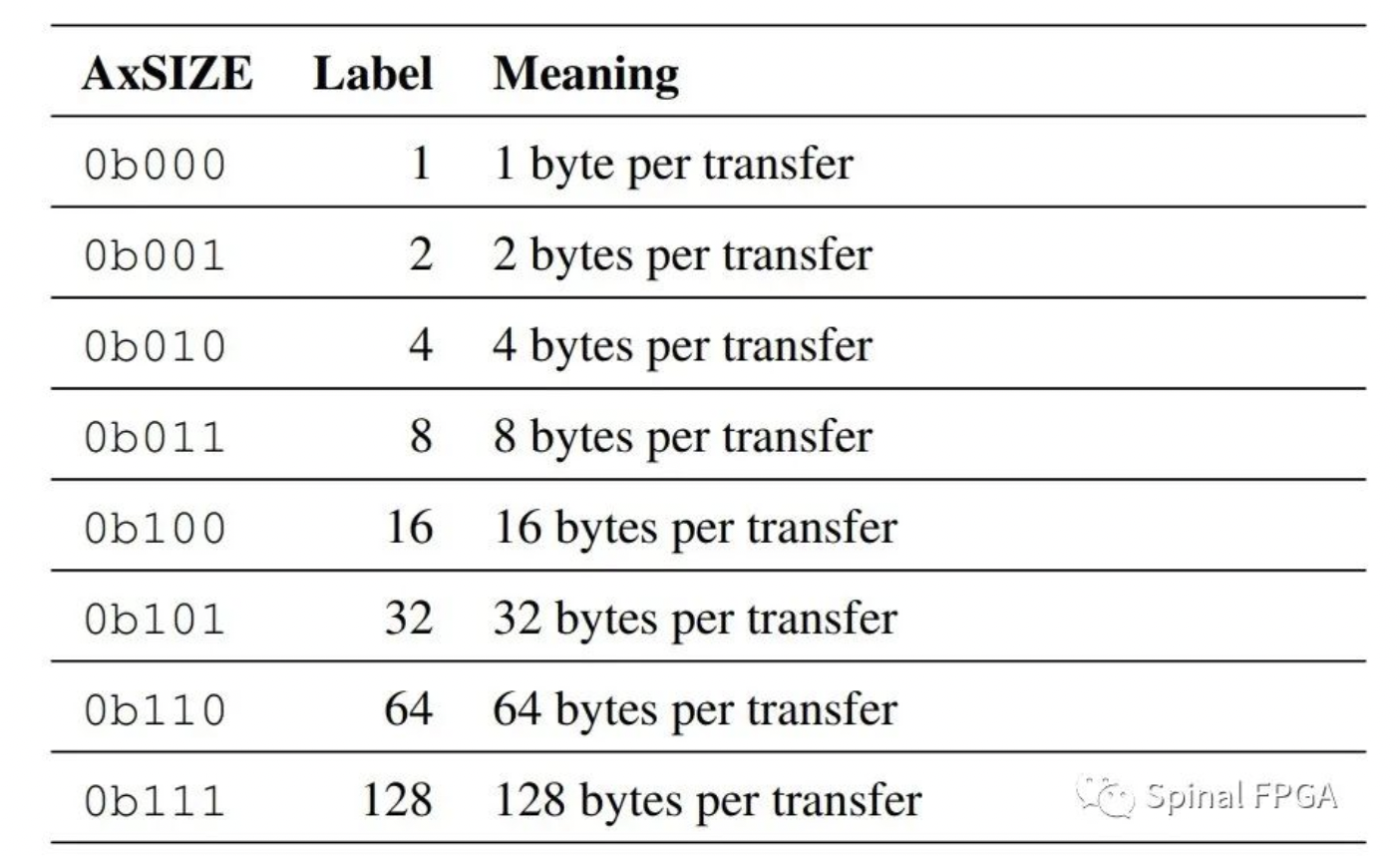

本指南介紹了高級微控制器總線體系結(jié)構(gòu)(AMBA)AXI的主要功能。

該指南解釋了幫助您實現(xiàn)AXI協(xié)議的關(guān)鍵概念和細節(jié)。

在本指南中,我們介紹:

?AMBA是什么。

?為什么AMBA在現(xiàn)代SoC設(shè)計中

2023-08-09 07:37:45

,隨著該介紹,第一個硬件驗證語言誕生了。 ***2 年,還創(chuàng)建了一個新標準 SystemVerilog。 現(xiàn)在有不同的驗證語言可用,其中 e、SystemVerilog、SystemC

2022-02-16 13:36:53

激勵,統(tǒng)計覆蓋率等;3.編寫驗證文檔。任職要求:1.計算機、微電子、自動化等相關(guān)專業(yè),本科及以上學(xué)歷,2年工作經(jīng)驗;2.熟悉c/c++編程語言,Linux操作環(huán)境;3.熟悉SystemVerilog

2017-02-15 13:39:33

2打兩拍systemverilog與VHDL編碼1 本章目錄1)FPGA簡介2)SystemVerilog簡介3)VHDL簡介4)打兩拍verilog編碼5)打兩拍VHDL編碼6)結(jié)束語2 FPGA

2021-07-26 06:19:28

本參考手冊詳細描述了Accellera為使用Verilog硬件描述語言在更高的抽象層次上進行系統(tǒng)的建模和驗證所作的擴展。這些擴展將Verilog語言推向了系統(tǒng)級空間和驗證級空間。SystemVerilog

2009-07-22 12:14:44 187

187 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

20 This chapter introduces the Advanced Microcontroller Bus Architecture (AMBA)specification.

2010-07-19 16:46:10 58

58 分層驗證法在基于AMBA系統(tǒng)中的應(yīng)用

在基于AMBA(Advanced Microcontroller Bus Architecture,先進的微控制器總線體系結(jié)構(gòu))的系統(tǒng)中,用戶設(shè)計的模塊和第三方IP模塊與AMBA AHB(Advanced High-p

2009-03-28 17:05:15 704

704 就 SystemC 和 SystemVerilog 這兩種語言而言, SystemC 是C++在硬件支持方面的擴展,而 SystemVerilog 則繼承了 Verilog,并對 Verilog 在面向?qū)ο蠛?b class="flag-6" style="color: red">驗證能力方面進行了擴展。這兩種語言均支持

2010-08-16 10:52:48 5140

5140 SystemVerilog 是過去10年來多方面技術(shù)發(fā)展和實際試驗的結(jié)晶,包括硬件描述語言(HDL)、硬件驗證語言(HVL)、SystemC、Superlog和屬性規(guī)范語言。它們都從技術(shù)和市場的成敗中得到了豐富的經(jīng)

2010-09-07 09:55:16 1118

1118 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語言,采用驗證方法學(xué)以及驗證庫開發(fā)出先進驗證環(huán)境。文章分為四部分,第一部分概述了用SystemVerilog語言驗證復(fù)雜S

2011-05-09 15:22:02 52

52 文章采用TOP-DOWN 的方法設(shè)計了 AMBA 總線IP 核!它包括AHB 和APB兩個子IP 核 所有AMBA結(jié)構(gòu)模塊均實現(xiàn)了RTL級建模

2011-07-25 18:10:52 91

91 文中分析了基于Systemverilog驗證環(huán)境的結(jié)構(gòu),并在介紹I 2 C總線協(xié)議的基礎(chǔ)上,重點論述了驗證環(huán)境中事務(wù)產(chǎn)生器及驅(qū)動器的設(shè)計。

2011-12-22 17:20:21 27

27 電子設(shè)計創(chuàng)新企業(yè)Cadence設(shè)計系統(tǒng)公司,今天宣布使用ARM AMBA協(xié)議類型的Cadence驗證IP(VIP)實現(xiàn)多個成功驗證項目,這是業(yè)界最廣泛使用的AMBA協(xié)議系列驗證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 997

997 Mentor Graphics 公司(納斯達克代碼:MENT)今日宣布推出面向 ARM AMBA 5 AHB 片上互連規(guī)范的驗證 IP (VIP)。該新 VIP 在 Mentor? 企業(yè)驗證平臺

2015-11-12 11:28:11 1132

1132 俄勒岡州威爾遜維爾,2016 年 3 月 2 日– Mentor Graphics 公司(納斯達克代碼:MENT)今日宣布,推出首個完全原生的 UVM SystemVerilog 內(nèi)存驗證 IP 庫,該內(nèi)存驗證 IP 庫可用于所有常用內(nèi)存設(shè)備、配置和接口。

2016-03-02 14:03:49 1027

1027 AMBA 2.0協(xié)議中文版,學(xué)習(xí)ARM SOC系統(tǒng)必備資料

2016-07-01 16:19:04 0

0 的連接、驅(qū)動器、監(jiān)視器、仿真序列以及功能覆蓋率的建立。 本文呈現(xiàn)出了一種使用UVM驗證方法學(xué)構(gòu)建基于高可配置性的高級微處理器總線架構(gòu)(AMBA)的IP驗證環(huán)境,其中會使用到Synopsys公司的AMBA VIP和Ruby腳本。該驗證環(huán)境可以支持通過使用AMBA設(shè)計參數(shù)進行自

2017-09-15 14:37:34 6

6 本文描述了一個符合驗證方法手冊(VMM)的基于SystemVerilog事務(wù)的測試平臺,并通過實例說明了使用基于事務(wù)的方法創(chuàng)建一個全面的約束隨機驗證環(huán)境中的VMM方法。這包括交易的生成和通過交易

2019-05-28 08:00:00 2

2 新思科技為下一代ArmAMBA協(xié)議(包括AMBA CXS)提供了廣泛的驗證解決方案。 更令人振奮的是,新思科技還為基于Arm的協(xié)議提供了驗證自動化解決方案,包括用于測試平臺生成的VC

2020-10-15 09:37:55 3402

3402 手冊的這一部分探討了使用SystemVerilog進行驗證,然后查看了使用SystemVerilog的優(yōu)點和缺點。

2021-03-29 10:32:46 23

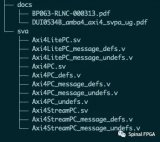

23 在SpinalHDL里,其Libraries里提供了關(guān)于總線相關(guān)的庫。包含AMBA3、AMBA4、AVALON等總線類型,并提供了bus slave factory工具

2021-04-08 17:28:26 2839

2839

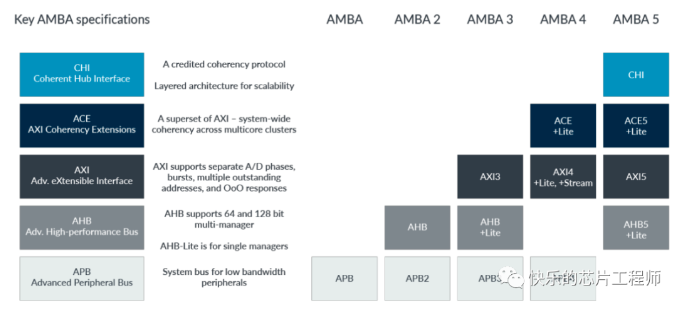

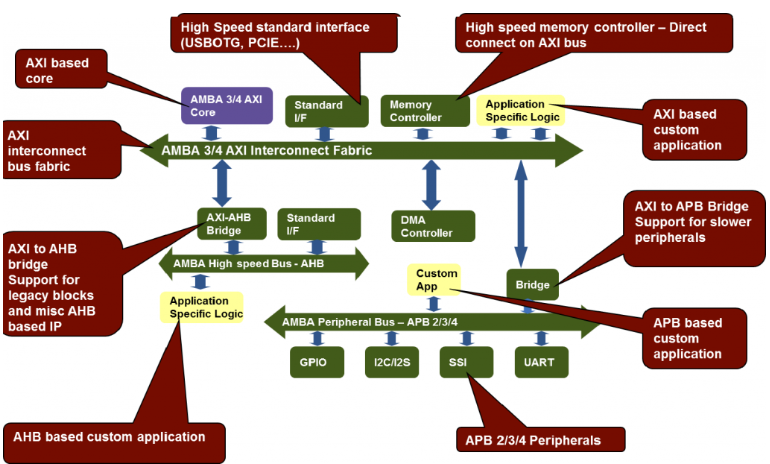

1.1.AMBA發(fā)展史 AMAB1.0 AMBA2.0 AMBA3.0 AMBA4.0 AMBA1.0:ASB協(xié)議和APB協(xié)議;AMBA2.0:AHB協(xié)議、ASB協(xié)議和APB協(xié)議;AMBA

2021-05-19 14:22:56 1835

1835

1.1.AMBA發(fā)展史 AMAB1.0 AMBA2.0 AMBA3.0 AMBA4.0 AMBA1.0:ASB協(xié)議和APB協(xié)議;AMBA2.0:AHB協(xié)議、ASB協(xié)議和APB協(xié)議;AMBA

2021-09-06 09:53:08 2718

2718

作者:limanjihe ?https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一種硬件描述和驗證語言

2021-10-11 10:35:38 2042

2042 關(guān)于我:2020屆雙非學(xué)校材料專業(yè)畢業(yè),現(xiàn)在已轉(zhuǎn)行芯片驗證,入職兩個月。最近MCU項目在用Synopsys公司的VIP,正好自己在看AMBA的VIP,就整理一下:4-介紹AMBA System

2021-12-08 16:21:07 10

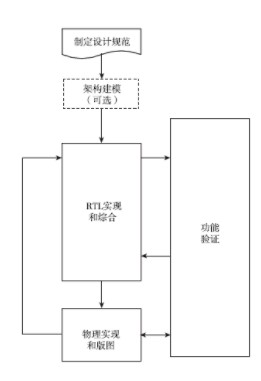

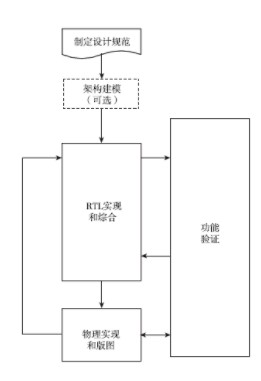

10 驗證是一個覆蓋面比較廣的課題,主要包括功能驗證、物理驗證、時序驗證等。我們常常涉及功能驗證,以確保設(shè)計能夠按照設(shè)計規(guī)范實現(xiàn)應(yīng)有功能。為了完成功能驗證,我們需要搭建驗證平臺testbench,這也是業(yè)界最常用的驗證手段。

2022-08-05 17:25:02 1974

1974

利用Systemverilog+UVM搭建soc驗證環(huán)境

2022-08-08 14:35:05 5

5 IEEE SystemVerilog標準:統(tǒng)一的硬件設(shè)計規(guī)范和驗證語言

2022-08-25 15:52:21 0

0 SystemVerilog casting意味著將一種數(shù)據(jù)類型轉(zhuǎn)換為另一種數(shù)據(jù)類型。在將一個變量賦值給另一個變量時,SystemVerilog要求這兩個變量具有相同的數(shù)據(jù)類型。

2022-10-17 14:35:40 1960

1960 學(xué)習(xí)Systemverilog必備的手冊,很全且介紹詳細

2022-10-19 16:04:06 2

2 SystemVerilog“struct”表示相同或不同數(shù)據(jù)類型的集合。

2022-11-07 10:18:20 1852

1852 SystemVerilog中的句柄賦值和對象復(fù)制的概念是有區(qū)別的。

2022-11-21 10:32:59 523

523 百度百科對UVM的釋義如下:通用驗證方法學(xué)(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平臺開發(fā)框架,驗證工程師可以利用其可重用組件構(gòu)建具有標準化層次結(jié)構(gòu)和接口的功能驗證環(huán)境。

2022-11-30 12:47:00 1060

1060 SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充了 C語言 數(shù)據(jù)類型、結(jié)構(gòu)、壓縮

2022-12-08 10:35:05 1262

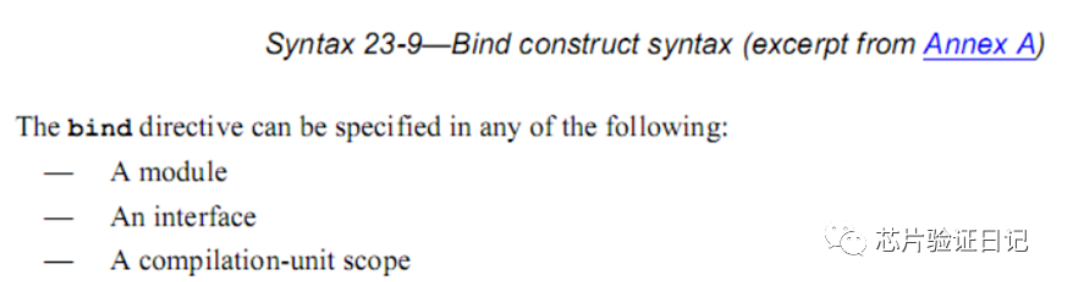

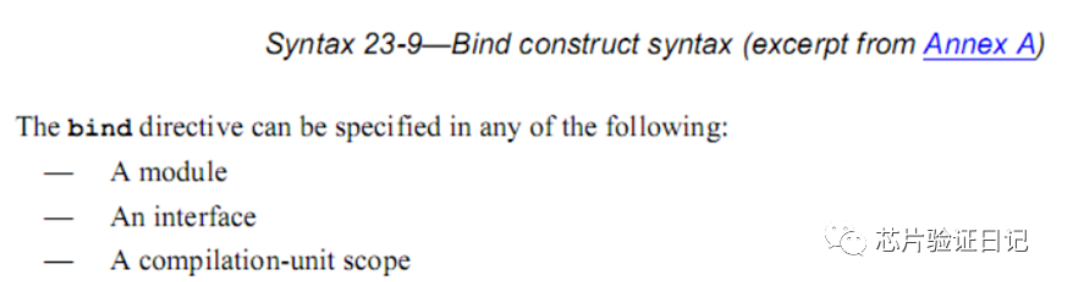

1262 bind是systemverilog中一個重要的知識點,很多時候能夠在驗證中發(fā)揮重要的作用,今天就針對這個知識點做一個梳理,希望能幫助到大家。

2023-01-11 08:59:03 6173

6173

持SystemVerilog語言,是開發(fā)仿真器的一個重要任務(wù)。 ? SystemVerilog的發(fā)展歷程 ? 數(shù)字芯片的驗證技術(shù)是隨著Verilog語法的演變而演變的。 最早,Verilog是完全用來描述

2023-04-07 14:40:34 535

535

高級微控制器總線架構(gòu)(Advanced Microcontroller Bus Architecture)或 AMBA 是一種開放標準的片上互連規(guī)范

2023-05-04 10:18:57 1719

1719

Arm 在 1990 年代后期推出了 AMBA。第一批 AMBA 總線是高級系統(tǒng)總線 (ASB:Advanced System Bus) 和高級外圍總線 (APB:Advanced Peripheral Bus)。ASB 已被更新的協(xié)議所取代,而 APB 今天仍在廣泛使用。

2023-05-04 11:00:32 732

732

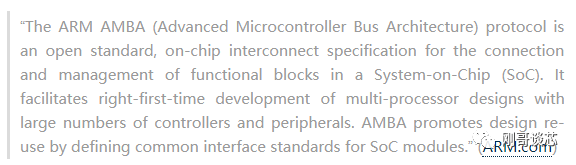

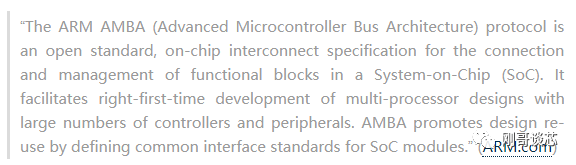

ARM AMBA (Advanced Microcontroller Bus Architecture)協(xié)議是一種公開標準,主要用于片上系統(tǒng)(SoC)中功能模塊連接和管理的互聯(lián)規(guī)范。它有助于一次性

2023-05-04 11:31:25 1082

1082

AMBA規(guī)范是一個開放標準,可免費從ARM公司獲得。目前,AMBA規(guī)范得到眾多第三方支持,被90%以上的ARM合作伙伴采用,在基于ARM處理器內(nèi)核的SoC設(shè)計中,已經(jīng)成為廣泛支持的現(xiàn)有互聯(lián)標準之一。

2023-05-04 11:43:02 385

385

AMBA總線陣營的強大超乎多數(shù)人的想象。AMBA總線是一個在SoC領(lǐng)域使用的事實上的標準。AMBA總線的最大優(yōu)點是開放的架構(gòu),和因此帶來的免費。開放的總線標準使AMBA總線迅速普及,而且更易吸收整個半導(dǎo)體界的成果。

2023-05-04 14:45:37 1943

1943

AMBA總線陣營的強大超乎多數(shù)人的想象。AMBA總線是一個在SoC領(lǐng)域使用的事實上的標準。AMBA總線的最大優(yōu)點是開放的架構(gòu),和因此帶來的免費。開放的總線標準使AMBA總線迅速普及,而且更易吸收整個半導(dǎo)體界的成果。

2023-05-04 14:47:43 1897

1897

ARM所推出的AMBA4總線相對來講還是應(yīng)用廣泛的。無論是芯片設(shè)計里還是FPGA設(shè)計里,時常能見到AMBA4總線的身影。

2023-05-05 15:37:55 500

500

相干集線器接口,俗稱 CHI,是一種接口規(guī)范,是5千從 Arm 生成 AMBA 協(xié)議 (AMBA?? 5),于 2013 年發(fā)布。AMBA? 5 CHI 定義了用于將完全相干處理器和動態(tài)內(nèi)存控制器連接到高性能無阻塞互連的接口。

2023-05-25 17:17:31 891

891 為了使 SOC 驗證工程師能夠創(chuàng)建高度可配置的 AMBA 結(jié)構(gòu),系統(tǒng)環(huán)境應(yīng)提供占位符,用于將 DUT 與任何典型的 AMBA VIP 組件(如 AXI3/4/ACE、AHB 或 APB)掛鉤。通過

2023-05-29 09:33:48 412

412

從這張圖片中,我清楚地看到不同口味的多個AMBA組件的優(yōu)勢(AXI3 / 4,ACE,AHB,APB)。因此,即使我們有所有不同的 VIP 來代表這些 .不同的口味,就完成完整子系統(tǒng)的驗證而言,這并不是一個灌籃。將所有這些組件拼接在一起并提出這樣一個驗證環(huán)境本身就是一個巨大的挑戰(zhàn)。

2023-05-29 10:35:20 365

365

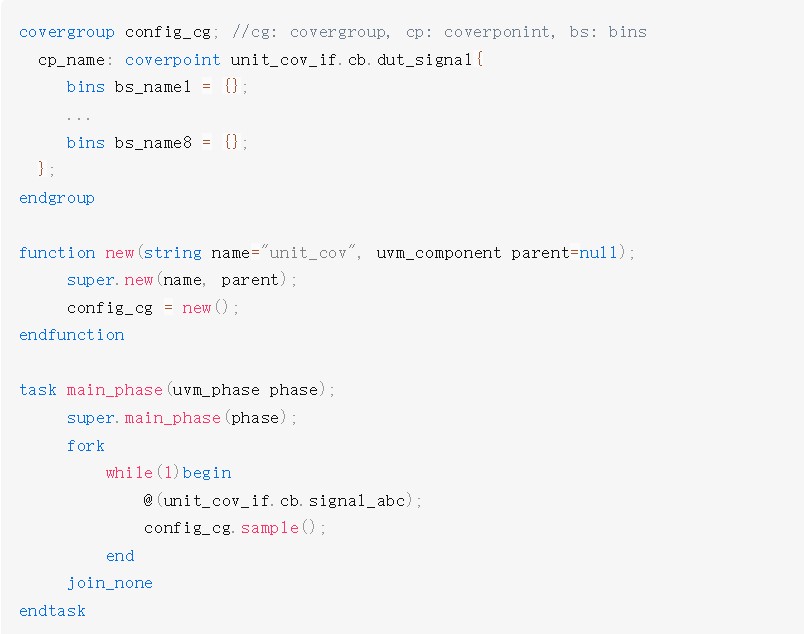

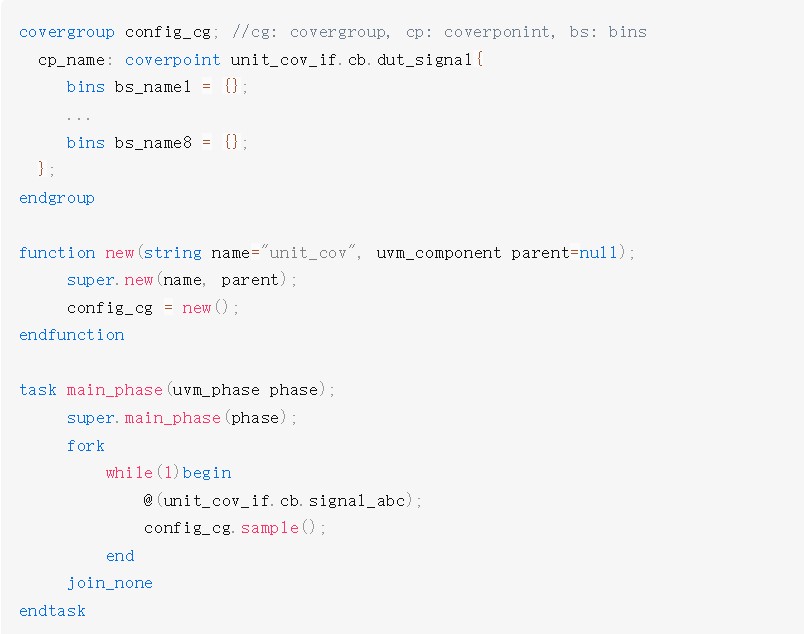

SystemVerilog是一名芯片驗證工程師,必須掌握的一門語言,其中Function Coverage是必須要懂的知識點之一;

2023-06-04 16:30:24 3702

3702

AMBA總線無論FPGA還是ASIC,應(yīng)該都是比較常用的一組總線協(xié)議。

2023-06-11 10:22:06 591

591

為了確保驗證的完備性,我們需要量化驗證目標。SystemVerilog提供了一套豐富的覆蓋率建模方式。

2023-06-25 10:44:16 520

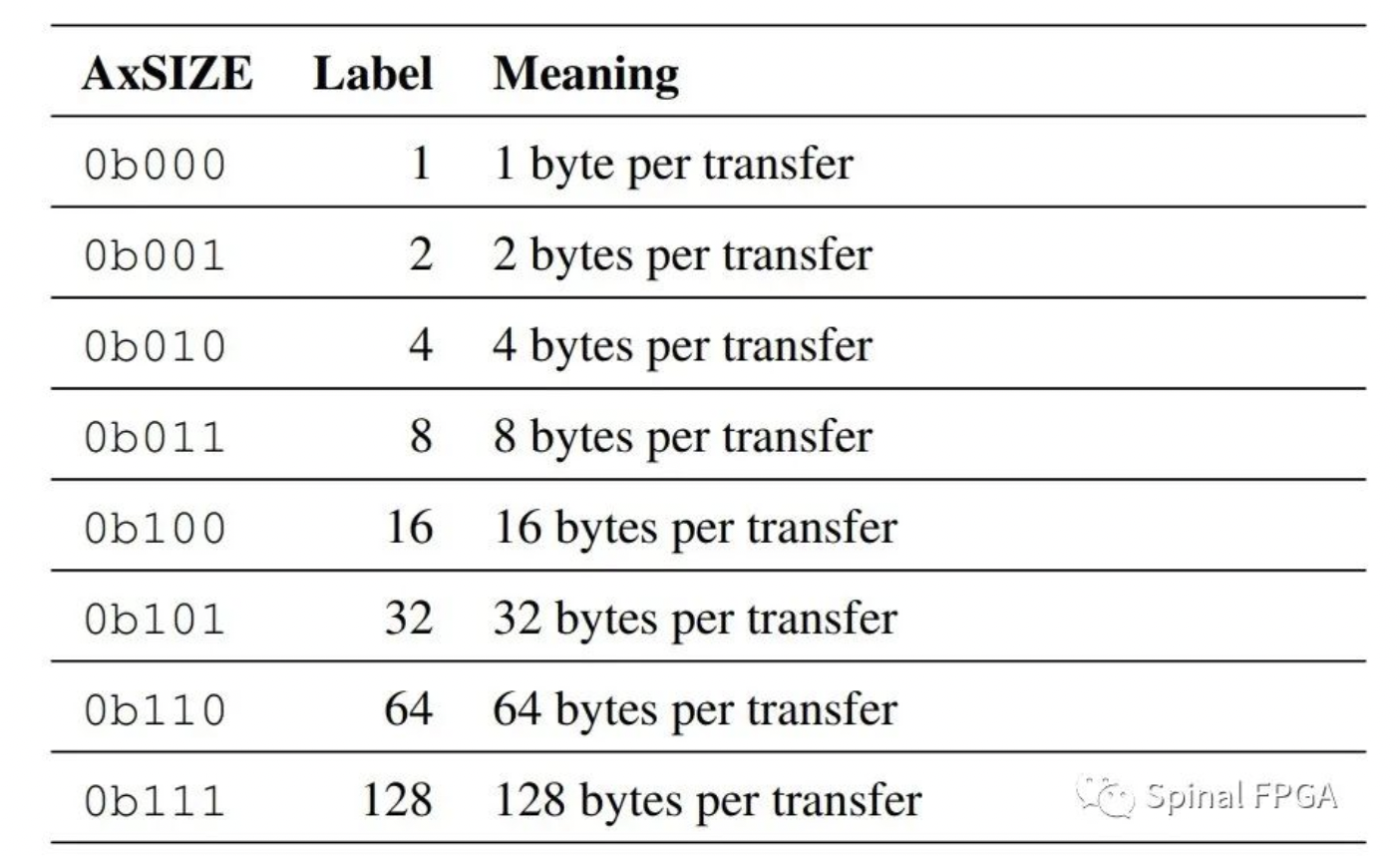

520 AMBA總線無論FPGA還是ASIC,應(yīng)該都是比較常用的一組總線協(xié)議。對于其中的協(xié)議,有一種傳輸格式叫Narrow Transfers,頗有些“無聊”~

2023-06-30 17:21:40 499

499

本文講一下SystemVerilog的time slot里的regions以及events的調(diào)度。SystemVerilog語言是根據(jù)離散事件執(zhí)行模型定義的,由events驅(qū)動。

2023-07-12 11:20:32 775

775

談到SystemVerilog,很多工程師都認為SystemVerilog僅僅是一門驗證語言,事實上不只如此。傳統(tǒng)的Verilog和VHDL被稱為HDL(Hardware Description

2023-10-19 11:19:19 342

342

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 272

272

電子發(fā)燒友App

電子發(fā)燒友App

評論