在UVM驗證環境的項目中,經常需要使用內置的print()函數或sprint()函數打印

2023-12-20 10:14:35 951

951

ASIC1810 - ASIC1810 - List of Unclassifed Manufacturers

2022-11-04 17:22:44

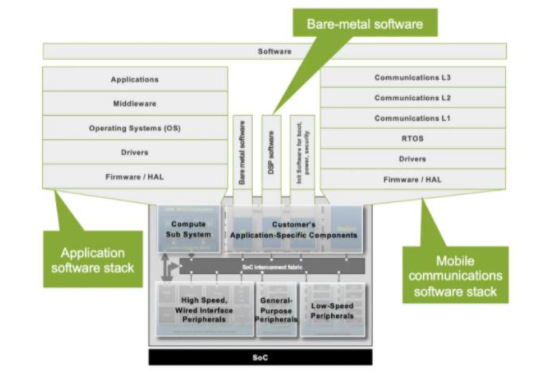

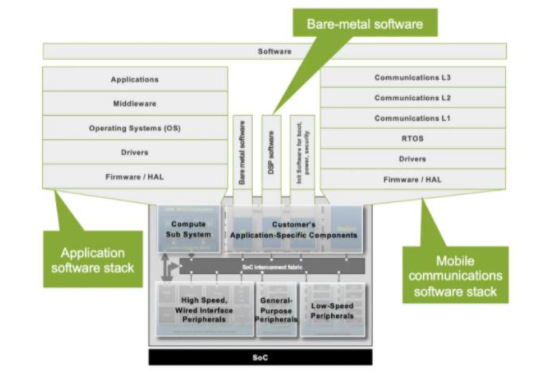

原型驗證---用軟件的方法來發現硬件的問題 在芯片tap-out之前,通常都會計算一下風險,例如存在一些的嚴重錯誤可能性。通常要某個人簽字來確認是否去生產。這是一個艱難的決定。ASIC的產品NRE

2019-07-11 08:19:24

1ASIC 驗證技術.................................................11.1 ASIC 設計流程

2015-09-18 15:26:25

ASIC設計-FPGA原型驗證

2020-03-19 16:15:49

1. 問題 假如用以下兩種方式啟動sequence,方法1用sequence的start()方法啟動seq1,方法2用UVM的default_sequence機制啟動seq2。那么seq1

2023-04-04 17:15:07

驗證方法簡介 設計驗證是用于證明設計正確性的過程,要求和規格。 在數字設計流程中,驗證可確保芯片按照設計意圖正確運行,然后再將設計送去制造。 具體來說,驗證方法是驗證集成電路設計的標準化方法。 驗證

2022-02-13 17:03:49

FPGA原型驗證已是當前原型驗證的主流且成熟的芯片驗證方法——它通過將RTL移植到現場可編程門陣列(FPGA)來驗證ASIC的功能,并在芯片的基本功能驗證通過后就可以開始驅動的開發,一直到芯片

2020-08-21 05:00:12

有流水處理和響應迅速的特點。 芯片解密認為,FPGA一般來說比ASIC的速度要慢,無法完成復雜的設計,但是功耗較低。但是他們也有很多的優點比如可以快速成品,可以被修改來改正程序中的錯誤和更便宜的造價

2017-06-12 15:56:59

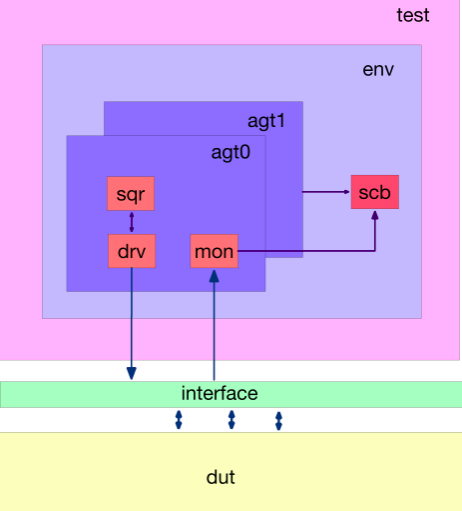

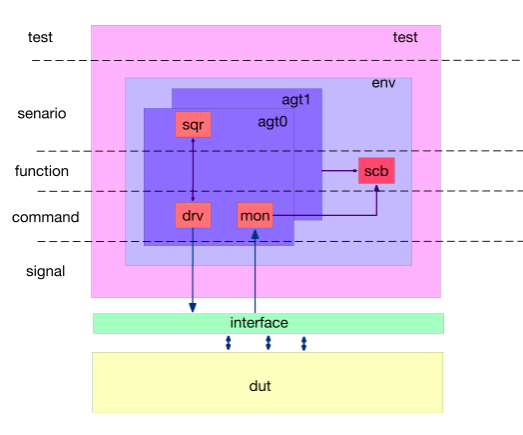

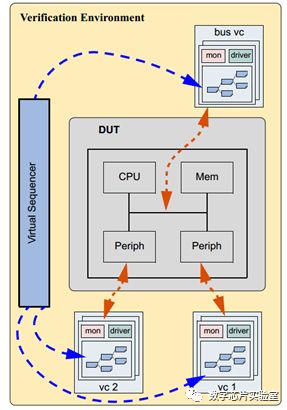

model)。一個簡單的驗證平臺框圖:在UVM中,引入了agent和sequence的概念,因此UVM中驗證平臺的典型框圖長這樣:通知:本章更新后在更新一篇《IC驗證之UVM常用宏匯總(四)》將不

2020-12-02 15:21:34

加入factory機制 上一節《IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(五)》給出了一個只有driver、使用UVM搭建的驗證平臺。嚴格來說這根本就不算是UVM驗證

2020-12-08 12:07:21

本帖最后由 IC那些事兒 于 2020-12-4 15:50 編輯

上次更新完《IC驗證"UVM驗證平臺"組成》后本打算不再更新......但有人反映要繼續更新...繼續

2020-12-04 15:48:19

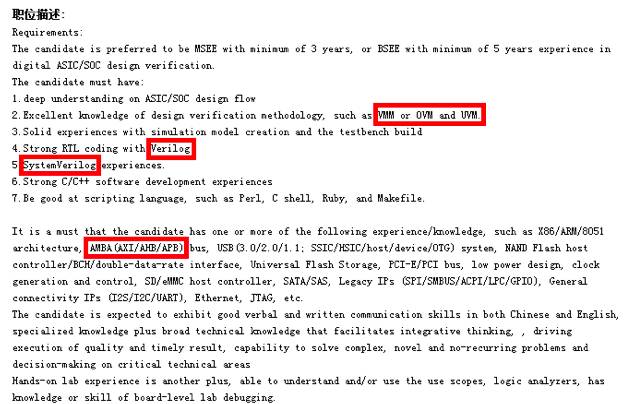

Synopsys在VMM中的寄存器解決方案RAL。同時,UVM還吸收了VMM中的 一些優秀的實現方式。可以說,UVM繼承了VMM和OVM的優點,克服了各自的缺點,代表了驗證方法學的發展方向。學了UVM之后能做

2020-12-01 15:09:14

: +define+MACRO 或者: +define+MACRO=100擴展寄存器模型中的數據位寬:`define UVM_REG_DATA_WIDTH 128擴展寄存器模型中的地址位寬:`define

2020-12-02 15:24:35

在上一節中,**《IC驗證"UVM驗證平臺加入factory機制"(六)》**雖然輸出了“main_phase is called”,但是“data is drived”并沒有

2020-12-09 18:28:15

第二章 驗證flow驗證的Roadmap驗證的目標UVM驗證方法學ASIC驗證分解驗證策略和任務的分解AMBA可重用、靈活性、兼容性、廣泛支持一.驗證的Roadmap1.ASIC芯片項目流程市場需求

2021-11-01 06:28:47

設計驗證方法 MyHDL - 基于 Python 的硬件描述語言,也具有驗證功能 PyUVM – 使用 cocotb 的 UVM 的 Python 實現 UVM Python –UVM的 Python

2022-11-03 13:07:24

,本科5年數字芯片驗證工程師崗位要求:1、熟悉systemverilog 語言,熟練掌握UVM/VMM/OVM驗證方法學,獨立完成過中等規模以上模塊的驗證開發2、熟悉數字芯片驗證流程,三年以上相關工作經驗3、碩士3年,本科5年聯系方式:ucollide@163.com一八五八3907八零五

2018-03-13 09:27:17

【招聘】射頻/模擬、ASIC設計/驗證、系統、模擬設計等 射頻集成電路工程師(TRX 方向)-BJ 射頻/模擬集成電路工程師(RF/Analog IC Engineer)-BJ 射頻IC工程師

2017-03-03 14:54:37

UVM Report機制概述

2020-12-21 06:55:05

uvm_reg_field是什么

2020-12-17 06:10:56

大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源?本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構。我們一個

2022-02-14 06:46:33

招聘崗位:芯片設計數字,驗證工程師崗位要求:1.本科及以上學歷,2年半以上工作經驗2.精通verilog,SV等語言3.有端到端項目的交付經驗4.精通VMM/UVM驗證方法學5.具備團隊合作意識,責任心強聯系方式:***簡歷投遞郵箱:lzdnewmail@163.com

2017-10-09 19:47:57

廈門asic崗位招聘。應屆和社招均歡迎,本科碩士均歡迎。做手機芯片的,國內沒幾家,一搜就知道名字了。簡歷請發郵箱 shuli198349@163.com

2015-06-12 12:07:37

Systemverilog [1]和 UVM [2]為驗證團隊提供結構和規則。它使得在許多測試中能獲得一致的結果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規UVM測試平臺的各種方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]為驗證團隊提供結構和規則。它使得在許多測試中能獲得一致的結果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規UVM測試平臺的各種方法。

2020-12-15 07:38:34

請教各位大佬,UVM是基于sv的驗證方法學,如果采用systemc語言編程,如何實現?

2019-11-07 15:30:16

),通常也叫寄存器模型,顧名思義就是對寄存器這個部件的建模。本文要介紹的內容,包括對UVM寄存器模型的概述,如何構建寄存器模型,以及如何將寄存器模型集成到驗證環境中。篇幅原因,將在下一篇文章再給出寄存器

2022-09-23 14:29:03

講述兩個內容,芯片驗證以及驗證計劃。首先來看看芯片驗證在芯片設計當中的地位。芯片驗證是在一個芯片設計的過程當中,驗證各個轉化階段是否正確的執行的過程,一個芯片的設計涉及到多個階段的轉化。首先,分析市場需求

2021-01-21 15:59:03

原文鏈接:https://zhuanlan.zhihu.com/p/345775995大家好,我是一哥,上章內容主要講述兩個內容,芯片驗證以及驗證計劃。那本章我們主要講述的內容有介紹什么是uvm

2021-01-21 16:00:16

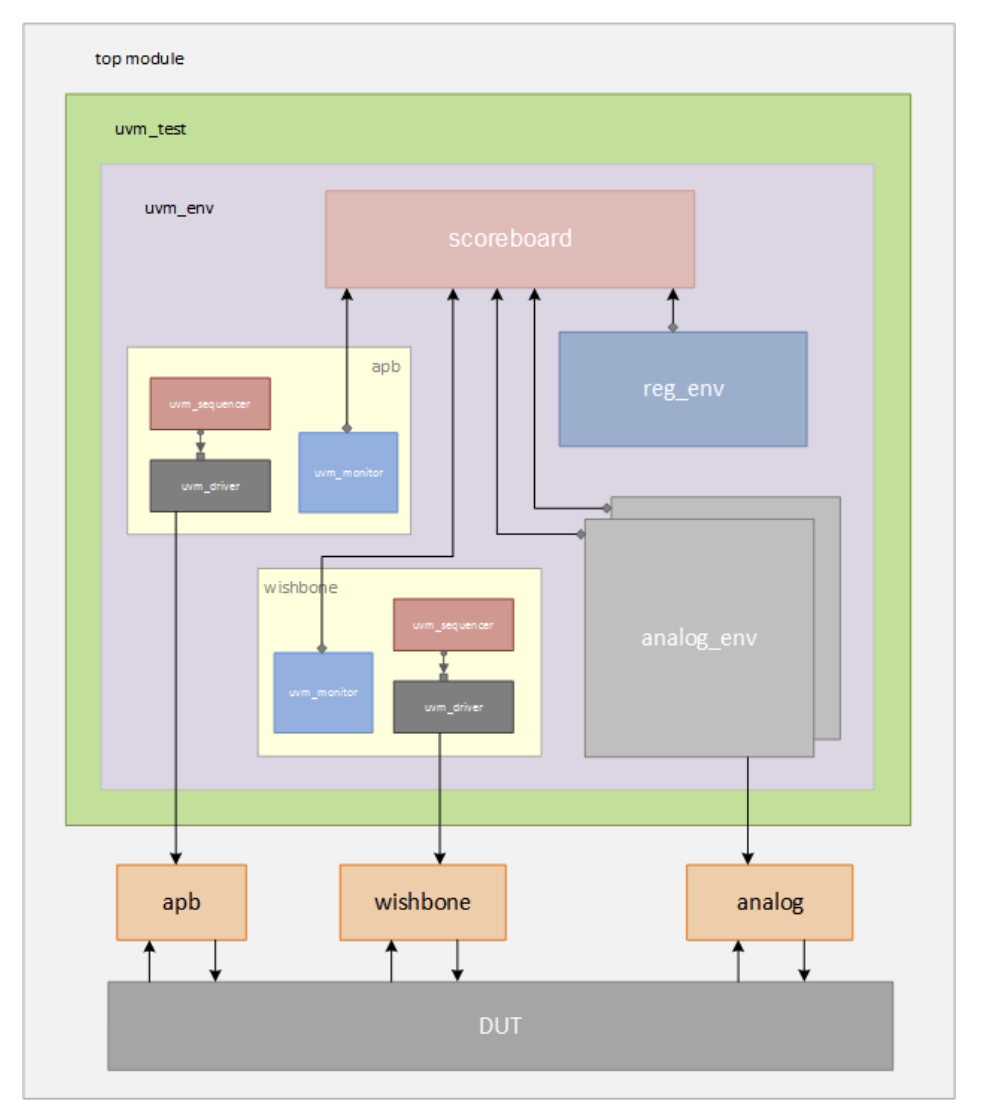

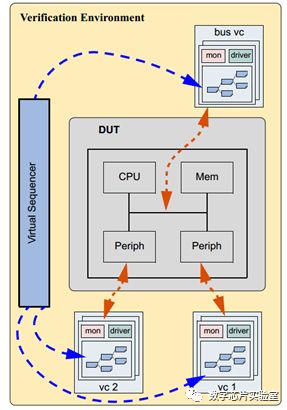

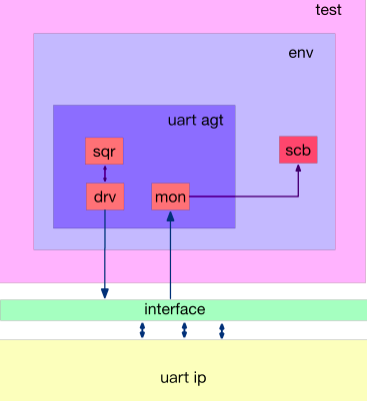

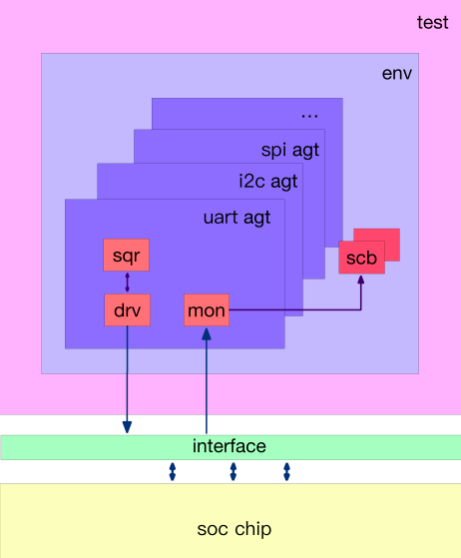

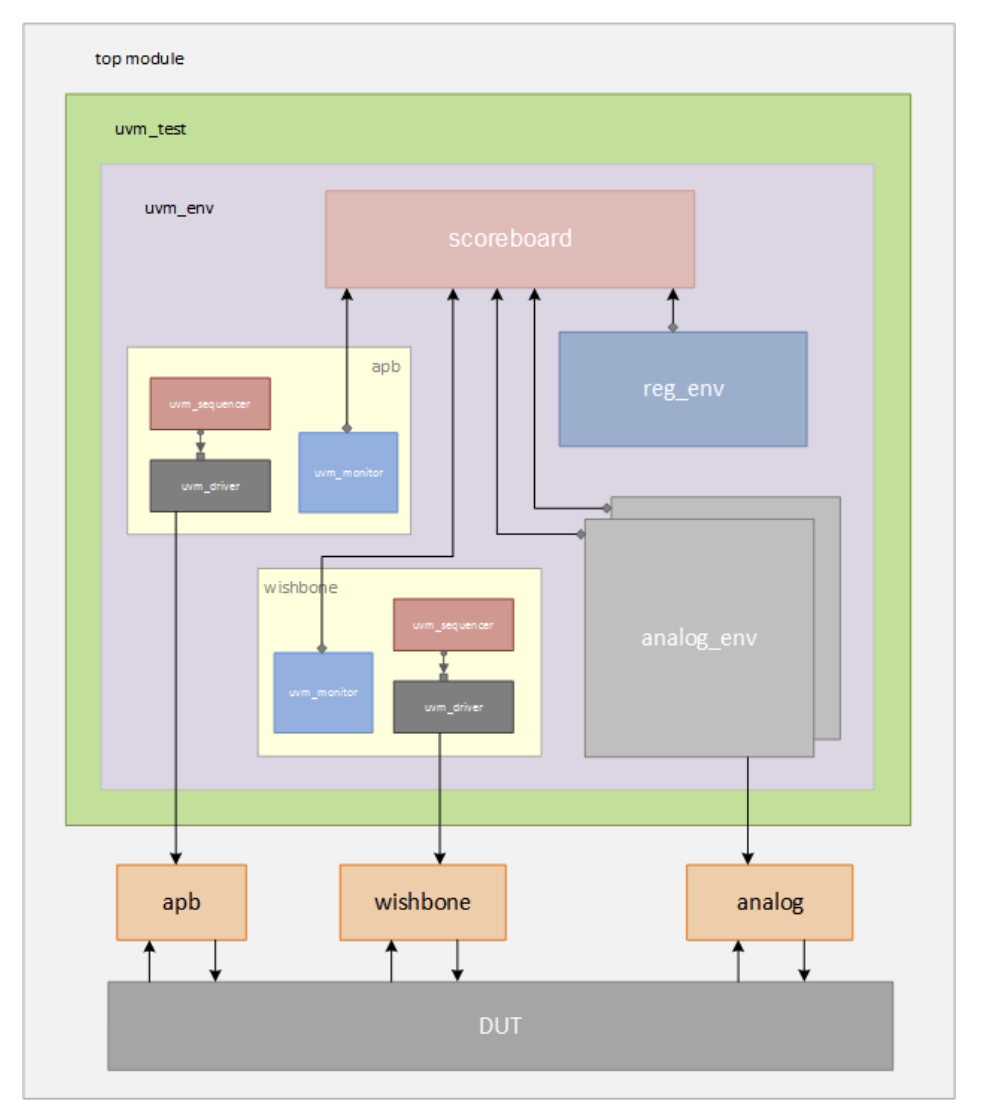

應用的過程中,將uvm的組件封裝起來,可以將這些封裝的組件呢作為一個整體進行重用,在進行芯片級或者是系統級驗證的時候,往往會出現多個模塊的驗證。 此時,測試平臺的結構會發生變化,圖中的測試平臺實現了

2021-01-22 15:32:04

的transaction,以及創建用于產生事物的事物發生器sequence。 在uvm驗證平臺中穿梭各個組件之間的基本信息單元是一個被稱為transaction的數據對象,也就是我們前面所說的事物

2021-01-26 10:05:37

大家好,我是一哥,上章一個典型的uvm驗證平臺應該是什么樣子的?從本章開始就正式進入uvm知識的學習。先一步一步搭建一個簡單的可運行的測試平臺。 本章首先來介紹一下構成uvm測試平臺的主要組件

2021-01-22 15:33:26

新手學習SystemVerilog & UVM指南 從剛接觸System Verilog以及后來的VMM,OVM,UVM已經有很多年了,隨著電子工業的逐步發展,國內對驗證人才的需求也會急劇

2015-03-11 16:24:35

`深圳單片機開發方案公司,專注電子產片領域單片機方案開發,提供優質的音頻轉接頭單片機方案ASIC芯片。電子產品開發之蘋果手機7/8/X小藥丸音頻轉接頭二合一單片機方案ASIC芯片完美實現蘋果手機邊

2018-10-23 14:49:24

形式驗證方法論基于斷言的驗證進行“驗證”的其他方法通用驗證方法 (UVM) – Accellera/Cadence嵌入式UVMUVM測試開源 VHDL 驗證方法 (OSVVM)UVVM:通用 VHDL

2022-11-26 20:43:20

獵頭職位:IC驗證工程師【北京】崗位職責:1.根據芯片架構文檔和設計要點,制定驗證方案,擬定驗證計劃;2.根據驗證方案和計劃,實施驗證,包括編寫參考模型、搭建仿真驗證平臺與迭代改進、編寫完備的驗證

2017-02-15 13:39:33

。往往我們在書寫測試用例或者sequences的時候會有查詢驗證平臺組件uvm_component的需求,比如env/driver/monitor。由于sequences不是測試平臺層次結構的一部分,實現

2022-04-11 16:43:42

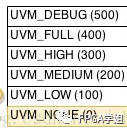

uvm_info宏的定義如下: `define uvm_info(ID,MSG,VERBOSITY) \ begin \ if (uvm_report_enabled(VERBOSITY

2023-03-17 16:41:28

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法。本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。1、RFID芯片的FPGA

2019-05-29 08:03:31

ASIC 芯片全定制費用高、風險大、周期長,因此在全定制之前一般先用FPGA 或CPLD 等可編程邏輯器件做功能驗證。但在一些空間極為有限、成本極低的應用場合,采用FPGA 或者CPLD 顯然

2009-09-25 16:00:32 12

12 全球電子設計創新領先企業Cadence設計系統公司,今天宣布了業界最全面的用于系統級芯片(SoC)驗證的通用驗證方法學(UVM)開源參考流程。為了配合Cadence EDA360中SoC實現能力的策略,

2010-06-28 08:29:14 2240

2240 FPGA原型驗證和其他驗證方法是不同的,任何一種其他驗證方法都是ASIC驗證中的一個環節,而FPGA驗證卻是一個過程。由于FPGA與ASIC在結構、性能上各不相同,ASIC是基于標準單元庫,FPGA用的

2010-09-10 17:22:26 989

989 對ASIC設計進行FPGA原型驗證時,由于物理結構不同,ASIC的代碼必須進行一定的轉換后才能作為FPGA的輸入。 現代集成電路設計中,芯片的規模和復雜度正呈指數增加。尤其在ASIC設計流程中

2011-03-25 15:16:20 108

108 本文描述ASIC驗證方法和過程,有助于ASIC設計者對驗證的認識。模擬是驗證ASIC并產生測試矢量的唯一途徑,設計者可以對ASIC芯片或者在ASIC應用系統中進行功能和時序模擬。

2012-05-24 09:32:47 23

23 本文描述ASIC驗證方法和過程,有助于ASIC設計者對驗證的認識。模擬是驗證ASIC并產生測試矢量的唯一途徑,設計者可以對ASIC芯片或者在ASIC應用系統中進行功能和時序模擬。

2012-05-24 09:32:47 27

27 俄勒岡州威爾遜維爾,2016 年 3 月 2 日– Mentor Graphics 公司(納斯達克代碼:MENT)今日宣布,推出首個完全原生的 UVM SystemVerilog 內存驗證 IP 庫,該內存驗證 IP 庫可用于所有常用內存設備、配置和接口。

2016-03-02 14:03:49 1027

1027 基于UVM的CPU卡芯片驗證平臺_錢一文

2017-01-07 19:00:39 4

4 基于UVM的驗證平臺設計研究_王國軍

2017-01-07 19:00:39 4

4 基于UVM的CAN模塊自驗證方法_熊濤

2017-01-08 14:47:53 3

3 一種基于UVM的混合信號驗證環境_耿睿

2017-01-07 21:39:44 1

1 四軸電機伺服控制ASIC芯片_劉亞靜

2017-01-07 15:17:12 4

4 UVM使得驗證測試平臺的結構得以標準化,各種復用策略及標準對于提高驗證質量、縮短項目周期都非常有效。垂直重用是常見的復用策略之一,即同一項目測試平臺復用于不同驗證層次。驗證中常將最底層的IP級驗證平臺向更高的集成層復用,而UVM寄存器模型則是驗證平臺復用的一個關鍵部分。

2017-09-15 11:49:08 15

15 的連接、驅動器、監視器、仿真序列以及功能覆蓋率的建立。 本文呈現出了一種使用UVM驗證方法學構建基于高可配置性的高級微處理器總線架構(AMBA)的IP驗證環境,其中會使用到Synopsys公司的AMBA VIP和Ruby腳本。該驗證環境可以支持通過使用AMBA設計參數進行自

2017-09-15 14:37:34 6

6 UVM已經成為了一種高效率的、從模塊級到系統級完整驗證環境開發標準,其中一個關鍵的原則是UVM可以開發出可重用的驗證組件。獲得重用動力的一個方面表現為標準的仿真器和硬件加速之間的驗證組件和環境的復用

2017-09-15 17:08:11 14

14 毋庸置疑,UVM大大提高了我們開發驗證平臺的效率。但同時,熟練掌握UVM搭建驗證平臺也并不是一件容易的事情。同時由于不同驗證工程師搭建環境的風格不太一致,所以在一個項目中常會出現不好管理,甚至前后

2017-09-15 17:18:01 22

22 聯發科從6年就開始布局研發ASIC芯片,現在聯發科基于16nm制程的ASIC芯片已經占據智能音箱市場超8成市占率。為了進一步擴充 ASIC產品陣線,聯發科推出了業界第一個通過 7nm FinFET 硅驗證(Silicon-Proven)的 56G PAM4 SerDes IP。

2018-04-25 21:23:12 34711

34711 近年來,ASIC設計規模的增大帶來了前所未有的芯片原型驗證問題,單顆大容量的FPGA通常已不足以容下千萬門級、甚至上億門級的邏輯設計。現今,將整個驗證設計分割到多個采用最新工藝大容量FPGA中,FPGA通過高速總線互聯,成為大規模ASIC或SOC原型驗證的極佳選擇。

2018-07-02 08:20:00 1695

1695 采用fpga原型技術驗證asic設計,首先需要把asic設計轉化為fpga設計。但asic是基于標準單元庫,fpga則是基于查找表,asic和fpga物理結構上的不同,決定了asic代碼需要一定

2019-07-23 08:07:00 1923

1923

等級的度量:基于通用驗證方法(UVM)的形式驗證和隨機約束測試增加了發現錯誤的可能性。有時我們為RTL驗證創建一個完美有效的測試,但發現它不能在門級仿真期間重復使用,因為UVM監視器掛在內部SoC信號上,這些信號在實現階段后可能會消失或改變。

2019-08-09 15:25:34 6862

6862

讀者思考UVM為什么要引入這些機制,從而使讀者知其然,更知其所以然。本書以一個完整的示例開篇,使得讀者一開始就對如何使用UVM搭建驗證平臺有總體的概念。針對沒有面向對象編程基礎的用戶,本書在附錄中簡要介紹了面向對象的概念及SystemVerilog中區別于其他編程語言的一些特殊語法。

2019-11-29 08:00:00 28

28 近幾十年來,集成電路事業發展迅速,設計與工藝技術不斷發展,更多和更復雜的功能被集成到一塊芯片上。SoC的集成度和復雜度大大提高,在IC設計中就容易引入錯誤,所以驗證工作將變得艱巨。隨著IC設計規模

2020-01-27 17:21:00 6132

6132

Wilson Research Group 的一項最近研究發現,48% 的 FPGA 設計項目和 71% 的 ASIC設計項目依賴 UVM 進行設計驗證。

2020-03-02 18:12:24 1019

1019 MathWorks宣布,HDLVerifier從現已上市的Release2019b開始提供對UniversalVerificationMethodology(UVM)的支持。

2020-03-07 14:29:17 815

815 本章第一節將大體介紹一下感性意義上的UVM,這里不會講的很詳細,因為關于UVM的歷史在網上已經有太多的資料第二節講述驗證平臺的組成,這里也只是介紹一個輪廓。第三節開始則會教我們一步一步搭建一個UVM

2020-07-01 08:00:00 69

69 根據威爾遜研究集團和西門子EDA的數據,即使在EDA工具的研發上花費了數十億美元,在驗證人工上又花費了數百億美元,但只有30%到50%的ASIC設計是第一次正確的。 即便如此,這些設計仍然有bug

2021-02-27 11:01:44 1436

1436

本文是本人對xilinx XC7V系列FPGA用于ASIC前端驗證遇到問題的總結,為自己記錄并分享給大家,如果有歧義或錯誤請大家在評論里指出。

2021-01-12 17:31:44 9

9 盡管本指南提供了一組說明,以執行一個或多個特定的驗證任務,但應 以教育,經驗和專業判斷為補充。 并非本指南的所有方面都可能 適用于所有情況。 《 UVM 1.1用戶指南》不一定代表標準 必須謹慎判斷給定的專業服務是否足夠,也不應以此文件為依據 應用時無需考慮項目的獨特方面。

2021-03-29 10:41:32 21

21 ASIC芯片設計開發流程說明。

2021-04-07 09:18:59 64

64 第二章 驗證flow驗證的Roadmap驗證的目標UVM驗證方法學ASIC驗證分解驗證策略和任務的分解AMBA可重用、靈活性、兼容性、廣泛支持一.驗證的Roadmap1.ASIC芯片項目流程市場需求

2021-10-25 12:36:01 22

22 大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源?本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構。我們

2021-12-09 13:36:13 7

7 需要門級驗證:FPGA 和 ASIC 一樣需要設計級驗證。但是,FPGA 在門級不是細粒度的,因此它們不需要門級驗證。您將每個門都放置在 ASIC 設計中,因此您需要驗證每個門。

2022-06-20 16:13:05 2184

2184

ASIC設計服務暨IP研發銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日發布FPGA-Go-ASIC驗證平臺。

2022-07-29 10:08:16 784

784 利用Systemverilog+UVM搭建soc驗證環境

2022-08-08 14:35:05 5

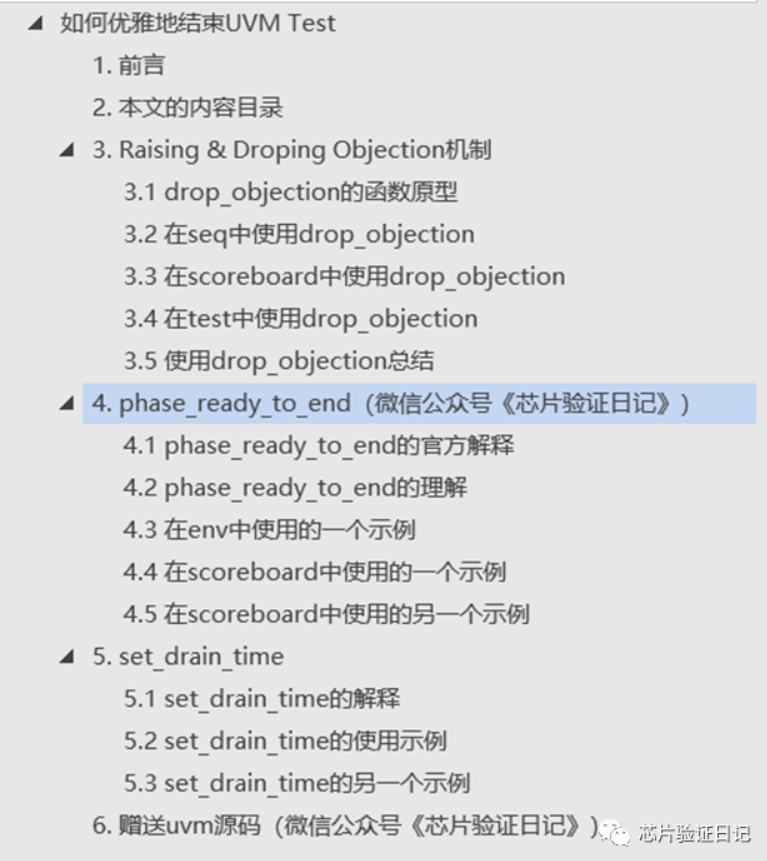

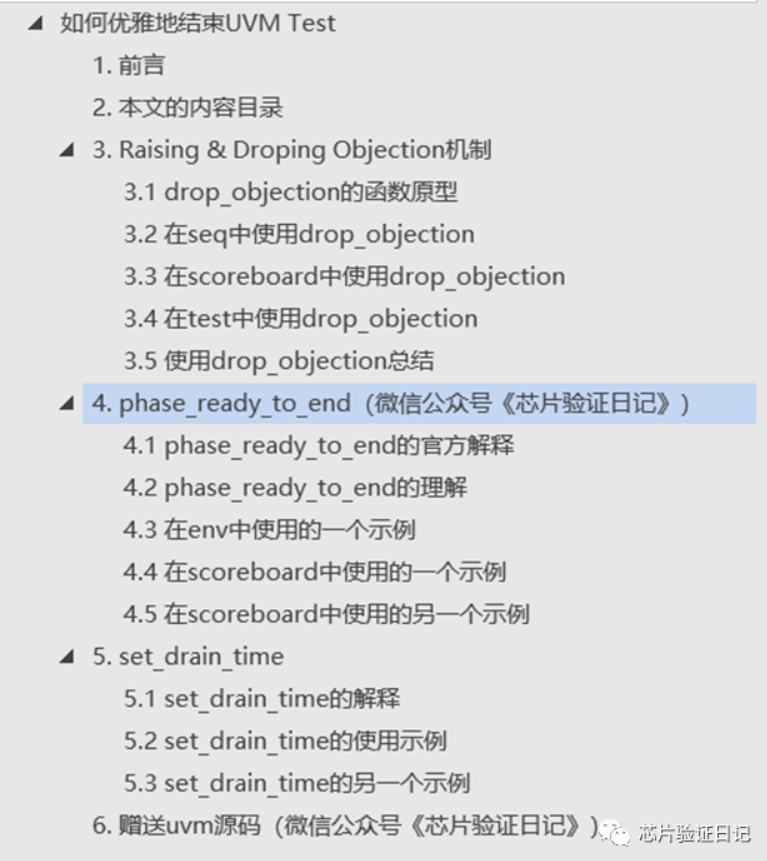

5 分享一下在UVM驗證環境中,結束仿真的幾種方式,不同結束仿真的方式適合不同的應用場景。

2022-12-17 11:23:54 1702

1702

因為DUT是一個靜態的內容,所以testbench理應也是靜態的,其作為uvm驗證環境和DUT的全局根結點。

2023-03-21 11:33:02 982

982 UVM environment**包含多個可重用的驗證組件,并根據test case的需求進行相應的配置。例如,UVM environment可能具有多個agent(對應不同的interface)、scoreboard、functional coverage collector和一些checker

2023-03-21 11:35:25 744

744

基于UVM搭建驗證環境和構造驗證激勵,調試的工作總是繞不開的。實際上,對驗證環境和激勵的調試,往往伴隨著驗證階段的前半程,并且會花掉驗證工程師很多時間和精力。

2023-04-06 09:36:03 428

428 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 以前看到不少驗證技術書籍都在說驗證環境中隨機怎么怎么好,然后為了隨機,UVM,SV 提供了什么什么支持。

2023-04-10 11:21:03 375

375 話說螺螄殼里做道場,UVM推出這么多年以來每年DVCon會議上總還是有人分享他們基于UVM package做的一些改動,使其能夠更適合項目的要求。

2023-04-13 18:13:09 1207

1207 在UVM中,transaction 是一個類對象,它包含了建模兩個驗證組件之間的通信所需的任何信息。

2023-05-24 09:17:32 1165

1165

driver應該派生自uvm_driver,而uvm_driver派生自uvm_component。

2023-05-26 14:38:46 824

824

如下圖所示,UVM中的TLM接口為組件之間Transaction的發送和接收提供了一套統一的通信方法。

2023-05-29 09:31:44 340

340

本文使用Easier UVM Code Generator生成包含多個agent和interface的uvm驗證環境。

2023-06-06 09:13:02 584

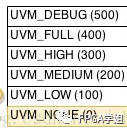

584 UVM預先定義了六個詳細程度; UVM_NONE到UVM_DEBUG。這些級別只不過是整數枚舉值

2023-06-06 12:33:26 2653

2653

uvm_do宏及其變體提供了創建、隨機化和發送transaction items或者sequence的方法。

2023-06-09 09:36:49 2588

2588

本次講一下UVM中的uvm_config_db,在UVM中提供了一個內部數據庫,可以在其中存儲給定名稱下的值,之后可以由其它TB組件去檢索。

2023-06-20 17:28:01 724

724 UVM提供了實現 **覆蓋驅動驗證(coverage-driven verification ,CDV)** 的框架。 CDV結合了自動測試向量生成,自檢查和覆蓋率收集,顯著地縮短了用于驗證設計時間。

2023-06-25 11:38:58 861

861

本次講一下UVM中的uvm_config_db,在UVM中提供了一個內部數據庫,可以在其中存儲給定名稱下的值,之后可以由其它TB組件去檢索。

2023-06-29 16:57:01 579

579 本篇是對UVM設計模式 ( 二 ) 參數化類、靜態變量/方法/類、單例模式、UVM_ROOT、工廠模式、UVM_FACTORY[1]中單例模式的補充,分析靜態類的使用,UVM中資源池的實現,uvm_config_db的使用。

2023-08-06 10:38:41 825

825

FPGA驗證和UVM驗證在芯片設計和驗證過程中都扮演著重要的角色,但它們之間存在明顯的區別。

2024-03-15 15:00:41 94

94

電子發燒友App

電子發燒友App

評論