德國慕尼黑,2022 年 6 月——可定制RISC-V處理器硅知識產(chǎn)權(quán)(IP)的領(lǐng)導(dǎo)者Codasip日前宣布,其Codasip Studio平臺現(xiàn)已支持蘋果公司macOS Monterey(當(dāng)前

2022-06-28 14:06:36 1037

1037

,RISC-V?嵌入式處理器IP的領(lǐng)先供應(yīng)商Codasip在捷克布爾諾和德國漢堡宣布,嵌入式電機和運動控制集成電路及微系統(tǒng)領(lǐng)域的全球領(lǐng)導(dǎo)者Trinamic選擇了Codasip的Bk3處理器用于其下一代產(chǎn)品系列。

2018-03-01 16:23:47 9764

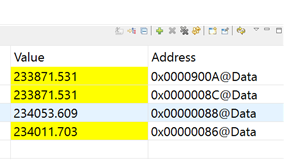

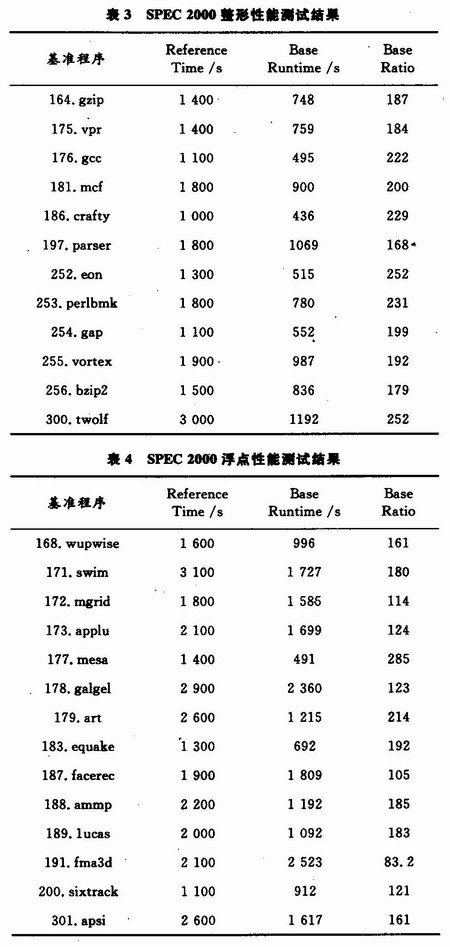

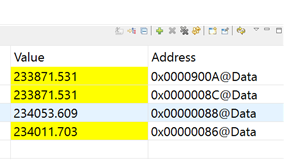

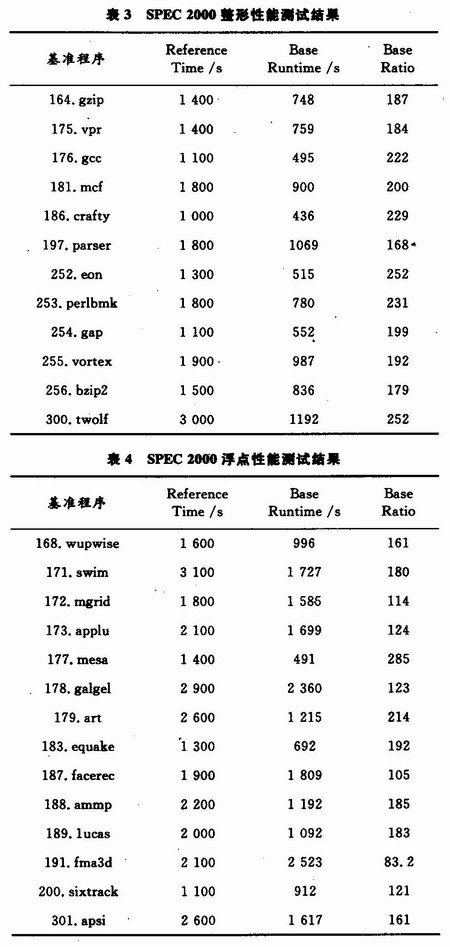

9764 C28x+FPU架構(gòu)的C2000微處理器在原有的C28x定點CPU的基礎(chǔ)上加入了一些寄存器和指令,來支持IEEE 單精度浮點數(shù)的運算。對于在定點微處理器上編寫的程序,浮點C2000也完全兼容,不需要

2018-03-07 08:57:35 10290

10290

德國慕尼黑,2022年5月——處理器設(shè)計自動化領(lǐng)域的領(lǐng)導(dǎo)性企業(yè)Codasip宣布:通過采用西門子集團(tuán)Siemens EDA的OneSpin?IC驗證工具,擴大了其形式驗證解決方案的可用工具范圍

2022-05-07 13:55:42 6483

6483

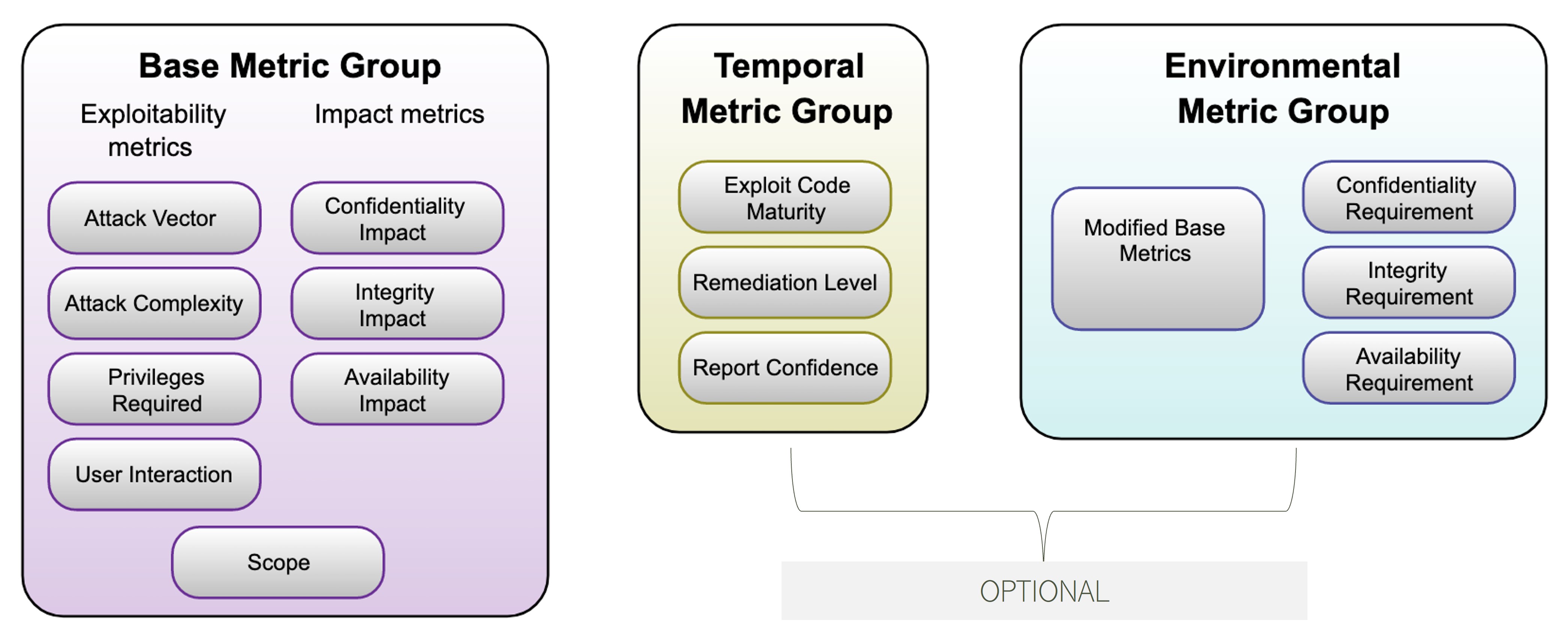

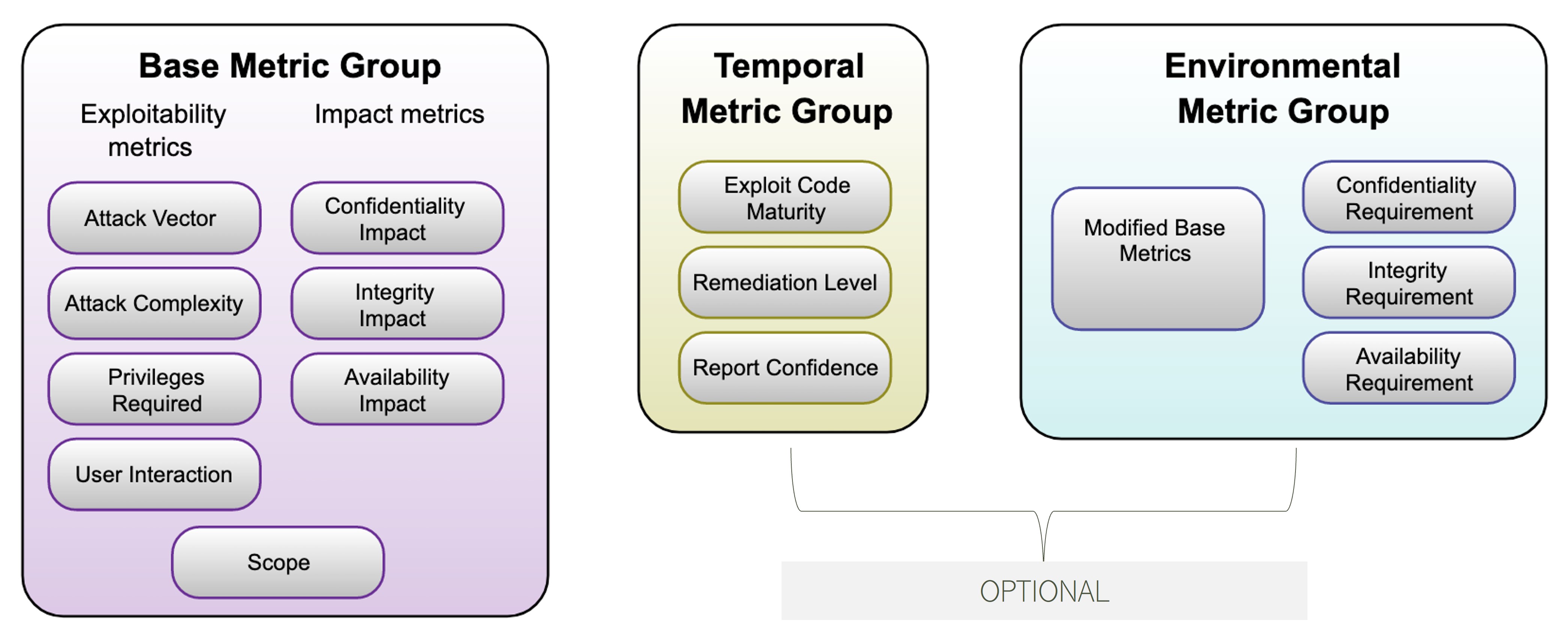

驗證處理器的安全性已成為現(xiàn)代電子系統(tǒng)設(shè)計中必不可少的步驟。用戶希望確保他們的消費類設(shè)備不會被黑客入侵,并且他們的個人和財務(wù)數(shù)據(jù)在云中是安全的。有效的安全驗證涉及處理器硬件和在其上運行的多層軟件

2023-03-16 10:47:01 7494

7494

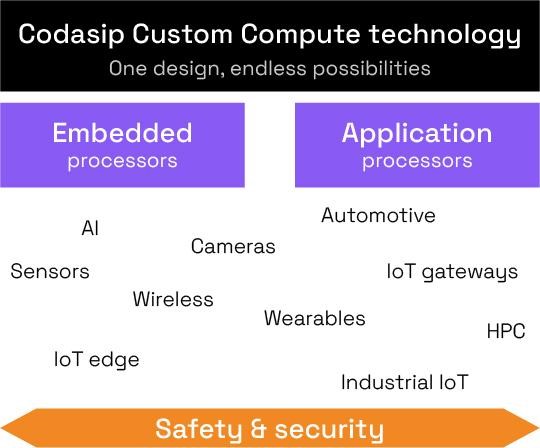

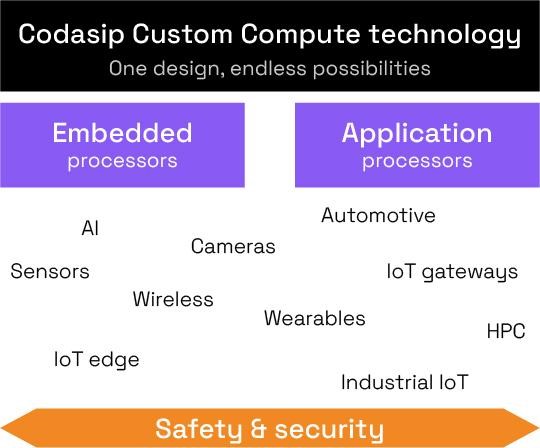

推出高度靈活的700系列,以實現(xiàn)無限創(chuàng)新 德國慕尼黑,2023年10月17日 ——RISC-V定制計算領(lǐng)域的領(lǐng)導(dǎo)者Codasip?今日宣布:推出一款全新的、高度可配置的RISC-V基準(zhǔn)性處理器系列

2023-10-24 17:25:33 339

339

嵌入式系統(tǒng)以各種類型的嵌入式處理器為核心,而隨著技術(shù)的發(fā)展,對于嵌入式處理器的性能及功耗的要求愈加嚴(yán)苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩(wěn)定

2019-07-19 08:29:10

處理器如何與外部設(shè)備通信?

2021-12-13 07:44:52

對于 T2080 處理器的預(yù)布局仿真,請共享 IBIS 文件(用于仿真 Hyperlynx SI)

2023-04-03 08:51:23

喜對于Virtex-6和用于FPGA的新7個系列,我沒有任何類型或硬處理器,為什么?有沒有計劃加入新的硬處理器,如果是這樣,什么樣的處理器?謝謝

2020-06-08 16:33:35

對于WL1837MOD的CPU的選擇,如果僅用一個ARM處理器來作為CPU可以嗎?該ARM處理器需要滿足什么功能?目前的ARM處理器,選擇哪款比較好呢?

希望大神們可以一一做出解答,萬分感謝!!!

2018-06-07 10:07:52

對于i.MX 8M Mini處理器,使用mscale ddr工具生成DDR校準(zhǔn)值的目的是什么?

我有一個運行 u-boot 的 i.MX 8M Mini 處理器。查看 u-boot 源代碼,我相信

2023-05-05 09:09:34

Cortex-M4內(nèi)核,Sitara AM57x處理器非常適用于那些不只需要單核性能的嵌入式應(yīng)用。這類集全部功能于一體的處理器賦予了靈活性全新的意義。AM57x處理器沒有幾乎相同的內(nèi)核,而是讓設(shè)計人

2018-09-04 09:54:55

ARM Cortex系列處理器――Cortex-AARM Cortex系列處理器——Cortex-MARM Cortex系列處理器——Cortex-R

2021-01-12 07:54:17

ARM cortex 處理器本身仿真要注意什么,uvm仿真時處理器本身arm提供驗證list嗎?

2022-08-05 14:14:40

ARM處理器中斷處理的編程是怎么實現(xiàn)的?

2021-04-27 06:46:53

ARM處理器狀態(tài)ARM微處理器的工作狀態(tài)一般有兩種,并可在兩種狀態(tài)之間切換:第一種為ARM狀態(tài),此時處理器執(zhí)行32位的字對齊的ARM指令;第二種為Thumb狀態(tài),此時處理器執(zhí)行16位的、半字對齊

2011-01-27 11:13:20

ARM處理器狀態(tài)ARM微處理器的工作狀態(tài)一般有兩種,并可在兩種狀態(tài)之間切換:第一種為ARM狀態(tài),此時處理器執(zhí)行32位的字對齊的ARM指令;第二種為Thumb狀態(tài),此時處理器執(zhí)行16位的、半字對齊

2011-01-27 14:19:05

ARM處理器模式和ARM處理器狀態(tài)有何區(qū)別?

2022-11-01 15:15:13

ARM處理器的節(jié)能優(yōu)勢綱 要許多嵌入式ARM處理器的系統(tǒng)都是基于電池供電的能量供應(yīng)方式,而處理器的功耗對于整個SoC芯片至關(guān)重要,因此ARM處理器的低功耗優(yōu)勢可以充分節(jié)省能量消耗。不過,除了處理器

2009-10-31 14:01:04

DSP處理器與通用處理器的比較1 對密集的乘法運算的支持GPP不是設(shè)計來做密集乘法任務(wù)的,即使是一些現(xiàn)代的GPP,也要求多個指令周期來做一次乘法。而DSP處理器使用專門的硬件來實現(xiàn)單周期乘法。DSP

2021-09-03 08:12:55

怎樣根據(jù)某些條件選擇DSP處理器的類型?比如:要求數(shù)據(jù)輸出時間間隔為1ms,速度數(shù)據(jù)類型為1個浮點型類型數(shù)據(jù)。急求大神指導(dǎo)!謝謝了!我對DSP處理器不太了解,暫時會用到這個技術(shù)。求指導(dǎo)!

2013-06-08 23:33:51

RK3399處理器與AR9201處理器有哪些不同之處呢?hi3559A處理器與RV1126處理器有哪些不同之處呢?

2022-02-21 07:29:27

“SHARC”是超級哈佛架構(gòu)(Super Harvard ARChitecture)的縮寫,是ADI公司為他們的浮點處理器起的名字。

2020-03-12 09:00:16

STM32內(nèi)核處理器好用嗎

2015-09-02 19:38:10

本文通過基于S3C44B0X處理器VxWorks嵌入式操作系統(tǒng)的BSP移植,詳細(xì)分析了VxWorks操作系統(tǒng)基于ARM處理器的中斷處理方法。

2021-04-27 06:28:03

為什么我的處理器漏電?

2021-03-02 08:19:38

先理清楚一些概念,然后我們再說下區(qū)別。什么是處理器?常常說的處理器,指的是CPU,擅長做計算,一般主頻用Ghz來計算,因為頻率很高,適合跑系統(tǒng),比如Linux。市面上常用的處理器有Intel AMD

2021-11-24 07:05:38

什么是MSP430多處理器?MSP430多處理器有哪些技術(shù)要點?

2021-05-27 06:52:20

嵌入式系統(tǒng)以各種類型的嵌入式處理器為核心,而隨著技術(shù)的發(fā)展,對于嵌入式處理器的性能及功耗的要求愈加嚴(yán)苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩(wěn)定

2019-07-05 07:52:22

我查看了TI的評估模塊的原理圖,看到前端處理器選用了MSP430作為DLPC的控制與解碼IT6801的控制,那么DLPC與IT6801芯片對前端處理器有什么特殊的要求嗎?可以用STM32代替MSP430處理器嗎?

2018-06-21 02:45:47

兼容jtag和sw調(diào)試接口的處理器的IR長度等信息,IR是什么,這里的處理器指的stm32嗎

2016-05-26 15:57:12

1、在AWS云中使用Arm處理器設(shè)計Arm處理器 Amazon Web Services (AWS) 宣布推出基于 Arm 的全新 AWS Graviton2 處理器,以及相關(guān)的第 6代

2022-09-02 15:55:27

階段的電流過大;第二,器件啟動異常;第三,最壞的情況會對處理器造成不可逆的損壞。可見,上下電時序對于確保系統(tǒng)的可靠運行起著重要的作用。

2019-10-18 07:53:02

多內(nèi)核是指在一枚處理器中集成兩個或多個完整的計算引擎(內(nèi)核),多核處理器是單枚芯片(也稱為“硅核”),能夠直接插入單一的處理器插槽中,但操作系統(tǒng)會利用所有相關(guān)的資源,將它的每個執(zhí)行內(nèi)核作為分立的邏輯

2019-06-20 06:47:01

普遍存在速度與處理級數(shù)的矛盾,有效解決此問題具有重要的現(xiàn)實意義。隨著片上系統(tǒng)(SOC)時代的到來,可編程邏輯器件不僅為FIR濾波器的設(shè)計提供了一條可行而高效的方法,而且更被廣泛地使用于數(shù)字信號處理

2019-07-30 07:22:48

電源電壓,但不具備延時功能。 2、如何確定微處理器復(fù)位閾值 如何正確地確定微處理器復(fù)位閾值,以及對于復(fù)位閾值精度的要求,常常沒有被正確地認(rèn)識。為了使設(shè)計者對于這個問題有一個更清楚的了解,我們以一

2020-07-08 09:46:44

ARM通過增加硬件協(xié)處理器來支持對其指令集的通用擴展,通過未定義指令陷阱支持這些協(xié)處理器的軟件仿真。簡單的ARM核提供板級協(xié)處理器接口,因此協(xié)處理器可作為一個獨立的元件接入。高速時鐘使得板級接口非常

2022-04-24 09:36:47

慮性能、實時能力和應(yīng)用靈活性的情況下,AM57x處理器也是更好的解決方案。工業(yè)以太網(wǎng)網(wǎng)關(guān)對于每個工業(yè)網(wǎng)絡(luò)都是不可或缺的,而性能與能夠可靠地將Gb以太網(wǎng)數(shù)據(jù)傳輸至工業(yè)網(wǎng)絡(luò)的實時能力也是必須的。全新

2018-09-04 10:07:50

微處理器的結(jié)構(gòu)是由哪些部分組成的?微處理器的代碼是如何執(zhí)行的呢?

2022-02-28 09:25:10

什么是信號處理器?信號處理器測試現(xiàn)狀如何?怎樣去提高信號處理器的測試性?

2021-05-10 06:55:08

1、STM32時鐘系統(tǒng)概述1.1 時鐘系統(tǒng)的概念與意義概念時鐘系統(tǒng)是由振蕩器(信號源)、定時喚醒器、分頻器等組成的電路。常用的信號源有晶體振蕩器和RC振蕩器。意義時鐘是嵌入式系統(tǒng)的脈搏,處理器內(nèi)核在

2021-08-12 07:16:57

我目前正在評估 iMXRT1062 處理器,現(xiàn)在正在尋找具有接近相同 I/O 和內(nèi)存特性但還支持 MMU 的處理器。也許有人可以就此提出建議。

2023-03-27 07:57:08

網(wǎng)絡(luò)處理器是什么?網(wǎng)絡(luò)處理器是由哪些部分組成的?有什么特點?網(wǎng)絡(luò)處理器產(chǎn)品現(xiàn)狀和應(yīng)用前景怎樣?

2021-05-28 06:48:48

基于XCVU440T的多核處理器多輸入芯片驗證板卡一、板卡概述 本板卡系北京太速科技自主研發(fā)的基于6U CPCI處理板,適用于多核處理器多輸入芯片驗證的應(yīng)用。芯片采用工業(yè)級

2022-02-25 10:23:05

14納米的ARM 處理器和14納米的X86移動處理器那個更省電??

2020-07-14 08:03:23

請問RISC處理器和ARM7處理器的區(qū)別在哪?求大神解答

2022-06-30 17:51:06

處理器相關(guān)的兩個問題,望哪位大神不吝指教下:1.是不是不帶FPU的處理器都是定點處理器啊? 比如定點數(shù)值信號處理器 C55XX系列的,比如51單片機,再比如RAM常用的Cortex-M3內(nèi)核處理器!2.對于定點處理器上面大神分享的經(jīng)驗是不是都通用的,還是根據(jù)編譯器而定的?

2019-05-13 01:09:48

面向多核處理器的低級并行程序驗證要 隨著多核處理器的廣泛使用以及人們對軟件提出了更高的可靠性要求,多核并行程序驗證的重要性日益凸顯。本文提出了一個完整的基于多核的并行程序驗證框架,該驗證框架包括抽象

2009-10-06 09:56:26

片上系統(tǒng)SoC(Sytem。n Chip),即是將整個系統(tǒng)集成在單個的芯片上。與傳統(tǒng)的板級電路不同,SoC集成的完整系統(tǒng)一般包括系統(tǒng)級芯片控制邏輯模塊、微處理器/微控制器CPU內(nèi)核模塊、數(shù)字信號

2019-08-30 08:27:15

片上系統(tǒng)SoC(Sytem。n Chip),即是將整個系統(tǒng)集成在單個的芯片上。與傳統(tǒng)的板級電路不同,SoC集成的完整系統(tǒng)一般包括系統(tǒng)級芯片控制邏輯模塊、微處理器/微控制器CPU內(nèi)核模塊、數(shù)字信號

2019-09-02 07:06:58

指令集作為微處理器軟件和硬件的分界線在計算機體系結(jié)構(gòu)中占有重要地位。測試程序自動生成(RTPG)是微處理器指令集驗證的主要方法之一。該文比較目前主流的RTPG 技術(shù)和驗證策略

2009-03-28 10:01:19 8

8 Tensilica 如何驗證處理器核心Tensilica 公司供稿由于半導(dǎo)體廠商不斷地將摩爾定律往前推進(jìn),系統(tǒng)單芯片(SoC)設(shè)計正陷入混亂的驗證泥潭。驗證工作在百萬門SoC 設(shè)計中所占

2009-12-19 08:26:24 10

10 摘要:在使用傳統(tǒng)的動態(tài)仿真方法對通用微處理器這樣大規(guī)模的設(shè)計進(jìn)行功能驗證時仿真速度成為了瓶頸,而使用FPGA物理原型驗證又不能提供很好的可調(diào)試性。本文主要介紹了基于

2010-06-07 11:20:54 0

0 什么是雙核處理器 什么是雙核處理器呢?雙核處理器背后的概念蘊涵著什么意義呢?簡而言之,雙核處理器即是基于單個半導(dǎo)體的一個處理器上擁有兩個一樣功能的處理器核

2006-10-12 09:47:11 17196

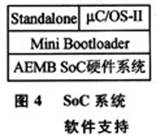

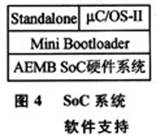

17196 AEMB軟核處理器設(shè)計的SoC系統(tǒng)驗證平臺

本文采用OpenCores組織所發(fā)布的32位微處理器AEMB作為SoC系統(tǒng)的控制中心,通過Wishbone總線互聯(lián)規(guī)范將OpenCores組織

2010-05-24 11:02:58 801

801

引言

自主研發(fā)高性能處理器芯片對于經(jīng)濟和國家安全方面具有重要意義。龍芯系列處理器的成功研制填補了我國自主研發(fā)高性能通用處理器的空白,龍芯2號采

2010-11-03 10:17:52 1672

1672

基于動態(tài)的RTL仿真依然是驗證超大規(guī)模集成電路的主要方法 在使用動態(tài)仿真方法對通用微處理器這樣大規(guī)模的設(shè)計進(jìn)行功能驗證時仿真速度成為了瓶頸#通常的解決方案是使用:.? 進(jìn)行硬

2011-06-28 17:09:13 40

40 本文利用Altera公司的FPGA開發(fā)工具對皋于國產(chǎn)龍芯I號處理器IP核的SoC芯片進(jìn)行ASIC流片前的系統(tǒng)驗證,全實時方式運行協(xié)同設(shè)計所產(chǎn)生的硬件代碼和軟件代碼,構(gòu)建一個可獨立運行、可現(xiàn)場

2012-04-21 15:22:01 3161

3161

基于OVM的32位微處理器驗證_吳勇昊

2017-03-17 08:00:00 3

3 性能驗證-ON-Intel的Xeon的處理器和Xeon的PHI-協(xié)處理器簇

2018-11-07 06:36:00 3607

3607 Codasip 科達(dá)希普公司詳細(xì)介紹 RISC-V處理器IP和處理器自動化設(shè)計工具領(lǐng)先供應(yīng)商 2014年始創(chuàng)于捷克科技重鎮(zhèn)布爾諾 10余年的大學(xué)科研是CODASIP的萌生之本 國際RISC-V基金會

2021-06-22 14:15:29 1654

1654 IAR Systems專業(yè)的開發(fā)工具IAR Embedded Workbench for RISC-V現(xiàn)已能夠支持Codasip的低功耗嵌入式處理器。

2021-12-02 13:46:59 1379

1379 Dave Higham作為ISO 26262道路車輛功能安全國際標(biāo)準(zhǔn)和安全方面的著名專家,將繼續(xù)推動Codasip去拓展定制處理器機遇。

2022-02-09 11:51:51 1380

1380

芯來科技將正式采用芯華章自主研發(fā)的新一代智能驗證系統(tǒng)穹景 (GalaxPSS)及數(shù)字仿真器穹鼎 (GalaxSim)等系列EDA驗證產(chǎn)品,加速新一代復(fù)雜RISC-V處理器IP的設(shè)計研發(fā)。

2022-03-03 10:32:25 1968

1968 德國慕尼黑 -?2022年4月—定制RISC-V處理器半導(dǎo)體知識產(chǎn)權(quán)(IP)領(lǐng)域的領(lǐng)導(dǎo)性企業(yè)Codasip日前宣布:已任命Jamie Broome先生為負(fù)責(zé)其全新汽車業(yè)務(wù)的副總裁。Broome

2022-04-25 16:02:34 1843

1843

? ?Codasip支持汽車制造商在創(chuàng)新和差異化能力方面實現(xiàn)突破 德國慕尼黑 - 2022年4月—定制RISC-V處理器半導(dǎo)體知識產(chǎn)權(quán)(IP)領(lǐng)域的領(lǐng)導(dǎo)性企業(yè)Codasip日前宣布:已任命Jamie

2022-04-25 16:05:57 3247

3247 Codasip 已在其 DV 測試平臺中包含 Imperas 黃金參考模型,以確保有效的驗證流程能夠適應(yīng)各種靈活的功能和選項,同時在未來內(nèi)核的整個路線圖中進(jìn)行擴展,以實現(xiàn)對功能質(zhì)量的嚴(yán)格確認(rèn)。

2022-06-01 10:11:36 847

847 功能支持Codasip的RISC-V處理器。在固件加載到Codasip處理器上時,Veridify的安全算法就會對其進(jìn)行驗證,以使RISC-V開發(fā)人員確信嵌入式系統(tǒng)是安全可用的。 Veridify的安全

2022-07-06 16:06:07 985

985 隨著Codasip Studio 9.2.0版本的發(fā)布,Codasip Studio新版本通過擴展和優(yōu)化等系列新功能賦能處理器設(shè)計自動化。

2022-09-14 17:21:13 942

942 可定制RISC-V處理器知識產(chǎn)權(quán)(IP)的領(lǐng)導(dǎo)者Codasip日前宣布:已任命胡征宇(Julian Hu)為該公司大中華區(qū)總經(jīng)理,以進(jìn)一步滿足區(qū)域內(nèi)客戶對可定制RISC-V處理器的強勁需求,并通過更完善的技術(shù)支持組織架構(gòu)來助力本地區(qū)客戶取得成功。

2022-10-20 09:43:49 687

687 在Codasip的驗證方法中使用智能隨機測試,使我們既能有針對性,又能廣泛地在這個新領(lǐng)域有效地找到更多的漏洞。這種測試方法包括調(diào)整測試,以更頻繁地激活觸發(fā)該漏洞的其他事件。

2022-11-01 10:08:20 399

399 SiliconArts光線追蹤解決方案將采用Codasip的RISC-V處理器內(nèi)核IP。Codasip Studio工具將支持客戶為其圖形應(yīng)用實現(xiàn)高度優(yōu)化。通過獲得Codasip完整的架構(gòu)授權(quán),SiliconArts從此項合作伙伴關(guān)系中獲得了充分的靈活性。

2022-11-03 11:21:14 557

557 SiliconArts光線追蹤解決方案將采用Codasip的RISC-V處理器IP。Codasip Studio工具將支持客戶為其圖形應(yīng)用實現(xiàn)高度優(yōu)化。

2022-11-04 12:06:14 471

471 “ Codasip通過收購Cerberus增強RISC-V的安全性能,而業(yè)界需要對RISC-V的安全性足夠重視 ” 2022年11月,德國慕尼黑 - 處理器設(shè)計自動化和可定制RISC-V處理器

2022-11-12 09:15:31 626

626 Codasip通過收購Cerberus增強RISC-V處理器設(shè)計的安全性 RISC-V的安全性問題需要得到高度重視 德國慕尼黑市,2022年11月 - 處理器設(shè)計自動化和RISC-V處理器硅知識產(chǎn)權(quán)

2022-11-16 19:37:05 486

486 來源:Codasip 德國慕尼黑,2022年12月7日——處理器設(shè)計自動化和RISC-V處理器IP的領(lǐng)導(dǎo)者Codasip今日宣布成立Codasip實驗室(Codasip Labs)。作為公司內(nèi)部創(chuàng)新

2022-12-09 15:55:58 452

452 Codasip成立Codasip實驗室以加速行業(yè)前沿技術(shù)的開發(fā)和應(yīng)用 日前處理器設(shè)計自動化和RISC-V處理器IP的領(lǐng)導(dǎo)者Codasip宣布成立Codasip實驗室(Codasip Labs)。作為

2022-12-09 18:23:01 3646

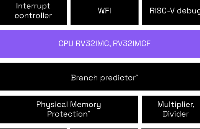

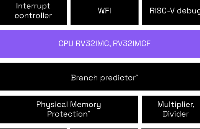

3646 在業(yè)界屢獲獎項的Codasip L31是一個小型、高效的32位嵌入式RISC-V處理器核,針對低功耗的AI/ML應(yīng)用,如物聯(lián)網(wǎng)邊緣設(shè)備等。憑借3級流水線、32個通用寄存器以及對谷歌

2023-02-28 10:45:30 390

390 處理器驗證是一個全新的領(lǐng)域。我們知道 Arm 和 Intel 對處理器質(zhì)量的期望設(shè)置了很高的標(biāo)準(zhǔn)。在 RISC-V 中,我們必須嘗試并遵循這一點。

2023-03-22 15:19:32 380

380 這種靈活性對于處理器IP來說雖然不太常見,但是可以使用Codasip IP來實現(xiàn)。所有的Codasip RISC-V內(nèi)核都是用一種叫做CodAL的高級語言設(shè)計的,并且可以用Codasip

2023-05-31 15:25:25 609

609

轉(zhuǎn)型RISC-V,大家才發(fā)現(xiàn)處理器驗證絕非易事。新標(biāo)準(zhǔn)由于其新穎和靈活性而帶來的新功能會在無意中產(chǎn)生規(guī)范和設(shè)計漏洞,因此處理器驗證是處理器開發(fā)過程中一項非常重要的環(huán)節(jié)。

2023-06-01 09:07:01 370

370

隨著RISC-V處理器的快速發(fā)展,如何保證其正確性成為了一個重要的問題。傳統(tǒng)的測試方法只能覆蓋一部分錯誤情況,而且無法完全保證處理器的正確性。因此,基于形式驗證的方法成為了一個非常有前途的方法,可以更加全面地驗證處理器的正確性。本文將介紹一種基于形式驗證的高效RISC-V處理器驗證方法。

2023-06-02 10:35:17 976

976 的客戶現(xiàn)在可以根據(jù)同一授權(quán)協(xié)議和合同去購買一系列精選的SmartDV外設(shè)IP的授權(quán)。這一合作伙伴關(guān)系支持使用Codasip RISC-V處理器的芯片設(shè)計人員,通過使用已驗證過兼容性和集成便捷性等特性

2023-07-03 16:13:04 464

464 在本文中,我們將以西門子EDA處理器驗證應(yīng)用程序為例,結(jié)合Codasip L31這款廣受歡迎的RISC-V處理器IP提供的特性,來介紹一種利用先進(jìn)的EDA工具,在實際設(shè)計工作中對處理器進(jìn)行驗證的具體方法。

2023-07-10 10:28:41 300

300

本板卡系我司自主研發(fā)的基于6U CPCI處理板,適用于多核處理器多輸入芯片驗證的應(yīng)用。芯片采用工業(yè)級設(shè)計。

2023-07-31 15:50:32 416

416

基于XCVU440-FLGA2892的多核處理器多輸入芯片驗證板卡為實現(xiàn)網(wǎng)絡(luò)交換芯片的驗證,包括四個FMC接口、DDR、GPIO等,板卡用于完成甲方的芯片驗證任務(wù),多任務(wù)功能驗證。

2023-08-24 10:58:23 476

476

RISC-V定制計算領(lǐng)域的領(lǐng)導(dǎo)者Codasip?宣布:公司現(xiàn)在可為其定制RISC-V處理器內(nèi)核提供Tessent? Enhanced Trace Encoder增強型追蹤編碼器解決方案,該方案

2023-09-12 09:03:25 407

407 RISC-V定制計算領(lǐng)域領(lǐng)導(dǎo)者 Codasip 今天宣布推出全新高度可配置的RISC-V基準(zhǔn)處理器系列,旨在實現(xiàn)無限創(chuàng)新。該"700家族系列"包括應(yīng)用和嵌入式處理器內(nèi)核。700

2023-10-18 10:03:55 320

320 2023年年尾最為重要的集成電路年會,Codasip作為銀牌贊助商向客戶和觀眾展示了其獨特的定制計算解決方案、新產(chǎn)品RISC-V處理器700系列以及Codasip Studio設(shè)計工具的獨到之處。 Codasip作為全球領(lǐng)先的RISC-V處理器IP核供應(yīng)商,我們在此次展會上再次證明了其在處理器的設(shè)計、開發(fā)和優(yōu)

2023-11-11 10:22:32 414

414

電子發(fā)燒友App

電子發(fā)燒友App

評論