1. 背景 這篇文章主要介紹了DDR3IP核的寫實現。 2. 寫命令和數據總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 5068

5068

和?x16 配置中均可提供高達?2133Mbps 的數據傳輸速率,并可與1.5V DDR3實現100%兼容。目前,華邦的?DRAM 產品布局包括1Gb-4Gb DDR3、128Mb-2Gb DDR

2022-04-20 16:04:03 2554

2554

DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數據率同步動態隨機存儲器)通常被我們稱為DDR,其中的“同步

2023-03-07 11:29:43 3207

3207

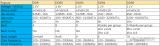

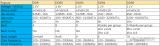

DDR內存1代已經淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 2871

2871

Cyclone II FPGA入門開發板DK-CYCII-2C20N提供集成功能,使用戶能夠開發和測試從簡單電路到各種多媒體項目的設計,無需實現復雜的應用編程接口(API),主機控制軟件,或SRAM / SDRAM /閃存控制器

2020-06-18 09:33:25

DDR2 SDRAM、DDR SDRAM 和 QDR II SRAM。外部存儲器件是各種圖像處理、存儲、通信以及通用嵌入式應用的一個重要的系統組件。1 Altera建議使用 Altera

2017-11-14 10:12:11

本帖最后由 mr.pengyongche 于 2013-4-30 02:58 編輯

Cyclone_II_EP2C20_原理

2012-08-11 09:25:37

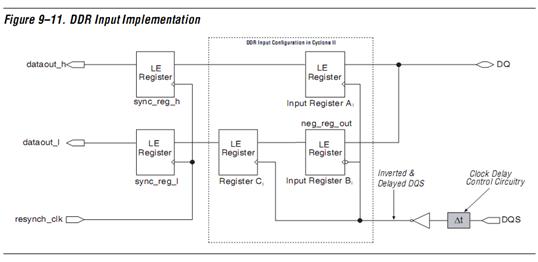

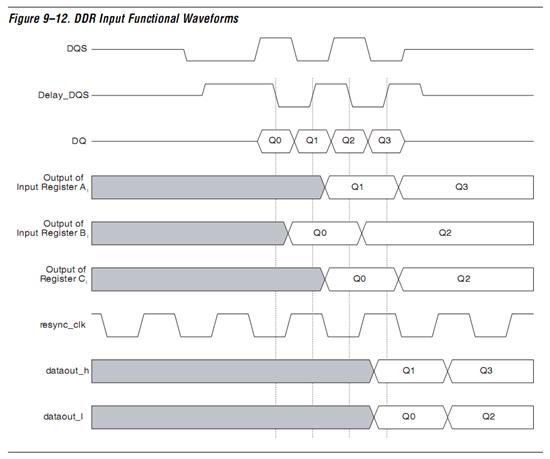

512Mb的DDR SDRAM設計,在Altera公司的Quartus Ⅱ4.2環境中采用Cyclone系列的FP1C6Q240C6來實現,總共使用了729個邏輯單元,占FPGA可編程邏輯資源的12%,此外還

2018-12-18 10:17:15

DDR SDRAM內存發展歷程

2021-01-06 06:04:22

DDR SDRAM訪問特性DDR控制器效率對比

2021-02-04 07:14:23

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

功率受信號線內阻影響大,是電壓平方關系,所以要盡量減少內阻,比如使用電平面,多打孔,縮短走線距離,高壓傳輸在終點用電阻分壓出較低電壓的信號等。SDRAM、DDR-I、DDR-II、 DDR-III信號

2010-03-18 15:33:07

SDRAM和DDR的具體區別是什么?

2021-06-18 07:58:51

更快、更大,每比特的功耗也更低,但是如何實現FPGA和DDR3 SDRAM DIMM條的接口設計呢? 關鍵字:均衡(leveling)如果FPGA I/O結構中沒有包含均衡功能,那么它與DDR

2019-04-22 07:00:08

是?A6.Quartus II v12.0 SP1Q7.Cyclone V Memory Controller的特性都有哪些?A7.1)最高支持400MHz硬核DDR3接口;2)最高支持300MHz軟核DDR3接口;3

2014-12-04 16:11:21

最近在設計一個需要連接DDR2 SDRAM的FPGA小系統,由于是第一次在使用SDRAM,在硬件連接時就遇到一個很糾結的問題——引腳的連接。看了幾種參考設計,發現有兩種說法:1、DDR2的數據(DQ

2017-09-25 17:51:50

Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產的型號為MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM為存儲器。用一個IP核完成

2011-05-03 11:31:09

基于Cyclone系列芯片DDR實現

2012-08-17 11:22:34

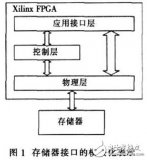

基于Xilinx FPGA的DDR2 SDRAM存儲器接口

2012-08-20 18:55:15

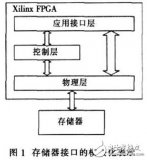

。本文結合筆者承擔的T比特路由器項目,對其中的大容量高速DDR內存接口的設計實現進行了詳細闡述。本文第2節對與DDR內存相關的知識做了簡單的介紹,從總體上對DDR內存有個認識;第3節闡述了DDR內存接口

2019-04-12 07:00:09

均衡的定義和重要性是什么如何實現FPGA和DDR3 SDRAM DIMM條的接口設計?

2021-05-07 06:21:53

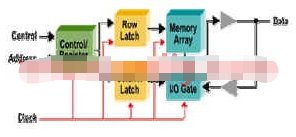

如何實現Reg istered SDRAM接口電路的設計?Reg istered SDRAM的工作原理是什么?Registered SDRAM接口電路的原理設計與布局布線規則是什么?

2021-04-12 07:10:21

嗨!我正在尋找Spartan-3A / 3ANFPGA入門KitBoard用戶指南(UG334)。具體來說第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因為例如這個內存

2019-07-31 06:18:10

嗨, 我使用的是XC6SLX45設備,其中我接口DDR SDRAM。在上面的FPGA器件中包含4個Bank。其中每個bank包含3或4個VREF引腳。通常在DDR SDRAM連接中,我們必須

2019-05-31 09:57:19

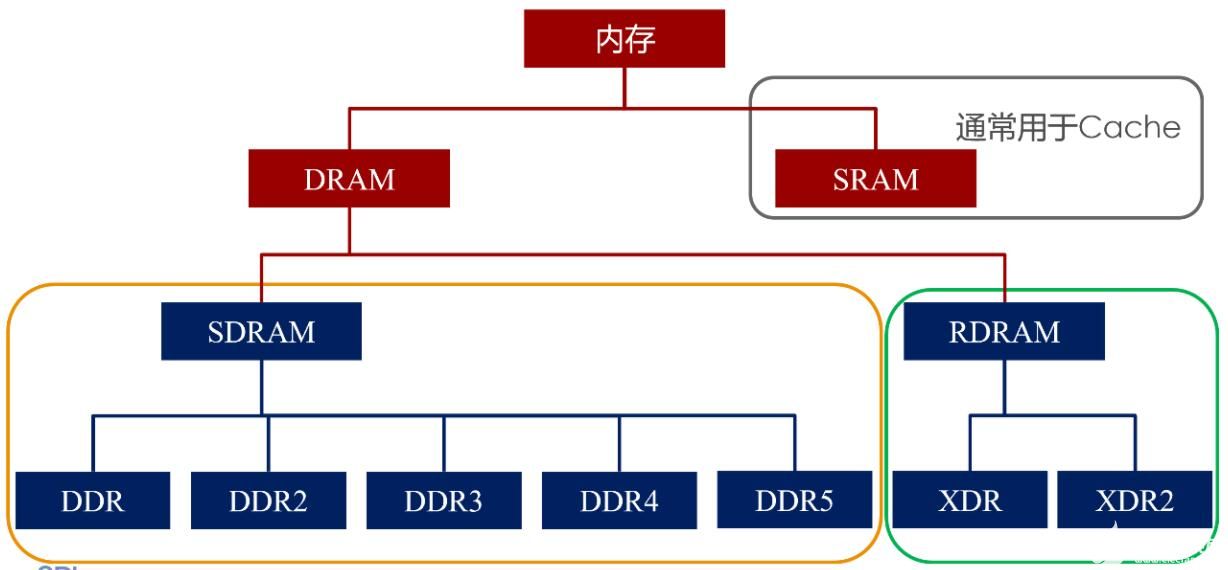

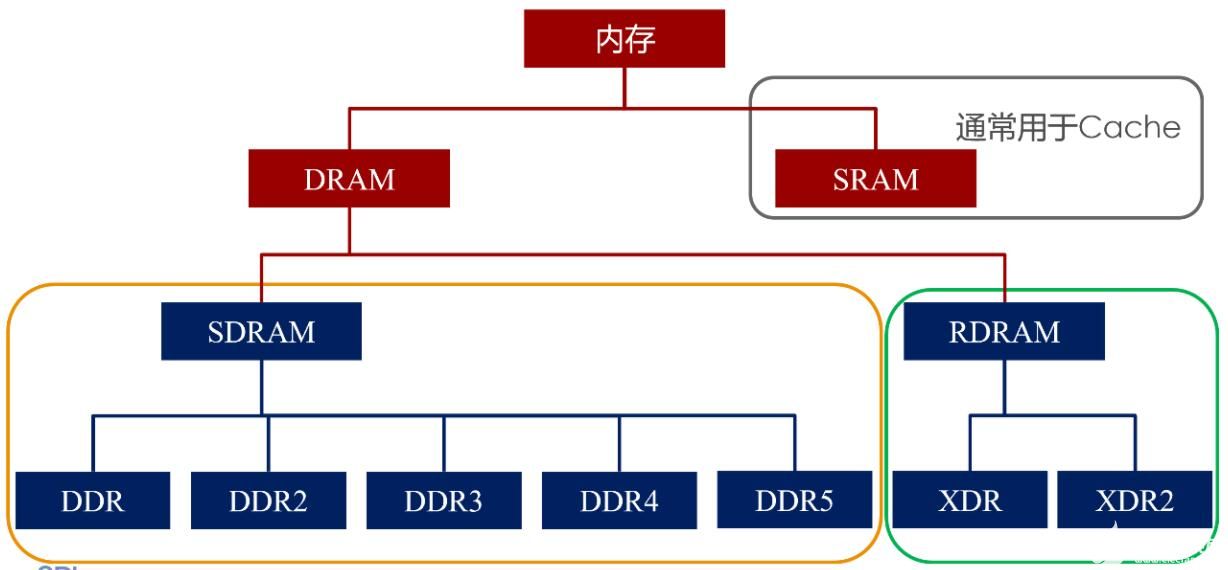

本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

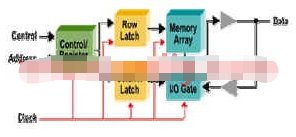

的時鐘雙沿讀寫嘛,速度這不就一下翻番了。很對,但是再往深入去,你思考過嗎?難道DDR內部尋址時數據也是雙沿讀寫么?非也DDR SDRAM外部的數據總線接口位寬,一般是8位或者16位。而它左邊那個紅圈里

2014-12-30 15:22:49

我需要在V7中實現與DDR3 SDRAM相同的功能和接口。這意味著命令/地址,讀取數據和寫入數據流的方向與MIG的方向不同。這可以實現嗎?

2020-07-14 16:18:04

設計分配DDR2所在Bank的輸出管腳時,建議采用Quartus II軟件自動分配,這樣才能更好地避免錯誤。圖4 FPGA Output Pad此外,還要注意:? 在Cyclone III系列的FPGA

2019-05-31 05:00:05

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 【關鍵字】DDR,時序,建立時間,保持時間,眼圖,邏輯分析儀,示波器【摘要】 DDR全名為Double Data Rate SDRAM ,簡稱為DDR。現在市場上的DDR已經發展到了DDR II,速度可以支持到667M

2008-12-13 20:15:07 15

15 DDR SDRAM is a 2n prefetch architecture with two data transfers perclock cycle. In the 2n prefetch

2009-03-28 14:43:47 56

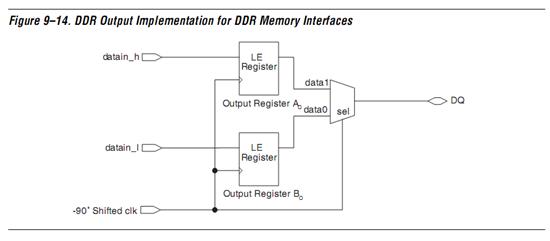

56 in the Virtex™-II architecture make it the perfectchoice for implementing a controller of a Double Data Rate (DDR) SDRAM. The D

2009-05-14 10:48:46 36

36 介紹基于現場可編程門陣列(FPGA),利用VHDL 語言設計實現MMC2107 與SDRAM 接口電路。文中包括MMC2107 組成結構、SDRAM 存儲接口結構和SDRAM 控制狀態機的設計。

2009-05-15 14:47:29 24

24 ref ddr sdram verilog源代碼

File/Directory Description

2009-06-14 08:48:01 82

82 =============================================doc DDR SDRAM reference design documentationmodel Contains the vhdl SDRAM model

2009-06-14 08:49:23 51

51 針對當今電子系統對高速大容量內存的需要,本文闡述了使用DDR 控制器IP 核來設計實現DDR內存接口的方法。該方法能使設計盡可能簡單,讓設計者更專注于關鍵邏輯設計,以便達到

2009-08-11 09:42:51 20

20 DDR2 SDRAM控制器的設計與實現

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設計方法!詳述了其基本結構和設計思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 SDRAM與DDR布線指南:ecos應用是與硬件平臺無關的,雖然開發板沒有涉及到SDRAM和DDR,不過,在某些高端平臺上使用ecos可能會遇到內存布線問題,為了完整敘述,這里一并給出說明。 很

2010-03-18 15:29:08 0

0 嵌入式測試和測量挑戰目錄引言3-4DRAM發展趨勢 3DRAM4-6SDRAM 6-9DDR SDRAM6DDR2 SDRAM 7DDR3 SDRAM 8DDR4 SDRAM 9GDDR 和LPDDR 9DIMMs 9-13DIMM 物理尺寸 9DIMM

2010-06-30 09:28:08 94

94 本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結構和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 不只計算機存儲器系統一直需要更大、更快、功率更低、物理尺寸更小的存儲器,嵌入式系統應用也有類似的要求。本應用指南介紹了邏輯分析儀在檢驗DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 本文將介紹DDR SDRAM的一些概念和難點,主要結合上一篇SDRAM的介紹加以對比。同時著重講解主流DDRII的技術。最后結合硬件設計提出一些參考。

DDR SDRAM全稱為Double Dat

2010-08-30 16:26:16 119

119 什么是DDR SDRAM內存

DDR是一種繼SDRAM后產生的內存技術,DDR,英文原意為“DoubleDataRate”,顧名思義,就是雙數據傳輸模式。之所以稱其為“雙”,也

2009-12-17 11:15:53 1646

1646 什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯合委員會)進行開發的新生代內存技

2009-12-17 11:17:59 623

623 DDR SDRAM內存

DDR SDRAM是Double Dat

2009-12-17 16:20:33 684

684 SDRAM 以其高速和大容量的優點獲得了極大的應用,但是其接口與目前廣泛應用的微處理器系統不兼容,介紹了用 VHDL 語言實現的SDRAM與RAM之間的接口控制電路,從而將SDRAM應用到微處理器

2011-06-01 15:29:15 57

57 文中在介紹DDR2的工作原理的基礎上,給出了一個用VHDL語言設計的DDR2 SDRAM控制器的方法,并且提出了一種在高速圖像處理系統中DDR2 SDRAM的應用方案,同時在Virtex-5系列的FPGA上得到了實現

2011-07-23 10:03:16 5102

5102 文章對適用DDR2 SDRAM控制器的結構、接口和時序進行了深入研究與分析,總結出一些控制器的關鍵技術特性,然后采用了自頂向下(TOP-IX)WN)的設計方法,用Verilog硬件描述語言實現控制器,

2011-09-01 16:36:29 174

174 雖然目前SDRAM內存條價格已經接底線,內存開始向DDR和Rambus內存過渡。但是由于DDR內存是在SDRAM基礎上發展起來的,所以詳細了解SDRAM內存的接口和主板設計方法對于設計基于DDR內存的主

2012-01-05 16:21:11 247

247 使用功能強大的FPGA來實現一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產的DDR2 SDRAM的存儲控制器,由于該公司出產的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 基于Xilinx的DDR2 SDRAM存儲控制器的用戶接口設計與仿真,本設計通過采用多路高速率數據讀寫操作仿真驗證,可知其完全可以滿足時序要求,由綜合結果可知其使用邏輯資源很少,運行速

2013-01-10 14:12:45 2990

2990 DDR SDRAM 全稱為Double Data Rate SDRAM,中文名為雙倍數據流SDRAM。DDRSDRAM 在原有的SDRAM 的基礎上改進而來。也正因為如此,DDR 能夠憑借著轉產成本優勢來打敗昔日的對手RDRAM,成為當今的主流

2013-09-13 15:17:30 210

210 ddr2_sdram 操作時序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 19

19 介紹在 Nios II 中利用 SDRAM 控制模塊實現對 SDRAM 存儲芯片——

K4M561633G 的讀寫,通過本章,你能學到

(1)SDRAM 控制模塊的使用。

(2)在 Nios II 中讀寫 SDRAM 芯片。

2015-12-14 15:40:33 0

0 DB31 Altera Cyclone II F672 電路板設計

2016-02-17 14:30:07 0

0 Altera Cyclone II F672

2016-02-17 15:13:08 0

0 DDR_SDRAM介紹和時序圖,DDR_SDRAM介紹和時序圖

2016-02-23 11:58:38 6

6 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設計VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 一種面向多核系統的DDR2SDRAM控制單元_章裕

2017-01-03 18:00:37 5

5 作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 Adrian Cosoroaba和Terry Magee在本月MemCon上給出了關于DDR4 SDRAM接口的詳細展示,該演示

2017-02-08 14:03:01 608

608 DDR2SDRAM控制器在機載顯控系統中的應用_孫少偉

2017-03-19 11:26:54 1

1 開發板,Cyclone_II_EP2C20_原理圖.part2

2017-03-19 11:45:23 14

14 DDR2_DDR3_SDRAM,PCB布線規則指導

2017-10-31 10:06:48 78

78 DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動態隨機存取內存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25152

25152 為了滿足高速圖像數據采集系統中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設計方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

在高速信號處理系統中, 需要緩存高速、大量的數據, 存儲器的選擇與應用已成為系統實現的關鍵所在。DDR SDRAM是一種高速CMOS、動態隨機訪問存儲器, 它采用雙倍數據速率結構來完成高速操作

2018-07-20 18:38:00 12744

12744

DRAM (動態隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統的存儲系統設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 2 協議,并遵從 JEDEC 標準 JESD79-2F (2009 年 11 月)的電氣接口來實現對外部存儲器總線接口的控制。組件包括帶可配置選項的 DDR SDRAM 控制器內核及 DDR 物理接口。

2018-05-30 09:29:00 7

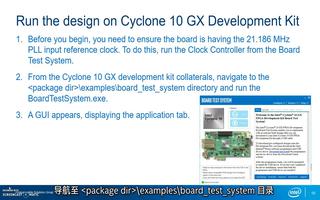

7 Cyclone 10 GX DDR3 示例設計的步驟

2018-06-20 00:12:00 5755

5755

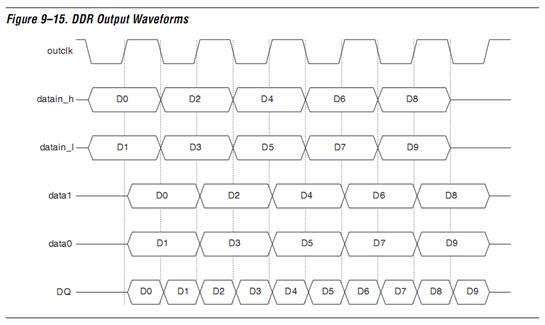

實現數據的高速大容量存儲是數據采集系統中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態機來描述對DDR SDRAM 的各種時序

2019-08-14 08:00:00 3401

3401

Xilinx Zynq-7000 SOC和7系列FPGA內存接口解決方案核心提供了到DDR3和DDR2 SDRAM、QDR II+SRAM、RLDRAM II/RLDRAM 3和LPDDR2 SDRAM的高性能連接。

2019-02-25 17:24:55 17

17 繼非常成功的第一代Cyclone?設備系列之后,Altera?Cyclone II FPGA將低成本的FPGA密度范圍擴展到68416個邏輯元件(LES),并提供多達622個可用I/O管腳和多達

2019-03-25 08:00:00 14

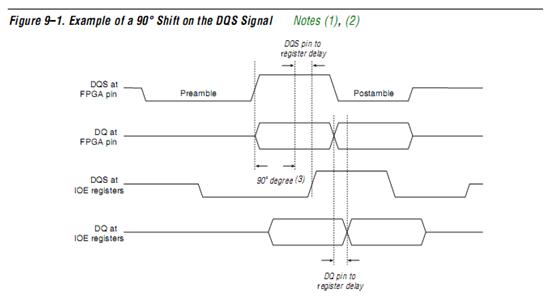

14 DDR2 設備概述:DDR2 SDRAM接口是源同步、支持雙速率傳輸。比如DDR SDRAM ,使用SSTL 1.8V/IO電氣標準,該電氣標準具有較低的功耗。與TSOP比起來,DDR2 SDRAM的FBGA封裝尺寸小得多。

2019-06-22 10:05:01 1793

1793

DDR5 是第五代 DDR SDRAM 的簡稱,DDR SDRAM 是英文 Double Data Rate SDRAM 的縮寫,中文譯為雙倍速率 SDRAM,而 SDRAM 又是

2020-02-03 18:30:59 5439

5439 DDR2 SDRAM采用雙數據速率結構實現高速運行。雙數據速率體系結構本質上是4n預取體系結構,其接口設計為在I/O球處每個時鐘周期傳輸兩個數據字。DDR2 SDRAM的單次讀寫操作有效地包括在內部

2020-05-21 08:00:00 1

1 DDR SDRAM是具有雙倍數據傳輸率的SDRAM,其數據傳輸速度為系統時鐘頻率的兩倍,由于速度增加,其傳輸性能優于傳統的SDRAM。DDR SDRAM 在系統時鐘的上升沿和下降沿都可以進行

2020-07-16 15:44:10 1938

1938 SDRAM從發展至今歷經了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM,SDRAM有一個同步

2020-07-24 14:25:27 719

719 DDR SDRAM的原理及特點:DDR SDRAM不需要提高時鐘頻率就能加倍提高SDRAM的速度,因為它允許在時鐘脈沖的上升沿和下降沿讀寫數據。至于地址和控制信號,還是跟傳統的SDRAM一樣,在時鐘的上升沿進行傳輸。

2020-08-10 17:33:21 603

603

SDRAM從SDR到DDR再到DDR2一路走來,又都產生了什么樣的變化,又都在哪些方面進行了改進,帶來了速度性能的進一步提升呢?

2020-09-26 11:47:34 10668

10668 。SDRAM可稱為SDRSDRAM。 DDR其實指的是DDRSDRAM,SDRAM及DDR主要差異有三點整理如下: SDRAM與DDR的主要差異

2021-02-22 15:35:48 3111

3111

本應用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實現的 DDR SDRAM 控制器。該實現運用了直接時鐘控制技術來實現數據采集,并采用自動校準電路來調整數據線上的延遲。

2021-03-26 14:42:41 4

4 本文首先分析了DDR SDRAM的基本特征,并提出了相應的解決方案詳細介紹了基于J EDEC DDR SDRAM規范的DDR SDRAM控制器設計方案。該控制器采用Verilog HDL硬件描述語言實現,并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 基于FPGA的DDR3SDRAM控制器設計及實現簡介(arm嵌入式開發平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設計及實現(嵌入式開發式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 DDR2總線的仿真方法,基于Agree公司最新的網絡處理器APP300和HY的

DDR2 SDRAM HY5PS121621。

2022-10-21 16:09:58 0

0 8Gb DDR4 SDRAM B裸片組織為128Mbit x 4 I/O x16banks或64Mbit x8 I/O x 16banks設備。此同步設備實現高達2666Mb/sec的高速雙數

2022-12-05 11:54:24 11

11 DDR3 SDRAM使用雙倍數據速率架構來實現高速操作。雙倍數據速率結構是一種8n預取架構,其接口經過設計,可在I/O引腳上每個時鐘周期傳輸兩個數據字。DDR3 SDRAM的單個讀或寫操作有效地包括

2023-02-06 10:12:00 3

3 DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數據率同步動態隨機存儲器)通常被我們稱為DDR

2023-03-07 11:33:57 1653

1653 如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用戶手冊

2023-04-27 20:25:40 6

6 SDRAM與DDR布線指南

2022-12-30 09:20:50 10

10 JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2

?

? ?

? ?

? ?

? ?

? ?

? ?

? 電子發燒友App

電子發燒友App

評論