完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > Cadence

鏗騰電子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一個專門從事電子設計自動化(EDA)的軟件公司,由SDA Systems和ECAD兩家公司于1988年兼并而成。是全球最大的電子設計技術(Electronic Design Technologies)、程序方案服務和設計服務供應商。其解決方案旨在提升和監控半導體、計算機系統、網絡工程和電信設備、消費電子產品以及其它各類型電子產品的設計。

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布擴大與三星晶圓代工廠的合作,包括簽署一項新的多年期

為了滿足高復雜度半導體芯片設計中面臨的時間節點緊迫、設計目標極具挑戰性以及設計專家短缺等諸多挑戰,Cadence 推出

新思科技(Synopsys)、西門子、楷登電子(Cadence)三大巨頭恢復對華EDA銷售

新思科技(Synopsys)、西門子、楷登電子(Cadence)三大芯片設計軟件巨頭正式恢復對華供貨;意味著美國已正式取

本文中,Priya 和 Gopi 分享了如何使用集成到 Allegro X Design 平臺的 Sigrity X A

? ?在使用Allegro軟件進行PCB設計的過程中,我們可能會遇到一個問題,那就是該軟件并不支持直接放置中文字符,它僅

大家是否想過,我們的智能手機為何能夠拍攝出令人驚嘆的照片、播放清晰悅耳的音樂或是準確測量心率?

汽車行業正在經歷一場前所未有的深刻變革,未來的汽車不再僅僅是交通工具,而是精密的軟件定義汽車(SDV)。

Kao Data與Cadence合作驗證數據中心間接蒸發冷卻設計

Kao Data 計劃在占地 36 英畝的園區內建立四個數據中心,目前已完成其中一個,即 KDL1 數據中心,這是英國第

Inphi借助Cadence技術完成7nm全芯片扁平化設計流片

Inphi 是高速數據移動互連領域的領導者,致力于在全球范圍內、數據中心之間以及數據中心內部快速傳輸大數據。

Cadence Conformal AI Studio助力前端驗證設計

Cadence 推出最新的前端驗證設計方案 Conformal AI Studio,專為解決日益復雜的前端設計挑戰而打造

鏗騰電子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一個專門從事電子設計自動化(EDA)的軟件公司,由SDA Systems和ECAD兩家公司于1988年兼并而成。是全球最大的電子設計技術(Electronic Design Technologies)、程序方案服務和設計服務供應商。其解決方案旨在提升和監控半導體、計算機系統、網絡工程和電信設備、消費電子產品以及其它各類型電子產品的設計。

電話: 86.21.61222300

傳真: 86.21.60312555

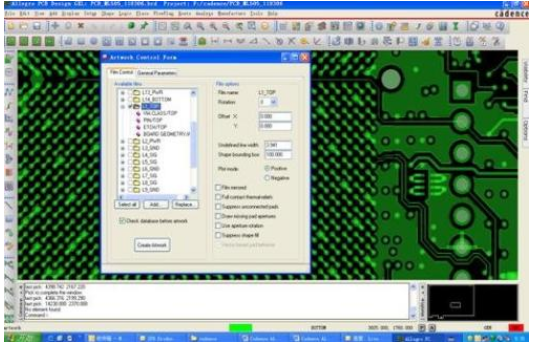

Cadence Allegro系統互連平臺能夠跨集成電路、封裝和PCB協同設計高性能互連。應用平臺的協同設計方法,工程師可以迅速優化I/O緩沖器之間和跨集成電路、封裝和PCB的系統互聯。該方法能避免硬件返工并降低硬件成本和縮短設計周期。約束驅動的Allegro流程包括高級功能用于設計捕捉、信號完整性和物理實現。由于它還得到Cadence Encounter與Virtuoso平臺的支持,Allegro協同設計方法使得高效的設計鏈協同成為現實。

AD PCB封裝轉Allegro封裝或者AD PCB轉Allegro PCB

AD封裝轉ALLEGRO封裝時,要把所有封裝放到一張PCB上或者分批次的放到PCB上,把PCB轉成ALLEGRO格式的,然后再用ALLEGRO導出PCB封裝

Cadence allegro與Altium等軟件的區別比較分析

現在推Altium Designer。國內低端設計的主流,國外基本沒人用。簡單易學,適合初學者,容易上手;占用系統資源較多,對電腦配置要求較高。在國內使...

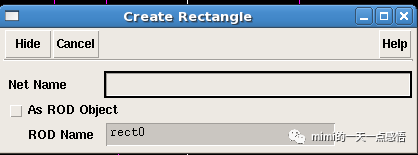

Cadence Virtuoso版圖設計工具之Virtuoso基本操作方法

創建矩形命令用于創建矩形。當創建一個矩形時,按F3會出現選項來對矩形進行命名。其中,“Net Name”為對所創建的矩形進行命名

Altium Designer原理圖PCB轉換到cadence的方法(一)

今天和大家分享一個詳細的AD(altium designer21)軟件的原理圖和PCB轉化為cadence 17.4【orcad和allegro】的圖文...

2008-07-12 標簽:cadence 0 6405

Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設計的方方面面。包括ASIC 設計,FPGA 設計和PCB 板設計。與眾所周知的EDA 軟件...

2017-12-04 標簽:cadence 7.5萬 0

2019年全球半導體IP市場總價值達39.4億美元 全球TOP10廠商排名出爐

2019年全球半導體IP市場總價值約為39.4億美元,比2018年的37.4億美元增長了5.2%。考慮到半導體市場在2019年下降了約15%,且IP特許...

Cadence設計系統公司創造了芯片制造商用于設計芯片的軟件以及這些芯片制造商可以納入其產品設計的知識產權IP,該公司今日發公告稱將計劃與NI達成一項收...

Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設計的方方面面,包括ASIC 設計、FPGA 設計和PCB 板設計。Cadence 在仿真、...

Cadence全新Tensilica Vision Q6 DSP IP助力提升視覺與AI性能

楷登電子今日正式推出Cadence? Tensilica? Vision Q6 DSP。該DSP基于速度更快的新處理器架構,面向嵌入式視覺和AI技術量身...

Cadence發布Cadence Sigrity 2018版本,可幫助設計團隊進一步縮短PCB設計周期

美國Cadence公司近日宣布發布Cadence Sigrity 2018版本,該版本包含最新的3D解決方案,幫助PCB設計團隊縮短設計周期的同時實現設...

Cadence Tensilica Vision P6 DSP 助力AI和視覺應用性能提升

現代智能邊緣設備和智能手機需要愈加復雜且豐富的圖像處理功能,以及基于AI的功能。先進的視覺和AI技術利用單攝像頭即可實現焦外成像,同時降低功耗和成本。V...

Cadence + Tensilica,強強聯合能否締造IP領域新機遇?

Cadence全球資深副總裁黃小立指出,在高速布局的接口上已然完成后,Cadence又開始對高速數據處理有著濃厚的興趣。Tensilica就是Caden...

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |