完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > verilog

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

文章:708個 瀏覽:111854次 帖子:936個

需要手工在 C++ 代碼里明確指定可并行執(zhí)行的任務(wù)(用 task,添加頭文件 hls_task.h),同時可并行執(zhí)行的 task 接口(對應(yīng) C++ 函...

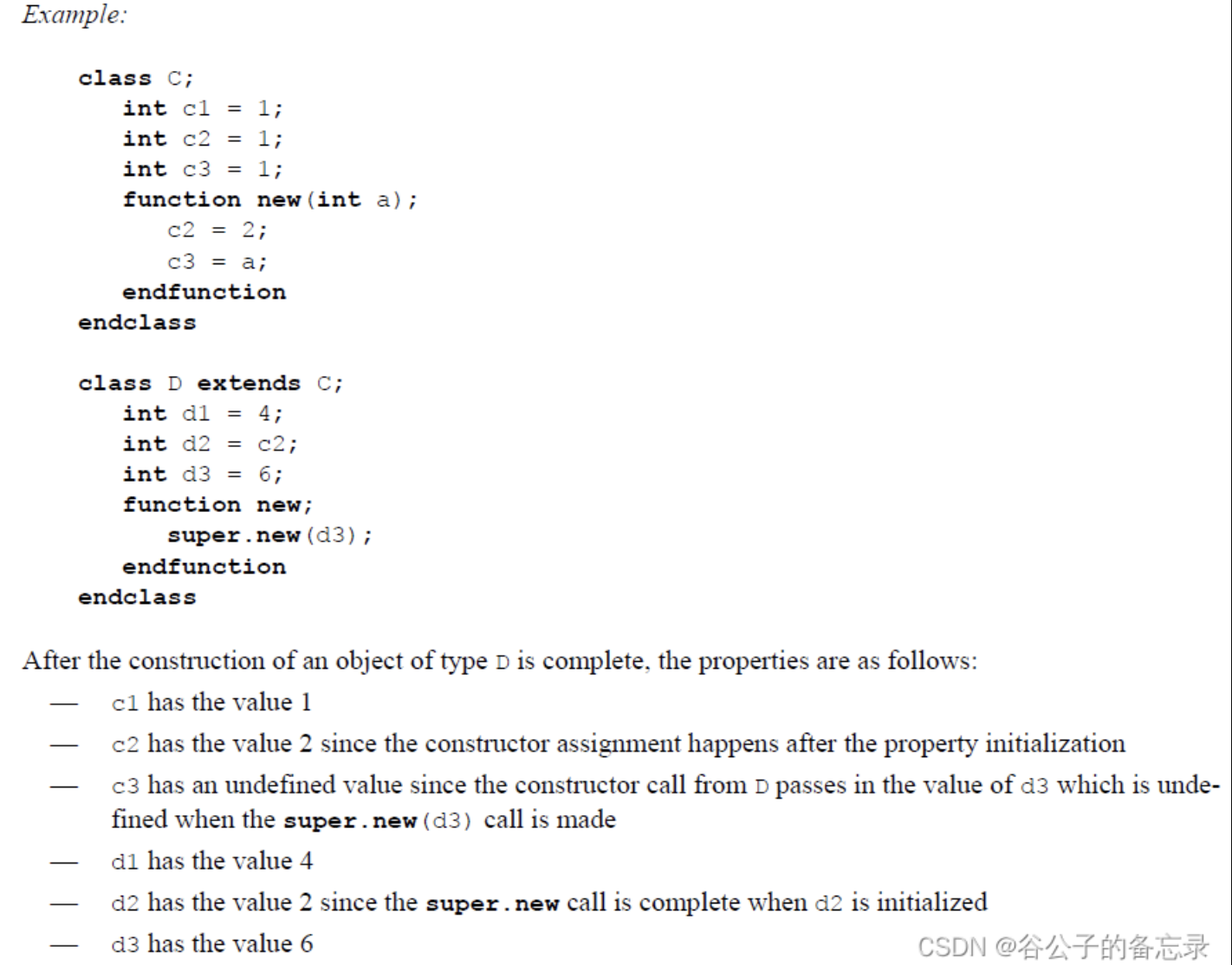

class里面包含data和對data進(jìn)行操作的subroutines(functions and tasks)。class的data稱為class p...

2023-05-24 標(biāo)簽:Verilog 941 0

System Verilog中的Bits與Bytes是等價的嗎

正如我們所知,“bit”是無符號的,而“byte”是有符號的。那么,你認(rèn)為下面兩個聲明是等價的嗎?

2022-10-26 標(biāo)簽:Verilog 936 0

UART協(xié)議由三根線組成,Tx,Rx,Gnd即發(fā)送、接收與地,不包含時鐘線,屬于全雙工異步串行通信協(xié)議。

SystemVerilog coding過程中你在哪里聲明臨時變量

眾所周知,語句塊中需要用到的變量只能在語句塊最開始定義。

Verilog 與 ASIC 設(shè)計的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog與ASIC設(shè)計的關(guān)系 Verilog作為一種硬件描述語言(HDL),在ASIC設(shè)計中扮演著至關(guān)重要的角色。ASIC(Application...

UVM中add_typewide_sequence和add_sequence的區(qū)別

第2和第3種方式類似,第3種是一下子添加多個sequence,它內(nèi)部原理就是調(diào)用第2種的函數(shù),因此在本質(zhì)上,只有第1和第2種這兩類區(qū)別。

大端,最高字節(jié)存儲在最低的內(nèi)存地址,小端則是最低有效字節(jié)存儲在最低的內(nèi)存地址。在Verilog中實(shí)現(xiàn)大端(Big-Endian)和小端(Little-E...

調(diào)制解調(diào)verilog程序開發(fā)需求

功能需求:開發(fā)調(diào)制解調(diào)verilog程序。要求數(shù)據(jù)上行速率1.25Gbps以上。下行速率較低,100M以上即可。程序包括:發(fā)射調(diào)制(數(shù)據(jù)編碼等)、接收解...

2023-08-30 標(biāo)簽:調(diào)制解調(diào)無線通信Verilog 889 0

如何高效替換Soft IP中的標(biāo)準(zhǔn)cell

我們在購買soft IP的時候,vendor提供的是通用的verilog/system verilog的代碼,而在不同的項(xiàng)目中,我們采用的工藝不一樣,因...

虛擬接口不支持多態(tài)性,因?yàn)樗鼈兣c靜態(tài)設(shè)計元素相關(guān)聯(lián)。但是,SystemVerilog 類確實(shí)支持多態(tài)性,這一事實(shí)可用于創(chuàng)建接口訪問器類。

基于SystemVerilog的驗(yàn)證引入了接口的概念來表示設(shè)計模塊之間的通信。在其最基本的形式中,SystemVerilog 接口只是一個命名的信號束,...

SystemVerilog有兩種類型的數(shù)組:壓縮數(shù)組和非壓縮數(shù)組。壓縮數(shù)組是連續(xù)存儲的位的集合,通常稱為向量。非壓縮數(shù)組是網(wǎng)絡(luò)或變量的集合。

2023-02-09 標(biāo)簽:網(wǎng)絡(luò)VerilogSystem 876 0

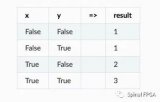

無論是SystemVerilog還是SpinalHDL,都有Last valid assignment wins的語法特征。如在SpinalHDL-Do...

2023-11-04 標(biāo)簽:VerilogCache狀態(tài)機(jī) 855 0

SystemVerilog中的Unpacked Unions

unpacked union中各個成員的大小可以是不同的。

SystemVerilog中的Virtual Methods

SystemVerilog中多態(tài)能夠工作的前提是父類中的方法被聲明為virtual的。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |