簡介

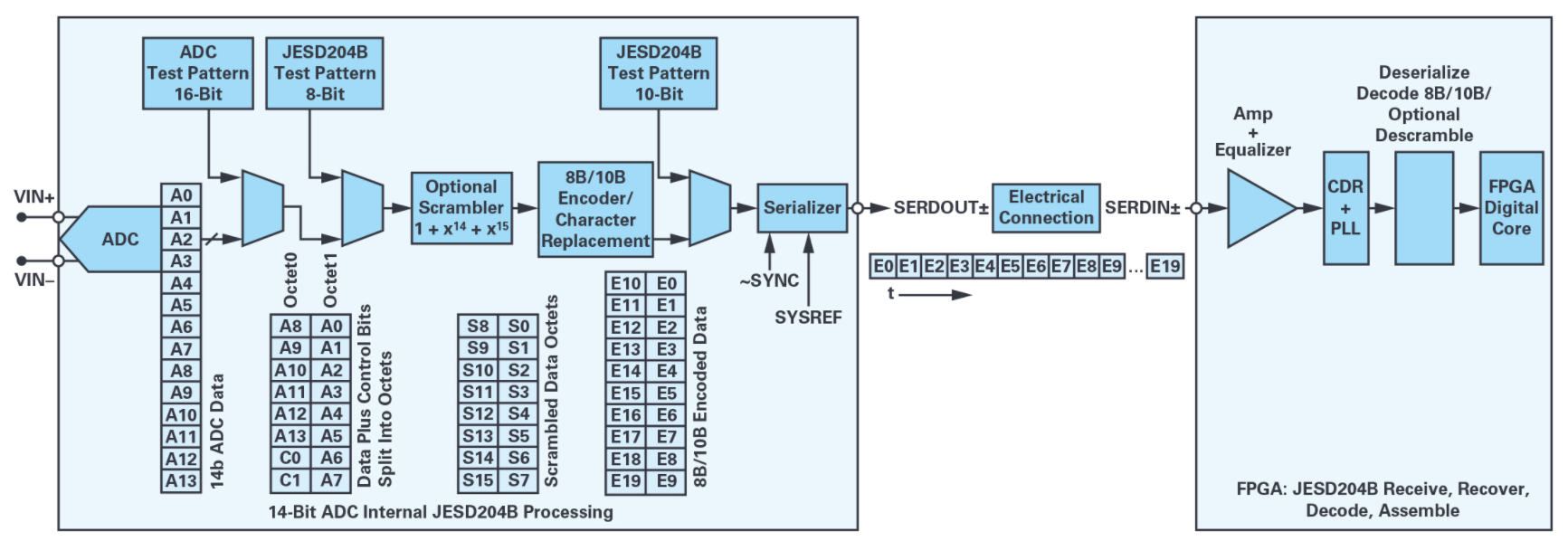

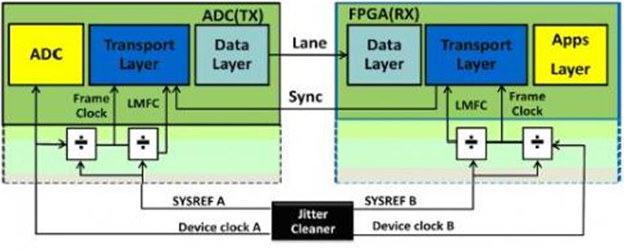

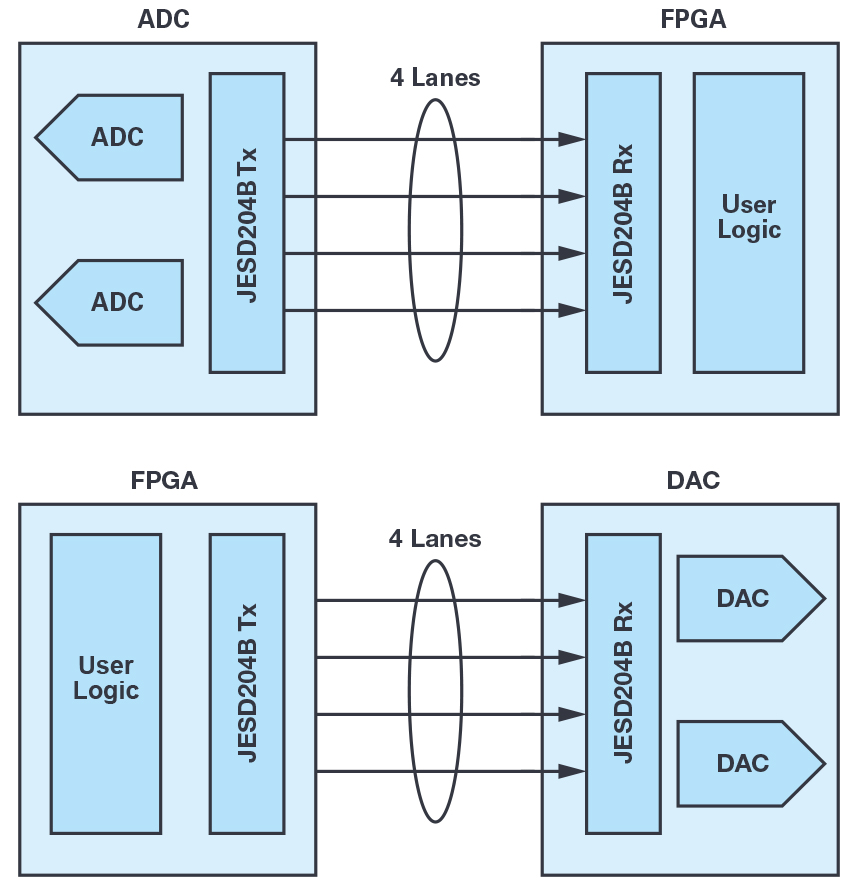

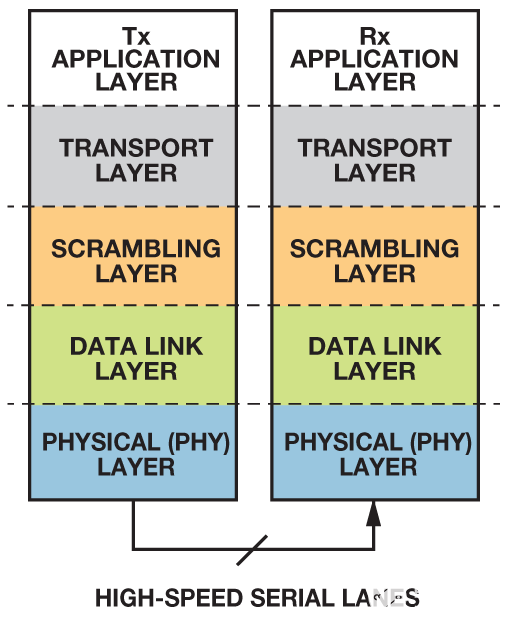

隨著高速ADC跨入GSPS范圍,與FPGA(定制ASIC)進行數據傳輸的首選接口協議是JESD204B。為了捕捉頻率范圍更高的RF頻譜,需要寬帶RF ADC。在其推動下,對于能夠捕捉更寬帶寬并支持配置更靈活的SDR(軟件定義無線電)平臺的GSPS ADC,高速串行接口(在此情況下既JESD204B)是必不可少的。JESD204B標準是一種分層規范,了解這一點很重要。規范中的各層都有自己的功能要完成。應用層支持JESD204B鏈路的配置和數據映射。傳輸層實現轉換樣本與成幀未加擾八位字之間的映射。加擾層可以選擇性地獲取八位字并進行加擾或解擾,以便通過延展頻譜尖峰來降低EMI效應。加擾在發送器中完成,解擾在接收器中完成。在數據鏈路層中,可選加擾的八位字編碼成10位字符。該層也是產生或檢測控制字符的地方,目的是監視和維護通道對齊。物理層即串行器/解串器(SERDES)層,負責以線路速率發送或接收字符。該層包括串行器、驅動器、接收器、時鐘和數據恢復電路。圖1顯示了這些層在JESD204B中的安排。為了更好地理解該規范,詳細闡釋各層對了解ADC樣本如何映射到8B/10B串行字是有好處的。

?

圖1. 通過JESD204B各層的簡化數據流

應用層

通過應用層可以實現特殊用戶配置,以及將采樣數據映射到典型JESD204B規范之外。這樣便能更有效地使用該接口來降低功耗并獲得其它好處。必須注意:發送器(ADC)和接收器(FPGA)均須采用此類特殊配置。接收器和發送器必須以相同方式進行配置,以便正確傳輸和解讀數據。對于需要以不同于N'(每個樣本傳輸的位數)的樣本大小傳輸數據的ADC,以獨特方式配置應用層可能有利。可以將多個樣本重新包裝,從而降低通道速率,提高鏈路整體效率。

傳輸層

讓我們仔細看看JESD204B規范的傳輸層。傳輸層接受ADC樣本并添加信息(填充)以產生半字節組(通常在4位邊界上)。此信息以結束位或控制位的形式提供,是有關所傳輸數據的附加信息。傳輸層將這些半字節組安排為幀。必須注意:傳輸層以并行數據將這些樣本提供給數據鏈路。并行數據總線的寬度由成幀器結構決定,單字節為8位,雙字節為16位,以此類推。此時的數據流尚未達到串行器。

一個ADC可以映射到一個單通道鏈路,或者映射到一個多通道鏈路。這種配置能力對于寬帶RF應用中使用的GSPSADC特別方便,在此類應用中,采樣速率決定是否使用多個通道,以便符合對通道速率的限制。若同一器件中有M個ADC,也可以將多個轉換器映射到多個通道。這些ADC可以映射到一個單通道鏈路,或者映射到一個包括L個通道的多通道鏈路。某些情況下,一個ADC可能需要多個通道。這要由給定ADC的最大通道速率來決定。例如,12位、2.5 GSPS AD9625的最大通道速率為6.5 Gbps。這意味著當N'等于16時,總共需要8個通道。有時候,通道速率可能受到系統中的FPGA限制。對于在RF應用中使用GSPSADC的客戶,成本可能是設計考慮之一。為了降低成本,可以使用通道速率較低的FPGA。例如,14位、1.0 GSPS雙通道AD9680的最大通道速率為12.5 Gbps。AD9680有4個輸出通道,可配置抽取來降低采樣速率,從而降低通道速率。這對于特定RF應用有兩個作用:一是降低通道速率,二是帶寬選擇。

現在回到JESD204B參數,N'參數指定JESD204B字大小。轉換器采樣分辨率被分解成4位半字節。14位轉換器和16位轉換器分別有4個半字節,而12位轉換器有3個半字節。如果AD9625的N'設置為12,則所需通道數可以減少2個,有6個通道便可使通道速率小于6.5 Gbps。建議將轉換樣本數(S)映射到4位半字節邊界上的JESD204B字中。圖2顯示了ADC樣本數到串行通道的映射。它已經參數化,支持許多可以利用JESD204B實現的潛在情況。

N'參數等于半字節數量乘以4。將轉換器的N'設為16,分辨率范圍設為8位至16位,對于發射器和接收器都是有益的。這允許將相同的發射器和接收器用于多個轉換器,從而簡化了整體系統設計。不完整的半字節有空間可用于JESD204B標準定義的控制位(CS)或結束位(下面的圖2中顯示為TT)中。必須滿足公式N' = N + CS + T。如有控制位,其附于每個轉換器樣本的LSB之后。在使用轉換器數量、每幀采樣數量、JESD204B字大小和最大通道速率來計算通道數量后,我們就可以確定每幀所發送的八位字數量F。可采用下面的公式來確定該參數:F = (M × S × N')/(8 × L)。有關JESD204鏈路參數的更多信息,請參閱參考文獻1,其中對鏈路參數做了更詳細的說明。另有一個分為四部分的在線研討會,它從傳輸層開始,提供了有關JESD204標準的進一步信息。

?

圖2. 傳輸層ADC樣本映射

傳輸層根據給定器件已定義的鏈路配置參數,決定如何包裝來自ADC的數據。這些參數在初始通道對齊序列(ILAS)期間從ADC傳輸到FPGA。這些設置通過串行端口接口(SPI)配置,其設置ADC和FPGA上的寄存器值來定義鏈路配置參數。根據這些參數產生一個校驗和并將其傳輸給接收器,以便接收器(FPGA)能夠驗證鏈路配置參數是否正確接收。通過鏈路傳輸的這些參數不是用于配置接收器,而是僅用于驗證鏈路參數匹配。若檢測到錯誤,FPGA將通過JESD204B規范的錯誤報告中定義的中斷報告此錯誤。有關鏈路配置參數的更多信息,請參閱本文末尾列出的參考文獻1。

數據鏈路層

數據鏈路層接受并行成幀數據(包含ADC樣本、控制位和結束位),并輸出8B/10B字,后者在物理層中進行串行化且可以加擾。8B/10B方案會增加一些開銷,但能提供直流平衡的輸出數據和內置差錯校驗。數據鏈路層通過鏈路建立過程同步JESD204B鏈路。鏈路建立包括三個不同階段:

1) 代碼組同步(CGS)

2) 初始通道對齊序列(ILAS)

3) 用戶數據

在代碼組同步(CGS)期間,各接收器(FPGA)必須利用時鐘和數據恢復(CDR)技術,在ADC傳來的輸入數據流中找到K28.5字符。一旦在所有鏈路通道上檢測到某一數量的連續K28.5字符,接收器模塊就會解除置位送至發送器模塊在代碼組同步(CGS)期間,各接收器(FPGA)必須利用時鐘和數據恢復(CDR)技術,在ADC傳來的輸入數據流中找到K28.5字符。一旦在所有鏈路通道上檢測到某一數量的連續K28.5字符,接收器模塊就會解除置位送至發送器模塊的SYNC~信號。在JESD204A中,發送模塊捕捉SYNC~信號的變化,經過固定數量的幀時鐘之后,ILAS就會啟動。在JESD204B中,發送模塊捕捉SYNC~信號的變化,并在下一個本地多幀時鐘(LMFC)邊界上啟動ILAS。

ILAS的主要作用是對齊鏈路的所有通道,驗證鏈路參數,以及確定幀和多幀邊界在接收器的輸入數據流中的位置。在ILAS期間,鏈路參數被發送到接收器(FPGA),以決定如何將數據發送到接收器。ILAS由4個或更多多幀組成。各多幀的最后一個字符是多幀對齊字符/A/。第一、第三和第四個多幀以/R/字符開始,以/A/字符結束。對于ADI ADC,其間的數據為斜坡數據。接收器利用各通道的最后一個/A/對齊接收器內各多幀的末尾。

第二個多幀包含/R/和/Q/字符,隨后是鏈路參數。/Q/字符表示之后的數據是鏈路配置參數。如果接收器需要,ILAS可以添加其它多幀。最后一個ILAS多幀的最后一個/A/字符出現后,用戶數據開始。在不需要通道間偏斜管理的系統中,可以旁路ILAS,只要發送器和接收器均支持這種模式。

CGS和ILAS階段完成后,發送器開始送出用戶數據(即來自ADC的樣本)。在這一階段,用戶數據根據發送器(ADC)中定義并轉發到接收器(FPGA)的鏈路參數,以流形式從發送器傳輸到接收器。這就是RF頻譜中被GSPS ADC數字化的所有帶寬傳輸以供處理的地方。接收器模塊處理并監視收到的數據有無錯誤,包括運行差異不正確(8B/10B錯誤)、不在表中(8B/10B錯誤)、意外控制字符、ILAS不正確和通道間偏斜(注意:8B/10B以某種方式來維持運行差異,使得輸出數據處于直流平衡狀態,同時為接收器中的時鐘和數據恢復電路保持充足的輸出躍遷)。如有這其中的任何錯誤,將以兩種方式中的一種向發送器報告:

? SYNC~置位—每個錯誤都需要重新同步(SYNC~拉低)。

? SYNC~報告—如果發生錯誤,SYNC~將變為高電平并持續一個幀時鐘周期。

在初始通道對齊序列期間,數據鏈路層負責使接收器中的通道對齊。/A/字符就是為了對齊接收器中的通道而使用。JESD204 A和B規范要求/A/字符之間至少隔開17個八位字。這樣可以降低系統大偏斜量的影響。在JESD204 A和B系統中,偏斜在下列三個可能的場景中進行了定義:

1) 一個發送器模塊和一個接收器模塊

2) 多個發送器模塊和一個接收器模塊

3) 多個發送器模塊和多個接收器模塊

達到用戶數據階段后,如果需要,通過數據鏈路中的字符替換可以監視并糾正幀和通道對齊。字符替換在幀和多幀邊界處進行。有兩種情況,一是基于幀的字符替換,二是基于多幀的字符替換。在基于幀的字符替換中,若給定通道上某一幀的最后一個字符與上一幀的最后一個字符相同,則發送器將用/F/字符替換該字符。這一做法同樣適用于使能加擾時,上一幀的最后一個字符是0xFC。在基于多幀的字符替換中,若給定通道上某一多幀的最后一個字符與上一幀的最后一個字符相同,則發送器將用/A/字符替換該字符。這種情況下,當使能加擾時,若上一多幀的最后一個字符是0x7C,字符替換也會進行。CGS、ILAS、用戶數據階段以及字符替換的圖解如圖3所示。

在接收器字符替換中,接收器的操作必須與發送器的操作剛好相同。若檢測到/F/字符,它將被上一幀的最后一個字符替代。若檢測到/A/字符,它將被上一多幀的最后一個字符替代。加擾使能時,/F/字符被0xFC替代,/A/字符被0x7C替代。若接收器檢測到兩個連續錯誤,它可以重新對齊通道。然而,當它執行該操作時,數據會被破壞。表1是JESD204所有控制字符的簡單列表。有關控制字符的更多信息,請參閱參考文獻3。

表1. JESD204控制字符

?

?

?

圖3. 數據鏈路層—ILAS、CGS、數據序列

可以選擇加擾數據,但必須注意:加擾要等到ILAS完成后出現第一個八位字之后才會開始。這意味著CGS和ILAS不會加擾。實施加擾可以降低發送器與接收器之間的高速串行通道上的頻譜峰值輻射。在某些系統設計中,特定數據模式可能會導致產生對給定系統工作頻率不利的頻譜,實施加擾可以解決這一問題。加擾模塊利用一個自同步的加擾模式,其具有如下多項式:1 + x14 + x15(框圖見圖4)。數據在8B/10B編碼器之前進行加擾,解碼后在接收器中進行解擾。由于加擾模式是自同步的,因此輸入和輸出端的兩個移位寄存器不得具有相同的初始設置,否則加擾功能會不起作用。解擾器總是在兩個八位字數據之后跟上步伐并與加擾器自動同步。不是所有系統都需要加擾數據,因此,該層應有能力旁路加擾功能。

?

圖4. JESD204B加擾/解擾

物理層

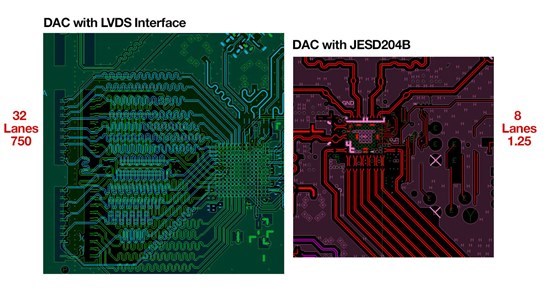

在物理層中,數據進行串行化,8B/10B編碼數據以線路速率發送和接收。物理層包括串行/解串器(SERDES)模塊、驅動器、接收器和CDR。由于數據傳輸速率非常高,這些模塊常常采用定制單元設計。JESD204和JESD204A均支持最高3.125 Gbps的速度。JESD204B規范支持三種可能的速度等級。速度等級1支持最高3.125 Gbps的速度,基于OIF-SxI5-0.10規范。速度等級2支持最高6.375 Gbps的速度,基于CEI-6G-SR規范。速度等級3支持最高12.5 Gbps的速度,基于CEI-11G-SR規范。表2概要顯示了三種速度等級對應的一些物理層規格。

表2. JESD204B物理層規范

?

?

表2列出了各種速度等級的JESD204B標準物理層信號的線路速率、差分電壓、上升/下降時間和總抖動。速度等級越高,信號幅度越小,保持高壓擺率就越容易,因而能夠維持開數據眼以正確傳輸信號。這些高速信號具有快速上升沿和下降沿,對電路板設計的約束非常嚴格。對于許多寬帶RF系統設計者來說,這不是新鮮事。然而,高速數字設計的一個重要區別是寬帶寬。典型RF系統的信號帶寬約為RF工作頻率的10%或以下。對于這些高速串行通道速率,系統設計需要考慮的帶寬通常為通道速率的3倍至5倍。通道速率為5 Gbps時,信號帶寬將是7.5 GHz到12.5GHz。對于如此寬的帶寬,保持適當的信號完整度并且了解如何衡量信號完整度是很重要的。

在串行差分接口中,眼圖是信號完整度的常用測量方法。圖5顯示了以最高3.125 Gbps的速度工作時JESD204發送器的眼圖罩。表3提供了有關時序、電壓電平、阻抗和回波損耗的詳細信息。信號不得侵占圖中的米色區域,必須始終處于白色區域中。表中給出了發送器必須滿足眼罩的條件。對于JESD204B規范中的另外兩種速度等級,也有類似的眼圖罩。詳情請參閱CEI-6G-SR和CEI-11G-SR物理層規范。有關眼圖罩的更多信息,請參閱參考文獻2,其中說明了物理層測量。

表3. 眼圖測量

?

?

?

圖5. Tx眼圖罩示例

結語

采用JESD204B的設計數量與日俱增,并且涉及諸多市場,例如通信、儀器儀表、軍工和航空航天。這些市場推動寬帶RF系統設計使用GSPS ADC,因而需要JESD204B串行接口。收發器支持JESD204B串行化/解串的FPGA越來越多,而且越來越便宜。隨著JESD204B接口變得越來越受歡迎,了解JESD204B規范的各層是很重要的。如上所述,規范中的各層都有自己的功能要完成。配置和數據映射是應用層的功能,而轉換樣本與未加擾八位字之間的映射是在傳輸層完成。加擾可以選擇性使能,以通過延展頻譜尖峰來降低EMI影響。在數據鏈路層,可選加擾的八位字編碼為8B/10B字符,控制字符的產生或檢測也在這里完成,以便支持通道對齊監控和維護。驅動器、接收器、時鐘和數據恢復電路構成發送和接收數據的物理層。通過本文,系統設計者應當能夠更好地了解JESD204B規范的各層,從而在下一個設計中更加有準備地實施JESD204B。

電子發燒友App

電子發燒友App

評論